# 303133 Hardware Software

Anwender-Handbuch

# **Z80-ECB-Serie**

# Hardware Software

**Anwender-Handbuch**

# Z80-ECB ANWENDER-HANDBUCH

# INHALT

# I. Übersicht

- 1. Zilog-Baugruppen

- 1.1. Einführung

- 1.2. Obersicht über die Z80-Platinensysteme

# II. Hardware-Teil

- 1. Obersicht über das Z80-ECB-System

- 2. Die Zentralbaugruppe Z80-ECB/C •

- 2.1. Schaltungsbeschreibung

- 2.1.1. CPU mit Pufferung

- 2.1.2. Takt

- 2.1.3. Programmspeicher

- 2.1.4. Schreib/Lese-Speicher

- 2.1.5. Parallel-Ein/Ausgabe

- 2.1.6. Serien-Schnittstelle

- 2.1.7. Hinweise zur Interrupt-Behandlung

- 2.2. Adressenbelegung

- 2.2.1. Speicher

- 2.2.2. Ein/Ausgabe

- 2.3. Pin-Belegung

- 2.3.1. Ein/Ausgabe-Stecker der ECB/C

- 2.3.2. Bus-Stecker

- 3. Die Erweiterungsbaugruppe Z80-ECB/E \*

- 3.1. Schaltungsbeschreibung

- 3.1.1. Pufferung und Decodierung

- 3.1.2. Programmspeicher

- 3.1.3. Schreib/Lesespeicher

- 4. Die Ein/Ausgabebaugruppen Z80-ECB/I 4

- 5. Schreib/Lese-Speicher-Erweiterungsbaugruppen Z80-ECB/D &

- 6. Schreib/Lese-Speicher-Erweiterungsbaugruppen (nichtflüchtig) Z80-ECB/V

- 7. Ein/Ausgabe-Baugruppe für allgemeine Aufgaben und Floppy-Disk-Ansteuerungen Z80-ECB/F

| 8. | Einschubreck | mit | Rückwandverdrahtung | Z80-ECB/R |

|----|--------------|-----|---------------------|-----------|

|----|--------------|-----|---------------------|-----------|

9. Inbetriebnahme

# III. Softwareteil

| 1.     | Monitorprogramme ECB/12 und ECB/1      |

|--------|----------------------------------------|

| 1.1.   | Einführung                             |

| 1.2.   | Hardware-Erfordernisse des Monitors    |

| 1.2.1. | Speicherorganisation                   |

| 1.2.2. | Anschluß eines Bedienungs-Terminals    |

| 1.3.   | Beschreibung des Monitor-Programms     |

| 1.3.1. | Verhältnis zu evtl. Anwenderprogrammen |

| 1.3.2. | Formale Regeln                         |

| 1.3.3. | Beschreibung der einzelnen Kommandos   |

| 1.3.4. | Haltepunkt-Behandlung                  |

| 2.     | Monitorprogramm ECB/3                  |

| 3.     | Fchtzeithetriehssystem 780-MTX         |

Ausgabe 3, April 1978

Copyright by:

GESCHÄFTSBEREICH MIKROCOMPUTER

Breslauer Str. 2 8057 Eching Tel. 089/3188-1 Telex 0522122

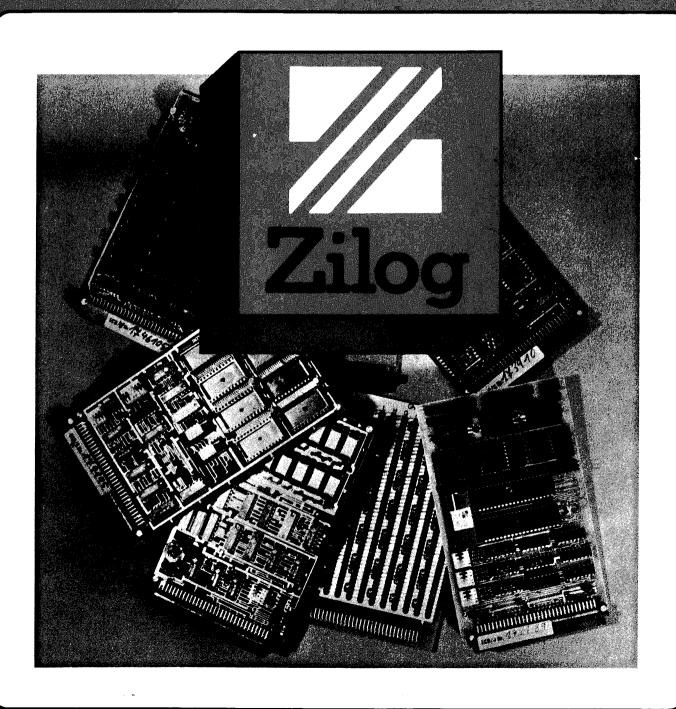

# 1. Zilog-Z80-Mikrocomputer-Baugruppen

# 1. Einführung

Die weitest verbreitete Anwendung von Mikrocomputern besteht darin, Geräte, Maschinen, Prozesse usw. mit "technischer Intelligenz" auszurüsten, d.h. in ihnen Programmierbarkeit, Entscheidungsfähigkeit, Rechner-Funktionen und Mensch/Maschine-Dialogfähigkeit zu implementieren.

Dies ist beim heutigen Stand der MOS-Technik zu Preisen möglich, die in den meisten Fällen weit unter technisch gleichwertigen Lösungen mit herkömmlichen oder kundenspezifischen Schaltkreisen liegen.

Um nun dem breiten Kreis von Anwendern diesen Schritt von konventioneller Technik zu Mikrocomputern zu erleichtern und dabei Entwicklungszeit und -kosten möglichst niedrig zu halten, wurden die Z80-Mikrocomputer-Baugruppensysteme entwickelt; in jedem Fall steht standardisierte Hardware (also Baugruppen und Baugruppenträger) zur Verfügung, die gemäß der weitverbreitetsten Normen realisiert wurde, und die zugehörige Grundsoftware (= ,,Monitoren") zur Inbetriebnahme dieser Baugruppen. Daher beschränkt sich bei Verwendung der Z80-Baugruppen der gesamte Anlagen-Entwicklungsaufwand in den meisten Fällen auf die Erstellung der Anwender-Software und einer häufig trivialen peripheren Anpassungsschaltung.

Bei der Konzeption dieser Baugruppen wurde von folgenden Voraussetzungen ausgegangen:

- die Leistungsfähigkeit der Z80-Bausteine ist so hoch und die Speicherersparnis gegenüber bisherigen Mikrocomputern so weitreichend, daß viele Aufgaben bereits mit einer einzigen Steckkarte zu lösen sind. Jedes der Z80-Baugruppensysteme beinhaltet deswegen einen autonomen 1 Platinen-Computer.

- da das System Z80 andererseits hervorragend zur Lösung sehr komplexer Anwenderprobleme geeignet ist, wurde diese autonome Computerkarte grundsätzlich so ausgelegt, daß ein kompromißloser Ausbau auf die volle Erweiterbarkeit der Z80 ohne spezielle Hardwaremaßnahmen möglich ist.

- die Aufteilung der einzelnen Bausteine auf die Baugruppe (="Partitioning") wurde dem hohen Integrationsgrad der Z80-Bausteine angemessen vorgenommen, so daß bei der Verwendung dieser Standardbaugruppen praktisch in keinem Fall ungenützte Hardware übrigbleibt (="Hardware-Overkill").

- durch den großen Fortschritt in der Floppy-Disk-Technologie und die stark sinkenden Preise der Floppy- Disks einerseits und durch die hohe Verarbeitungsgeschwindigkeit der Z80-CPU andererseits wird es in vielen Fällen interessant und wirtschaftlich, Floppy Disks im Anwendersystem einzusetzen. Aus diesem Grund beinhalten die Z80-Baugruppensysteme komplette FD-Ansteuerungseinheiten

- Ebenfalls mit dem Ziel, auch komplexe Anwendersysteme realisieren zu helfen, werden Baugruppen mit dynamischen RAM-Bausteinen angeboten.

- Da sämtliche Z80-Bausteine mit einer einzigen 5V-Speisespannung auskommen, wurden auch alle Baugruppen so ausgelegt, daß keine zusätzlichen Speisespannungen erforderlich sind.

Lediglich bei der Verwendung von 2708-EPROM's geht dieser Vorteil verloren; hier müssen externe + 12 V und — 5V-Versorgungsspannungen zugeführt werden.

# 2. Übersicht über die Z80-Platinensysteme

Das System Z80 umfaßt 3 verschiedene Platinensysteme, die aus den Baugruppen, Zubehör und der zugehörigen Standardsoftware bestehen.

Durch die Verfügbarkeit von Platinen unterschiedlicher Abmessungen ist gewährleistet, daß die Einsatzmöglichkeit kostensparender Z80-Standard-Hardware nicht durch mechanische Restriktionen (wie vorgegebene Einbaumaße) eingeschränkt wird:

- Das Baugruppensystem mit dem Z80-MCB als Zentralbaugruppe im amerikanischen Format 7,5" × 7,7".

- Das Baugruppensystem mit dem Z80-MCB/E als Zentralbaugruppe im Doppeleuropaformat (233×160 mm) mit 64-poligen VG-Steckern, das mit den 7,5"×7,7"-Platinen schaltungsmäßig identisch ist und

- das Baugruppensystem mit dem Z80-ECB/C als Zentralbaugruppe im Einzel-Europa-Format (100 × 160 mm) mit einem 64-poligen VG-Stecker.

Sämtliche Platinensysteme umfassen eine autonome voll erweitbare 1-Platinen-Computerkarte und zusätzlich Ein/Ausgabe-, Speichererweiterungs-, dynamische RAM-, Floppy-Disk-Controller- und Stromversorgungs-Module.

Die Entscheidung, welchem der 3 Formate der Vorzug zu geben ist, hängt von der Einzelsituation des Anwenders ab: ob bei ihm bereits ein Format eingeführt ist und welches Partitioning (also welche Aufteilung der Bestückung auf die Baugruppen) für seine Aktivitäten die günstigere ist.

Die einzelnen Systeme umfassen folgende Baugruppen:

| <ul><li>O</li></ul> | EM-Computer im Format $7,7'' \times 7,5''$               |

|---------------------|----------------------------------------------------------|

|                     | ☐ Ein-Platinen-Computer                                  |

|                     | ☐ Schreib/Lese-Speichererweiterung                       |

|                     | ☐ Festwertspeicher-Erweiterung                           |

|                     | ☐ Parallele Ein/Ausgabe-Baugruppe                        |

|                     | ☐ Serien-Ein/Ausgaben-Baugruppe                          |

|                     | ☐ Floppy-Disk-Controller                                 |

|                     | ☐ Video-Board                                            |

|                     | ☐ PROM-Programmierboard                                  |

|                     | ☐ AD/DA-Wandler                                          |

|                     | ☐ Einschub-Rahmen                                        |

|                     |                                                          |

| • 0                 | EM-Computer im Doppel-Europa-Format                      |

|                     | ☐ Ein-Platinen-Computer                                  |

|                     | ☐ Schreib/Lese-Speichererweiterung                       |

|                     | ☐ Floppy-Disk-Controller                                 |

|                     | 1 Troppy Disk Controller                                 |

| • 0                 | EM-Computer im Einzel-Europa-Format                      |

| • •                 | ☐ Ein-Platinen-Computer                                  |

|                     | ☐ Festwertspeicher-Erweiterung                           |

|                     | ☐ Dynamische Schreib/Lesespeicher-Erweiterung            |

|                     | ☐ Ein/Ausgabe-Baugruppe                                  |

|                     | ☐ Stromausfallsichere Schreib/Lese-Speicher-             |

|                     | Baugruppe                                                |

|                     | ☐ Floppy-Disk-Controller                                 |

|                     | ☐ Einschub-Rahmen                                        |

|                     |                                                          |

| A E                 | Section to point a residenter Grundsoftware wird für ind |

An Festwertspeicher-residenter Grundsoftware wird für jedes der 3 Systeme angeboten

| 1/2 kByte-Monitor tu | r Spe  | icherzugriff und Daten  |

|----------------------|--------|-------------------------|

| verkehr über die Ser | ienscl | hnittstelle             |

| 1 kByte-Monitor mit  | zusä   | tzlichen Testmöglichkei |

| ten (Haltepunkten    | und    | CPU-Registrierinhalts   |

| Ausgabe)             |        | -                       |

☐ 3 kByte-Monitor mit zusätzlicher Floppy-Disk-Grundsoftware

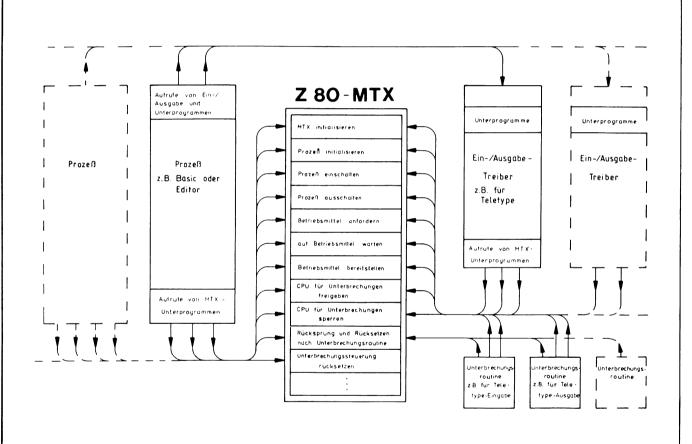

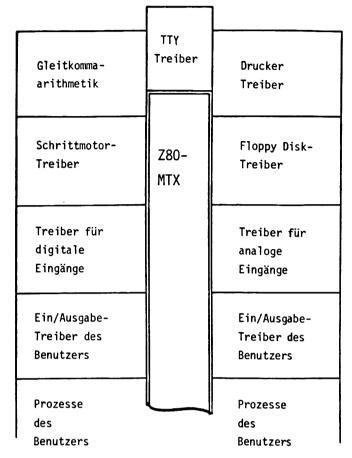

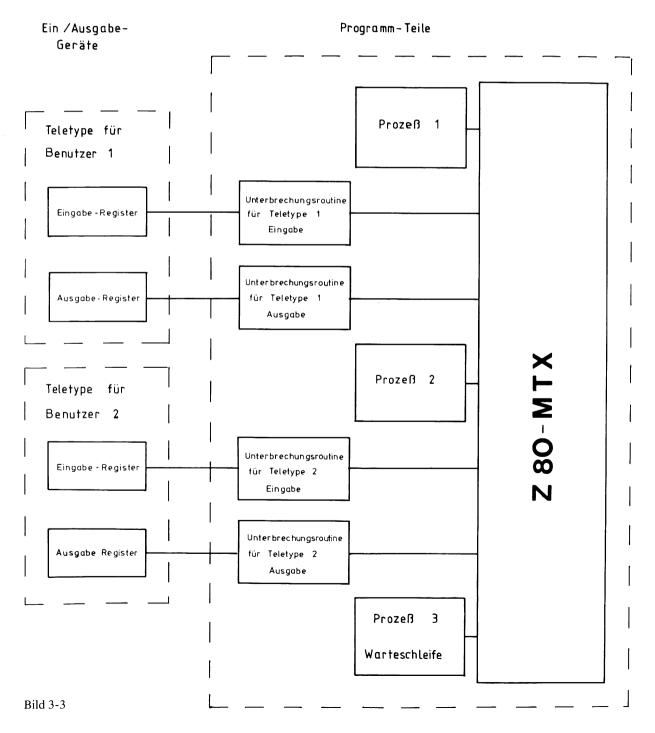

Für die ECB-Familie ist darüberhinaus ein Multi-Task-Echtzeitbetriebssystem verfügbar.

# **ECB-HARDWARE**

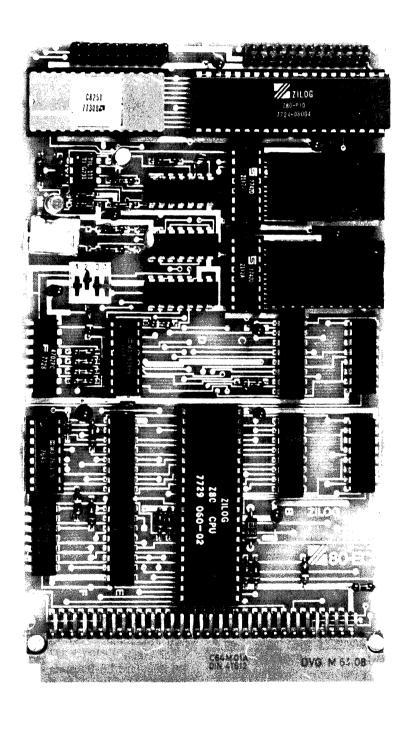

### 1. Übersicht über das ECB-System

In diesem Handbuch werden die Grundbaugruppen des ECB-Systems beschrieben:

Z80-ECB/C Computerplatine für Stand-Alone-Betrieb.

erweiterbar auf vollen Z80-Speicher und

I/O-Bereich

Z80-ECB/E Erweiterungsplatine mit max. 8 kByte Fest-

wertspeicher und 1 kByte statischem

Schreib/Lesespeicher

Z80-ECB/I I/O-Platine mit 4 Byte-paralleler Ein/Ausgabe, Quittungs-(,,Handshaking")-Logik,

4 Zähler/Zeitgeber-Kanälen und Wire wrap Feld für anwenderspezifische Interface-

schaltungen.

Z80-ECB/D8 Schreib/Lese-Speichererweiterung um

8 kByte dynamisches RAM (mit 4 kbit-

Bausteinen aufgebaut)

Z80-ECB/D16 Schreib/Lese-Speichererweiterung um

16 kByte dynamisches RAM, (mit 16 kbit-Bausteinen aufgebaut) auf 32 kByte aus-

baufähig.

$Z80\text{-}ECB/D32 \quad Schreib/Lese\text{-}Speichererweiterung \quad um \quad 32$

kByte dynamisches RAM (mit 16 kbit-Bau-

steinen aufgebaut)

Z80-ECB/V Schreib/Lese-Speichererweiterung um

4 kByte CMOS-RAM. Dieser Speicher ist durch einen auf der Platine untergebrachten

Puffer-Akku nichtflüchtig.

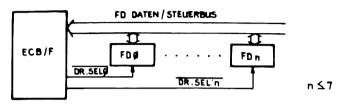

Z80-ECB/F Floppy-Disk-Controller und allgemeine

Ein/Ausgabebaugruppe mit 20 Bit paralleler Ein/Ausgabe, 2 Serien-Duplex-Ein/Ausgabekanälen (SI0, HDLC- und SDLCfähig z.B. für Rechner/Rechner-Kopplun-

gen) und 4 Zähler/Zeitgeber-Kanälen.

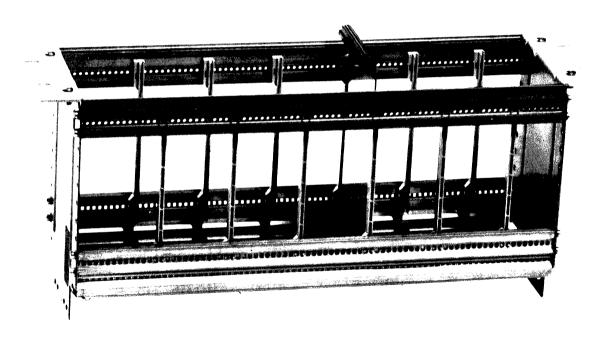

Z80-ECB/R 19 Zoll-Einschubreck mit Rückwandver-

drahtung für bis zu 20 ECB-Baugruppen

(6 Steckplätze sind bestückt).

Z80-ECB/R6 Nachrüstsatz für Z80-ECB/R zur Nachbe-

stückung von weiteren 6 Steckplätzen des

ECB/R.

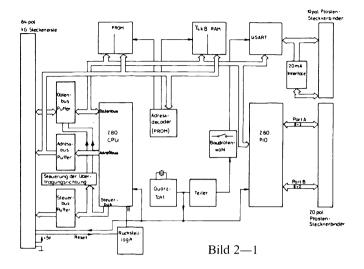

Das Z80-ECB-Grundkonzept ersehen Sie aus Bild 1—1.

Sämtliche Bus-Signale wurden so auf die 64-poligen Standard VG-Stecker herausgeführt, daß alle Baugruppen untereinander über "1:1-Verdrahtung" verbunden werden, d.h. daß immer gleiche Steckerpins (ohne Kreuzungen) miteinander verdrahtet sind, wodurch sich eine problemlose Rückwandverdrahtung ergibt.

Die Zentralbaugruppe Z80-ECB/C wurde aus folgenden Gründen bereits mit Speicher- und Ein/Ausgabemöglichkeiten ausgerüstet:

einfachere Anwenderprobleme können bereits mit dieser Konfiguration oder mit geringfügiger Erweiterung gelöst werden.

□ eine Serienschnittstelle ist in den meisten Anwendersystemen nur einmal erforderlich; sie wurde daher auf der Zentralplatine untergebracht.

□ kleine Systeme kommen bereits mit den auf der Z80-ECB/C vorhandenen zwei 8bit-Ports aus, da diese bereits die gesamte Quittungs- und Interruptsteuerungs-Logik implizieren.

In größeren Systemen werden dagegen häufig einige wenige parallele Hilfs-Ein/Ausgaben (z.B. für Anzeigen oder Status-Informationen) benötigt, für die die ECB/C-PIO verwendet werden kann.

□ Das 1 kByte PROM der Z80-ECB/C wurde bewußt fest durch Programmierung eines Address Decode PROM's auf die Anfangsadresse 0 gelegt (variabel durch Austausch dieses PROM's), da man hier sinnvollerweise die Grundfirmware (= "Monitor") oder aber Programme für Tests und Wartung bzw. zur Interrupt-Behandlung ablegt: die Platine wird mit Sockeln ohne PROM-Bausteine geliefert, da nicht festgelegt ist, ob Monitor- oder Anwenderfirmware verwendet werden soll.

☐ Die 256 Bytes statischen RAM's auf der Platine sind als Zwischenspeicher oder Stack einzusetzen.

☐ Durch Herausführen der Signale BUSRQ und BUSAK ist der Aufbau von Multiprozessorsystemen und direkter Speicherzugriff (DMA) möglich.

☐ Speichererweiterungen werden mit im Verhältnis 8:1 gemischten Festwert/Schreib/Lese-Speicher-Baugruppen durchgeführt, da erfahrungsgemäß bei wachsender Programmgröße auch der Bedarf an Variablen-Speicher proportional wächst. Zum Aufbau des Festwertspeichers können alle Standard-Masken-ROM's "fusible" PROM's oder EPROM's eingesetzt werden, deren Pinbelegung den Bausteinen HM 7641 (fusible PROM) oder 2708 (EPROM) entspricht und die den Geschwindigkeitsanforderungen der Z80-CPU genügen. Aus diesem Grund wird die Z80-ECB/E-Baugruppe auch lediglich mit Sockeln, nicht aber mit Festwert-Speicher-Bausteinen geliefert, um dem Anwender freie Wahl der Bausteine zu ermöglichen. Beide Speicherbereiche können über DIL-Schalter jedem beliebigen adressierbaren Speicherbereich der Z80-CPU zugeordnet werden. Für Systeme, in denen auch die Anwenderprogramme in Schreib/ Lesespeichern abgelegt werden sollen (z.B. bei den meisten Anwender-Systemen, die mit Floppy Disks und der Steuerplatine ECB/F arbeiten), stehen reine RAM-Karten (8, 16 oder 32 kByte dynamisches RAM ECB/D und 4 kByte-CMOS statisches RAM mit Puffer-Batterie und Speicherschutzschalter Z80-ECB/V) zur Verfügung. Zur Erweiterung der Ein/Ausgabe-Möglichkeiten der Zentralplatine dient die Z80-ECB/I mit ihren vier 8bit-Ports und vier Zähler/Zeitgeber-Kanälen inklusive kompletter Ouittungs- (= "Handshaking") und Interrupt-Steuerungslogik. Zusätzliche Ergänzung ECB-basierender Systeme ist über die Serien/Parallel/Echtzeit-, Ein/Ausgabe und Floppy-Disk-Platine ECB/F sowie über die Baugruppen aus dem Z80-KIT-Konzept und Sonderbaugruppen möglich.

☐ Als Bus-Stecker kommt die weitverbreitete 64-polige VG-Steckerleiste zum Einsatz.

Hier werden sämtliche Signale herausgeführt, die allen Baugruppen gemeinsam sind und einfach durchverdrahtet werden können.

☐ Ein/Ausgabe-Signale werden von der Karte an dem dem Bus-Stecker entgegengesetzten Kartenende über 3M-Pfostensteckverbinder verfügbar gemacht, da

Ein/Ausgabe-Signale bei sehr vielen Anwendungen an der Frontseite (üblicherweise der "Rückwandverdrahtung" gegenüberliegend) benötigt werden.

auch bei aufwendigerer, den Ein/Ausgabebausteinen nachgeschalteter Peripheriehardware eine Rückführung dieser Signale über eine zweite, kundenspezifische Interface-Baugruppe möglich ist (auch "Huckepack"bzw. "Sandwich"-Verfahren erwägen!!)

• die Herausführung sämtlicher Signale, also auch der Ein/Ausgabe, auf der Busseite die Verwendung vielpoliger teurer Steckverbinder nötig machen und die komplizierte Leitungsführung auf der Baugruppe zu großem Platzverlust verursachen würde. Um dem Anwender Zeitverlust durch Aufbau- und Verdrahtungsprobleme zu ersparen, wird übrigens passend zu diesem System ein Baugruppenträger (Z80-ECB/R) angeboten.

# Sämtliche Erweiterungs-Baugruppen der ECB-Serie 3M- Stecker für USART PIQ (10) (20) Z80 - ECB / Z80 - ECB VG-Stecker (64) VG-Stecker (64) Steuerbus Adresbus

Bild 1—1: Z80-ECB-Grundkonzept.

# 2. Die Zentralbaugruppe Z80-ECB/C

# 2.1 Schaltungsbeschreibung

Die Baugruppe umfaßt folgende Funktionseinheiten

- Z80-CPU

- Decoder und Puffer für vollen Speicher-(64 kByte) und I/O-Ausbau (256 Ports)

- Platz f

ür 2 kByte PROM

- 256 Byte RAM

- 2 Parallelschnittstellen (1 Stück Z80-PIO)

- 1 Serienschnittstelle mit RS 232 und 20 mA Stromschleifen-Interfaces

- Über Schalter 14 Baud-Raten einstellbar

- Busseitiger 64-poliger Stecker nach DIN 41612 (VG 95324)

- I/O-seitig 3M-WWP-Pfostensteckverbinder

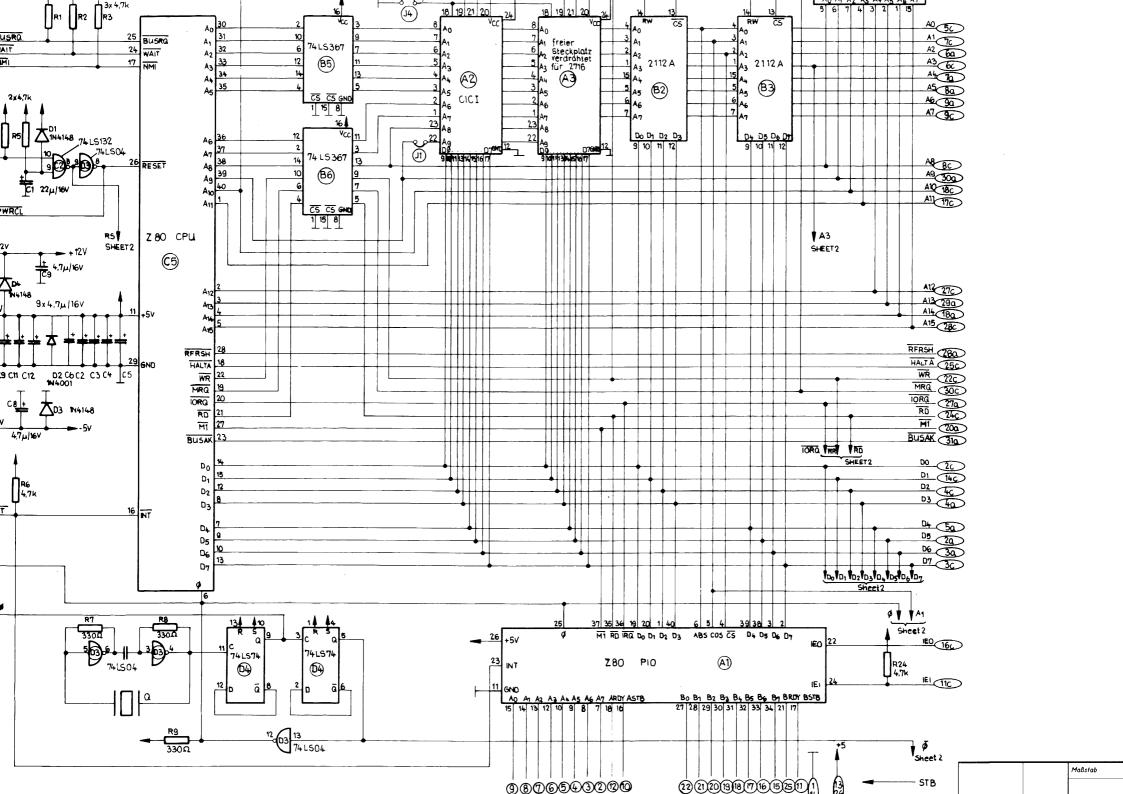

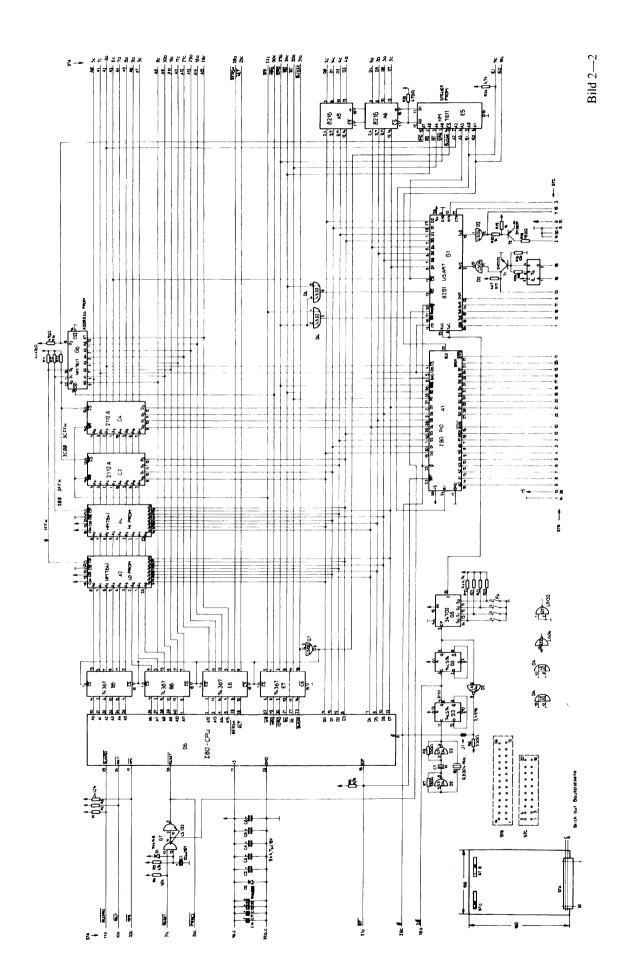

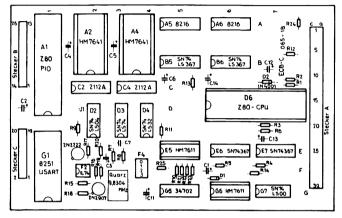

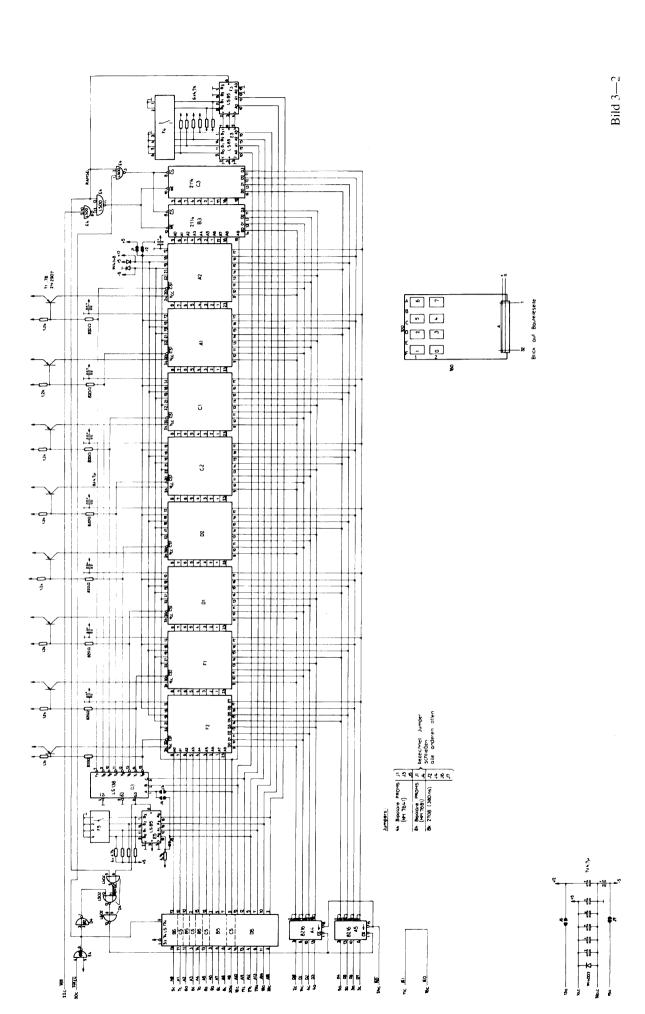

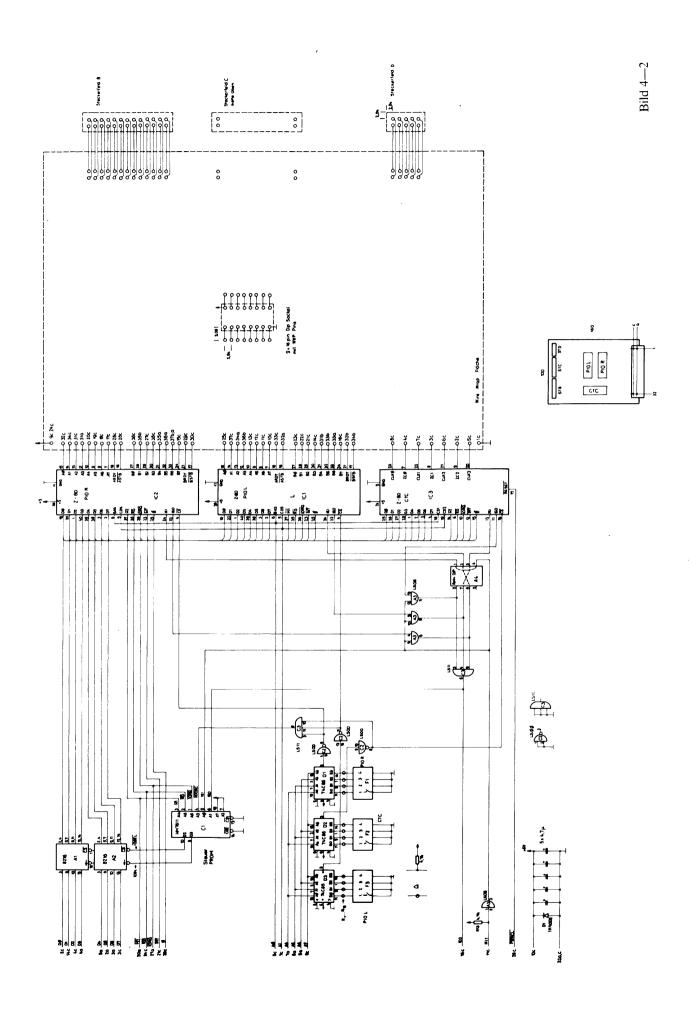

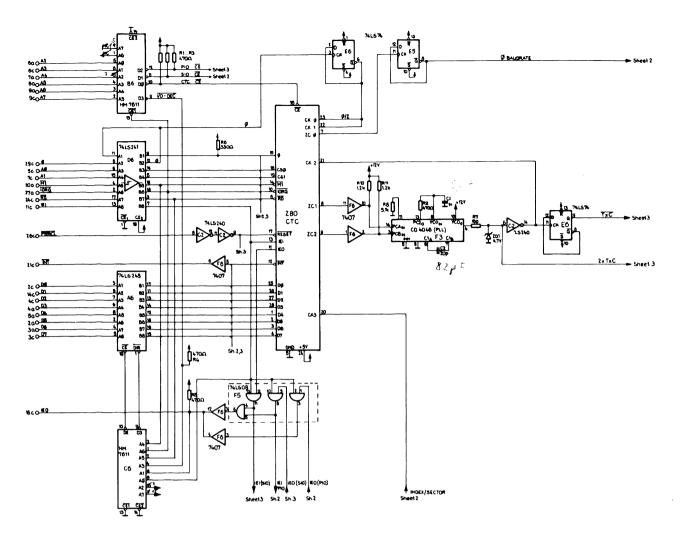

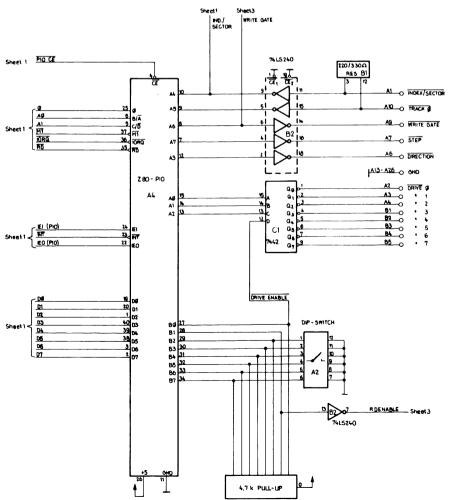

Aus der Blockschaltung (Bild 2—1) ist die Verknüpfung der einzelnen Funktionseinheiten zu erkennen; die Busleitungen sind gepuffert. Die Adreßeingänge der auf der Z80-ECB/C untergebrachten Speicherbausteine werden über diese Puffer, die Datenleitungen vom CPU-Datenbus direkt angesprochen. Festwert- und Schreib/Lese-Speicherbereich auf der Platine haben durch den Adreßdecoder vorgegebene Anfangsadressen. Die Baudrate für die Serienschnittstelle wird hardwaremäßig vom Quarz-Systemtakt abgeleitet. Bild 2—2 zeigt die Schaltung im Detail, die in folgenden noch im Einzelnen erläutert wird.

## 2.1.1 CPU mit Pufferung

Sämtliche Z80-CPU-Signale (siehe Z80-Datenbuch und Z80-CPU-Technical-Manual) bis auf die Signale BUSRO, WAIT, INT und NMI sind gepuffert.

Das Rückstellen der Z80-CPU kann über die zwei Standardgatter sowohl durch Aus/Einschalten der Stromversorgung als auch elektronisch oder elektromechanisch über den Eingang RESET (1 Low-Power-Schottky-Eingangslast) erfolgen. Zur Erhöhung der Störsicherheit und Erreichung voller Speicher-Ausbaufähigkeit wurde im System Z80-ECB eine doppelte Pufferung sämtlicher Busleitungen vorgenommen. Für die bidirektionalen Datenpuffer muß je 1 Steuersignal zur Bausteinaktivierung und zur Festlegung der Datenübertragungsrichtung erzeugt werden (s. Z80-Applikationsschrift über Ein/Ausgabeschaltungen und Pufferung in Z80-Systemen). Diese Steuersignale hängen ihrerseits von folgenden Signalen ab:

a) INTERNAL MEM DECODE (IMD) ist aktiv, wenn der auf der Zentralplatine aufgebaute Speicherbereich angesprochen ist.

- b) I/O-REQUEST (IORQ) ist aktiv, wenn eine Daten-Ein-Ausgabe eingeleitet wird.

- READ: Lesesignal  $(\overline{RD})$

- d) M1: definiert den Maschinenzyklus 1 (= "Fetch-Zyklus")

- e) INTERNAL I/O-DECODE (IIODEC) ist aktiv, sobald Ein/Ausgabebausteine auf der Zentralplatine ECB/C angesprochen sind.

- INTERNAL INTERRUPT ENABLE IN (IIEI) Interrupt-Freigabe-Eingang für Ein/Ausgabe-Bausteine auf der ECB/C

- g) INTERNAL INTERRUPT ENABLE OUT (IIEO) Interrupt-Freigabe-Ausgang von Ein/Ausgabe-Bausteinen auf der ECB/C

Die genannten Signale verknüpft man nun zur Erzeugung der beiden Datenbus-Steuersignale sinnvollerweise mit einem PROM (vgl. Bild 2—3).

Die logischen Gleichungen hierzu lauten wie folgt:

CPUIN =

$$(IMD \land R\overline{D})$$

$\lor$   $(\overline{IORQ} \land \overline{M1})$   $\lor$  EXT MEM READ INTA

$$\lor (\overline{IORQ} \land IIODEC \land \overline{RD})$$

EXT IO READ

$$\overline{\text{CS}} = (\overline{\text{IORQ}} \wedge \overline{\text{M1}} \wedge \text{IIEI} \wedge \text{II EO}) \vee$$

$$\overline{\text{EXT INTA}}$$

$$\overline{\text{IORQ}} \vee \overline{\text{II ODEC}}$$

$$\overline{\text{EXT MEM TRANS}}$$

Dabei sind:

CPUIN: Richtungssteuersignal (High: Richtung zur CPU)

CS: Aktivierungsignal (High: Puffer gesperrt)

M1: Maschinenzyklus 1 **IORO**: I/O Request

**HODEC:** ECB/C Internal I/O Anforderung

RD:

IIEO: ECB/C- Internal Interrupt Enable Out ECB/C Internal Interrupt Enable In IIEI: **IMD**: ECB/C- Intern Speicheranforderung

Dadurch wird der 1 KByte-Festwertspeicher auf der Z80-ECB/C in den Adreßbereich

0 0 0 0 H bis 0 3 F F H

und der 1/4 kByte Schreib/Lesespeicher in den Adreßbereich

3 C 0 0 H bis 3 C F F H

gelegt.

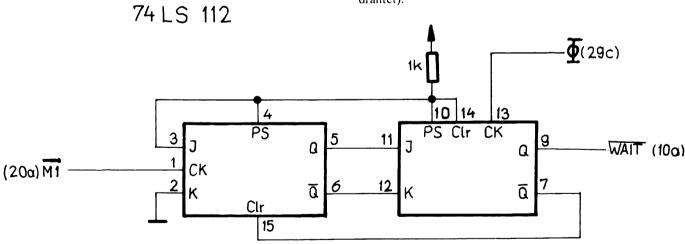

# 2.1.2 Takt

Aus Stabilitäts- und Kostengründen wird der Systemtakt über einen 9,8304 MHz-Quarz erzeugt, der zusammen mit 1/3 Standard LS-Baustein einen Oszillator bildet. Der für die Z80-CPU nötige Takt  $\Phi$  von 2,4576 MHz wird über einen D-FlipFlop-Teiler: 4 (2 × ½ 74LS74) gewonnen, von dem auch das 2 Φ-Signal abgeleitet und auf den Bus herausgeführt wird, das häufig in dynamischen RAM-Speichersystemen benötigt wird (siehe entsprechende Applikationsschriften!). Die für die Serienschnittstelle erforderliche Bezugsfrequenz erzeugt der den D-Flip-Flops nachgeschaltete programmierbare Teilerbaustein 34702, an dessen Eingängen So...S3 4 DIL-Schalter zur Festlegung der gewünschten Datenübertragungsrate angeschlossen sind.

Inhalt der PROM's (Datenbussteuerung und Adreßcodierung)

a) PROM HM 7611 zur Datenbussteuerung

D 0 = CS

active low für ECB/C

D 1 = CPU IN

D 2 = IOSEL

D S = IO IN

active high für ECB/I

active high für ECB/I

| Adresse | ı | ı | ı | 1 | ı | ı | ı | ı | ı | ı              | ı              | ı | ı | ı | ı | i |

|---------|---|---|---|---|---|---|---|---|---|----------------|----------------|---|---|---|---|---|

| (hex)   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9              | Α              | В | C | D | Ε | F |

| 000     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 001     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 002     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 003     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 004     | 8 | 8 | 8 | 8 | 8 | 8 | 8 | 8 | 8 | 8              | 8              | 8 | 8 | 8 | 8 | 8 |

| 005     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | 3 | 3 |

| 006     | 3 | 3 | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 007     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 008     | F | F | F | F | F | F | F | F | F | F              | F              | F | F | F | F | F |

| 009     | F | F | F | F | 3 | 3 | 3 | 3 | F | F              | F              | F | Е | E | E | Ε |

| 00A     | Ε | F | E | Ε | Ε | 3 | E | Ε | E | F              | Е              | Ε | Е | 3 | E | E |

| 00B     | F | F | F | F | В | В | В | В | F | F              | F              | F | C | C | C | C |

| 00C     | Α | Α | Α | Α | Α | Α | Α | Α | Α | A              | Α              | Α | Α | Α | Α | Α |

| 00D     | Ε | Е | E | E | Е | Ε | E | Е | E | E              | E              | Е | E | Ε | E | E |

| 00E     | C | C | C | C | C | C | C | C | C | C              | C              | C | C | C | C | C |

| 00F     | C | C | C | C | C | C | C | C | C | $ \mathbf{C} $ | $ \mathbf{C} $ | C | C | C | C | C |

b) PROM HM 7611 zur Adreßdecodierung (standardmäßig ausgelieferter PROM-Inhalt; bei anderer Adreßbelegung ist ein PROM mit anderem Inhalt zu verwenden).

| Adresse (hex) | Inhalt |

|---------------|--------|

| 0             | C      |

| 1             | C      |

| 2             | Α      |

| 3             | Α      |

| 3C            | 6      |

c) PROM HM 7611 zur Adreßdecodierung bei Einsatz von HM 7681- oder i 2758 Programmspeicherbausteinen:

| Adresse (hex) | Inhalt<br>C |

|---------------|-------------|

| 1             | C           |

| 2             | C           |

| 3             | C           |

| 4 5           | Α           |

| 5             | Α           |

| 6             | Α           |

| 7             | Α           |

| 3C            | 6           |

Alle anderen Steuerpromspeicherzellen müssen mit 1111 (F<sub>Hex</sub>) belegt sein!

Dies entspricht einer Speicherorganisation:

0 — 7FFH PROM 3C00H — 3CFFH RAM Die folgende Tabelle zeigt die Beziehung zwischen Schalterstellungen und gewählter Baud-Rate:

| S 1 | <b>S</b> 2 | <b>S</b> 3 | S4  |            |

|-----|------------|------------|-----|------------|

| EIN | EIN        | AUS        | EIN | 50 Baud    |

| EIN | EIN        | AUS        | AUS | 75 Baud    |

| EIN | AUS        | EIN        | EIN | 134,5 Baud |

| EIN | AUS        | EIN        | AUS | 200 Baud   |

| EIN | AUS        | AUS        | EIN | 600 Baud   |

| EIN | AUS        | AUS        | AUS | 2400 Baud  |

| AUS | EIN        | EIN        | EIN | 9600 Baud  |

| AUS | EIN        | EIN        | AUS | 4800 Baud  |

| AUS | EIN        | AUS        | EIN | 1800 Baud  |

| AUS | EIN        | AUS        | AUS | 1200 Baud  |

| AUS | AUS        | EIN        | EIN | 2400 Baud  |

| AUS | AUS        | EIN        | AUS | 300 Baud   |

| AUS | AUS        | AUS        | EIN | 150 Baud   |

| AUS | AUS        | AUS        | AUS | 110 Baud   |

# 2.1.3 Programmspeicher

Der 1 kByte große Festwertspeicher besteht aus 2 "fusible" PROM's HARRIS HM 7641, die 512 × 8 bit organisiert sind; bei Verwendung der 1 k×8-Bipolaren HARRIS-PROM's HM 7681 ergibt sich ein Programmspeicherbereich von 2k Byte. Die Adreßleitung A9 ist in diesem Fall zusätzlich mit Pin 22 beider Fassungen zu verbinden und das Adreßdecode-PROM entsprechend zu modifizieren. Stattdessen sind natürlich auch elektrisch und Pin-kompatible Bausteine anderer Hersteller einsetzbar.

Dieser PROM-Bereich ist in erster Linie zur Unterbringung eines Monitors oder von Wartungs- und Test-Programmen gedacht.

Die Bausteinanwahl (= "Chip-Select") findet durch die höherwertigen 8 Adreßbits statt. Zur Decodierung wurde ein PROM-Baustein HM 7611 verwendet. Dadurch wurde

- ☐ die Anzahl der nötigen Decoder-Bausteine minimiert und gleichzeitig

- ☐ dem Anwender die Möglichkeit gegeben, durch Auswechseln des PROM's die Speicheranfangsadressen in ¼ kByte-Schritten in jeden beliebigen Speicherbereich zu legen (s. auch Pkt. 2.2. "Adressen-Belegung").

# 2.1.4 Schreib/Lese-Speicher

Der 256 Byte große Schreib/Lese-Speicher besteht aus 2 statischen 2112A-RAM-Bausteinen, die 256×4-bitweise organisiert sind.

Sie werden vom gleichen PROM HM 7611 wie der vorher erwähnte Festwertspeicher-Bereich aktiviert und lassen sich durch Auswechseln dieses PROM's in 256-Byte-Schritten in jeden beliebigen Speicherbereich verlagern.

# 2.1.5 Parallel-Ein/Ausgabe

Für den Datenverkehr zwischen Z80-CPU und der "Außenwelt" über parallele Schnittstellen wurde 1 Baustein Z80-PIO auf der Baugruppe Z80-ECB/C untergebracht. Dieser Baustein umfaßt zwei 8bit-Ports, die als Eingabe-Port, Ausgabe-Port, bidirektionales Port oder aber in Einzelbit-Schaltung arbeiten können (Einzelheiten siehe Z80-PIO-Produktspezifikation und Z80-PIO-Technical Manual).

Beide Ports verfügen über eine interne Logik, die ohne zusätzliche Hardware Quittungs-(= "Handshaking")-Betrieb (2 eigene Leitungen pro Port) und priorisierten Vektor-Interrupt ermöglicht. Die die Priorisierung festlegenden Signale IEI (= "Interrupt Enable In") und IEO (= "Interrupt Enable Out") sind zur Verkettung mit weiteren Ein/Ausgabebausteinen busseitig herausgeführt.

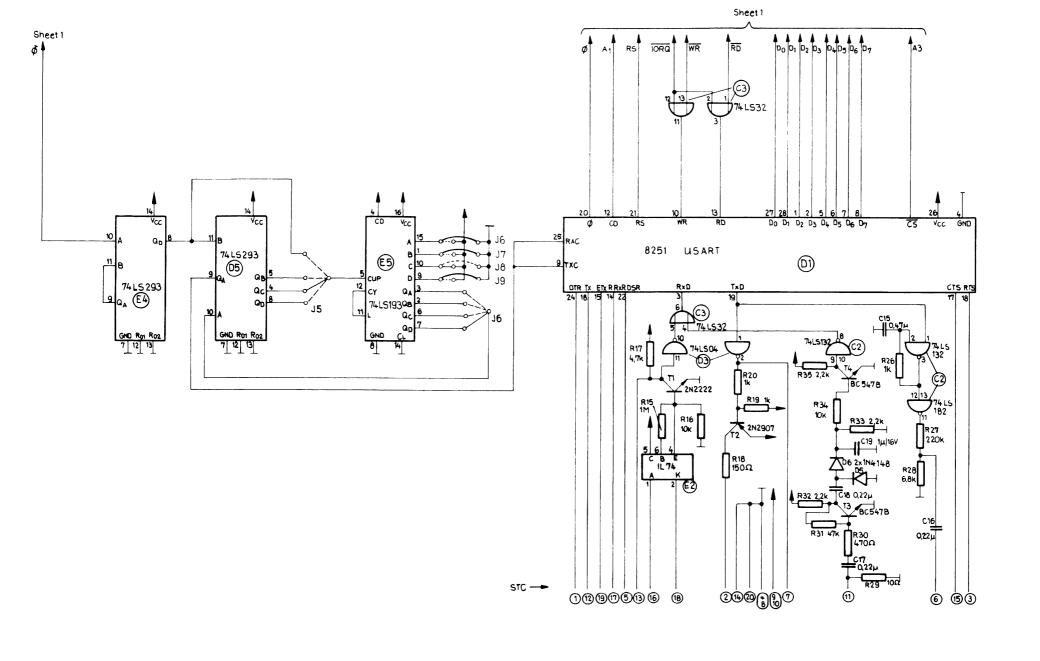

## 2.1.6 Serien-Schnittstelle

Die Serienschnittstelle (1 Duplex-Kanal) ermöglicht den seriellen Datenverkehr zwischen peripherer Elektronik und der Z80-CPU; meist wird man hier Diagnosegeräte für Wartungs- und Testzwecke anschließen.

Bei Verwendung eines Fernschreibers kann die ECB/C zusammen mit den ECB-Monitorprogrammen sogar als einfaches Entwicklungshilfsmittel auf hexadezimaler Basis benützt werden; es ist mit dieser Konfiguration das Einschreiben von Programmen, Lesen von Speicher- und CPU-Register-Inhalten und sogar die Durchführung von Tests über das Setzen von Haltepunkten (= "Breakpoints") möglich.

Die Serienschnittstelle wurde mit einem Standard-USART-Baustein realisiert.

Der USART ist übrigens selbst auch interruptfähig, hat aber nicht die Möglichkeit zur automatischen Interrupt-Vektor-Behandlung, die alle Zilog Z80-Ein/Ausgabe-Bausteine aufweisen. Soll die Serienschnittstelle in Vektor-Interrupt-Betriebsart gefahren werden, müßte deshalb eine zusätzliche Logik zur Interrupt-Vektor-Erzeugung aufgebaut werden. Die Eingangsschaltung der Stromschleifenschnittstelle (TTY-Schnittstelle) besteht aus einem Optokoppler mit nachfolgendem Impedanzwandler und TTL-Puffer. Die Leuchtdiode des Optokopplers kann in zwei verschiedene Arten vom angeschlossenen Terminal angesteuert werden:

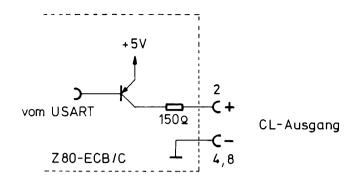

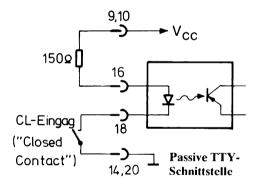

- ☐ Liefert das Terminal den Strom für die Stromschleifenschnittstelle, genügt es, die Leuchtdiode in diesen Stromkreis zu schalten.

- □ Stellt das Terminal nur einen Kontaktschluß zur Verfügung, wie es üblicherweise bei einem Fernschreiber (z. B. Teletype ASR 33) der Fall ist, ist es notwendig, die Anode der Leuchtdiode über einen Widerstand (150 Ohm) auf +5 Volt zu legen und den Kontakt zwischen Leuchtdioden-Kathode und Masse zu legen.

Der Fototransistor auf der Ausgangsseite des Optokopplers ist als Emitterfolger geschaltet, der einen weiteren Transistor schaltet. Die Basis des Fototransistors ist hochohmig mit dem Emitter verbunden, so daß der Fototransistor beim Ein- und Ausschalten an seinen Anschlüssen keine große Spannungsdifferenzen auszugleichen hat. Dadurch wird der Einfluß interner Transistorkapazitäten ausgeglichen und eine stabile Datenübertragung selbst bei hohen Baudraten gewährleistet.

Der dem Treibertransistor folgende TTL-Puffer 74LS04 ist zusätzlich auf den Pfostensteckverbinder der Serienschnittstelle zur Realisierung einer Spannungsschnittstelle entsprechend RS 232 herausgeführt, wobei allerdings die Normpegel nicht im vollen Umfang eingehalten werden. Dies hat jedoch für Datenübertragungen auf Strecken < 20 m praktisch keine Bedeutung.

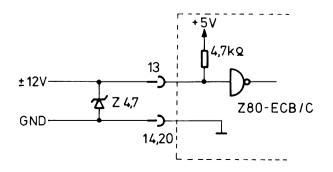

**Zur besonderen Beachtung:** Bei Anschluß eines RS 232/V 24 SENDERS mit vollem Spannungshub an die Serienschnittstelle der ECB/C muß eine Zener Diode 4.7V als Schutz parallel zum Eingang geschaltet werden.

Analog ist auch der Senderausgang des USART 8251 über einen TTL-Puffer und einen PNP-Transistor geschaltet, wobei der Ausgang des TTL-Puffers wieder über eine separate Leitung als RS 232 ähnliche Schnittstelle auf den Serieninterface-Steckverbinder herausgeführt ist. Der PNP-Transistor prägt den Strom der Datenübertragungs-Stromschleife.

Die restlichen Ausgänge des 8251 sind ungepuffert auf den Serienstecker herausgeführt.

Der Clear to Send Eingang des USART verhindert das Aussenden von Daten, wenn er auf HIGH steht.

Da dieser Eingang auf der ECB/C nicht abgeschlossen ist, empfiehlt es sich, auf dem Anschlußstecker eine Brücke zwischen CTS (PIN 15 Pfostenstecker) und GND (PIN 14 Pfostenstecker) zu legen.

# 2.1.6.1 Current Loop 20 mA (CL)

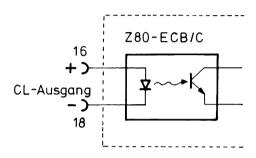

Der CL-Ausgang besteht aus einem PNP-Transistor, der über einen  $150\,\Omega$ -Widerstand den notwendigen Strom liefert.

Der CL-Eingang besteht aus einem Optokoppler mit nachgeschaltetem Verstärker.

Dieser Eingang ist dafür eingerichtet, daß der Sender den Strom für die Schnittstelle liefert. Ist dies nicht möglich, muß im Verbindungsstecker ein Widerstand eingebaut werden:

Der CL-Sender liefert dann lediglich ein "closed contact"-Signal, wobei der Strom für die Leuchtdiode über den  $150\,\Omega$ -Widerstand aus den  $+5\,V$  der Zentraleinheit erzeugt wird.

# 2.1.6.2 RS 232 C/V 24 Schnittstelle

Der RS 232 C Eingang der SST ist ein Low Power Schottky TTL Eingang. Um diesen mit echten RS 232 C Signalen steuern zu können, ist im allgemeinen nur eine Zenerdiode im Verbindungsstecker notwendig.

Der RS 232C Ausgang ist ein Ausgang eines Low Power Schottky Gatters. Dieses liefert zwar die richtigen logischen Signale, nicht jedoch die Normpegel der RS 232 C Norm.

Hat ein anzuschließender RS 232C Leitungsempfänger eine Hysterese ≥2 V, ist ein Interface zwischenzuschalten.

# 2.1.7 Hinweise zur Interrupt-Behandlung

Bei Mehrbaugruppen-Systemen, die unter Interrupt arbeiten. existiert grundsätzlich das Problem, die RETI-Anweisung über die Datenbuspuffer zu bringen.

Da einerseits Interrupt auf der Zentralplatine möglich sein muß, andererseits das Anwenderprogramm vom Entwicklungssystem auf beliebige (also auch außerhalb des 1kB-Bereichs der ECB/C) Speicherbereiche gelegt werden kann, existieren zur Testbarkeit der Anwender-Programme über den Echtzeit-Testadapter des Z80-Entwicklungssystems nur folgende mögliche Programmstrukturen:

- aa) Im gesamten Programm kommt nur ein einziger RETI-Befehl vor, der im Speicherbereich 0...1 kByte stehen muß (adressiert über eine Marke IRET).

- ab) Der Rücksprung aus weiteren Interrupt-Bedienroutinen erfolgt dann über den Befehl

JP IRET. oder

bb) alle Interrupt-Service-Routinen liegen im RAM/ROM-Speicherbereich der ECB/C-Baugruppe.

Wird in der Testphase mit dem Z80-Entwicklungssysteminternen Speicher gearbeitet, so ist außerdem sicher zu stellen, daß keine Prom's in den Promsockeln der ECB/C stecken. Ist dies nicht der Fall, kommt es bei jeder Ausführung eines RETI-Befehls zu einem Buskonflikt, der in der Regel verhindert, daß die I/O-Bausteine den RETI-Befehl richtig decodieren.

## 2.2 Adressen-Belegung des Z80-ECB/C

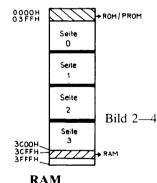

# 2.2.1 Speicher

Der Speicher ist in 4 kByte-Seiten eingeteilt, bei Verwendung des 1/4 kByte-Speichers auf der ECB/C-Platine bleibt der Rest der Seite, in der das RAM liegt, unbenutzt.

Die ausgelieferte Standardversion hat folgende Zuweisung (Bild 2-4):

### ROM/PROM Adresse: 0 0 0 0 0 1/4 kByte $\mathbf{C}$ F

Der RAM-Bereich wurde an das obere Ende der Seite 3 gelegt, da ECB-Systeme dann problemlos mit der Minimal-Ausrüstung des Z80-Entwicklungssystems hard- und software-mäßig auszutesten sind.

## 2.2.2 Ein/Ausgabe

Die Ein/Ausgabe-Bausteine auf dem Z80-ECB/C sind in 1 aus 8 Code der Speicheradress-Bits 0-3 dekodiert.

**Z80-PIO:**

PORT B/A A0 LOW = A; HI = B

CONTROL DATA A1 LOW = DATA; HI = CONTROL

A2 LOW = CHIP SELECTED

USART:

CONTROL/DATA A1 LOW = DATA; HI = CONTROL A3 LOW = CHIP SELECTED CHIP SEL

Es ist zu beachten, daß bei Erweiterung um weitere I/O-Bausteine die Adreß-Bits 2 und 3 immer HI sind!

Die Adressen für die Ein/Ausgabe-Bausteine ergeben sich damit wie folgt:

PORT B: DATA 09H PIO:

> PORT B: CONTROL 0BH PORT A: DATA 08H

PORT A: CONTROL 0AH

CONTROL: USART:

06H DATA: 04H

Grundsätzlich nicht erlaubt sind die I/O Adressen X0 . . . X3H, da dann sowohl USART als auch PIO ausgewählt sind  $(X = 0 \dots F).$

Bild 2-5

# 2.3 Pinbelegungen

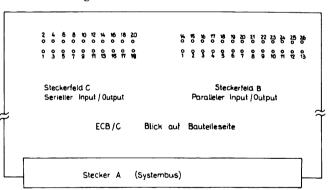

## 2.3.1. Ein/Ausgabe-Stecker des ECB/C

Stift-Nr. Steckerfeld C 20 pol. WWP Steckerfeld

- DTR (Data Terminal Ready; 8251) 1

- Current loop Out + 2

- 3 RTS (Request to send Data; 8251)

- 4 Current loop Out — (GND)

- 5 DSR (Data Set Ready; 8251)

- 6 NC

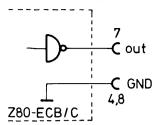

- 7 RS 232 Out +

- 8 **GND**

- 9 +5V

- 10 +5V

- NC 11

- Tx EMPTY (Transmitter Empty; 8251) 12

- RS 232 IN + 13

- 14 **GND**

- 15 CTS (Clear to send Data; 8251)

- 16 Current loop in +

- RxRDY (Receiver Ready; 8251) 17

```

Steckerfeld C

20 pol. WWP Steckerfeld

Stift-Nr.

10

ASTB

A Strobe

B Strobe

18

11

BSTB

Current loop in —

12

ARDY

A Ready

19

Tx Ready (Transmitter Ready; 8251)

+ 5 V

20

13

GND

14

passendes Gegenstück: 20 pol. Pfosten Verbinder

15

B7

z. B. Scotch 3421—0000

B6

16

17

B5

Steckerfeld B

26 pol. WWP-Steckerfeld

Stift-Nr.

B4

PIO

18

19

B3

PORT B

GND

1

20

B2

2

A7

21

B1

3

A6

B0

22

4

A5

NC

23

5

PIO PORTA

A4

24

NC

6

A3

25

BRDY B Ready

A2

26

+5V

8

A 1

Gegenstück: 26 pol. Pfosten-Verbinder

9

A0

z.B. Scotch 3399—0000

```

# 2.3.2 Der ECB-Bus.

Die folgende Anschlußbelegung ist für alle Baugruppen der ECB-Serien verschiedener Hersteller genormt. Die einzelnen Platinen sind durch 64polige Steckverbinder (VG 95324) über 1:1 Verdrahtung miteinander verbunden. Die Angaben über Fan In und Fan Out beziehen sich auf die Zentralplatine ECB/C.

|                                        | Stecker Pin  | Bezeichnung                         | Fan Out (TTL)          | Fan In                     | Kommentar                |

|----------------------------------------|--------------|-------------------------------------|------------------------|----------------------------|--------------------------|

| A 0                                    | 5c           | Adresse 0                           | 9                      |                            |                          |

| A 1                                    | 7c           | Adresse 1                           | 9                      |                            |                          |

| A 2                                    | 6a           | Adresse 2                           | 9                      |                            |                          |

| A 3<br>A 4                             | 6c<br>7a     | Adresse 3 Adresse 4                 | 9                      |                            | Adress-Bus               |

| A 4<br>A 5                             | 7a<br>8a     | Adresse 5                           | 9                      |                            | (Tri-State<br>bei BUSAK) |

| A 6                                    | 9a           | Adresse 6                           | 9                      |                            | bei Besak)               |

| A 7                                    | 9c           | Adresse 7                           | 9                      |                            |                          |

| A 8                                    | 8c           | Adresse 8                           | 9                      |                            |                          |

| A 9                                    | 30a          | Adresse 9                           | 9                      |                            | Ausgänge                 |

| A 10                                   | 18c          | Adresse 10                          | 9                      |                            |                          |

| A 11                                   | 17c          | Adresse 11                          | 9                      |                            |                          |

| A 12<br>A 13                           | 27c<br>29a   | Adresse 12<br>Adresse 13            | 9                      |                            |                          |

| A 13<br>A 14                           | 18a          | Adresse 13 Adresse 14               | 9                      |                            |                          |

| A 15                                   | 28c          | Adresse 15                          | ý ý                    |                            |                          |

|                                        |              | 7 taresse 13                        | ,                      |                            |                          |

| D 0                                    | 2c ·         | Data 0                              | 25 mA low              | 0,25 mA Low                |                          |

| D 1                                    | 14c          | Data 1                              | 25 mA low              | 0,25 mA Low                | Daten Bus                |

| D 2                                    | 4c -         | Data 2                              | 25 mA low              | 0,25 mA Low                | Bidirek-                 |

| D 3<br>D 4                             | 4a .<br>5a - | Data 3<br>Data 4                    | 25 mA low<br>25 mA low | 0,25 mA Low<br>0,25 mA Low | tional;                  |

| D 5                                    | 2            | Data 4<br>Data 5                    | 25 mA low              | 0,25 mA Low                | (Tri-State<br>bei BUSAK) |

| D 6                                    | 2a           | Data 5<br>Data 6                    | 25 mA low              | 0,25 mA Low                | oci BOSAK)               |

| D 7                                    | 3c           | Data 7                              | 25 mA low              | 0,25 mA Low                |                          |

| D 8                                    | 10c          | Data 8                              |                        | ,                          | -                        |

| D 9                                    | 12c          | Data 9                              |                        |                            |                          |

| D 10                                   | 13c          | Data 10                             |                        |                            |                          |

| D 11                                   | 14a          | Data 11                             |                        | viert für 16 bit-          |                          |

| D 12                                   | 23c          | Data 12                             |                        | putersysteme               |                          |

| D 13<br>D 14                           | 19c<br>21a   | Data 13<br>Data 14                  | (z. B. z               | ZILOG Z8000)               |                          |

| D 15                                   | 22a          | Data 14<br>Data 15                  |                        |                            |                          |

|                                        |              |                                     | _                      |                            | <del> </del>             |

| $\frac{\overline{M1}}{\overline{MBO}}$ | 20a          | Maschinenzyklus 1                   | 9                      |                            |                          |

| MRQ<br>IORQ                            | 30c<br>27a   | Memory Request                      | 9 9                    |                            | Country                  |

| RD                                     | 24c          | IN/OUT Request<br>Read              | 9                      |                            | System<br>Steuerbus      |

| WR                                     | 22c          | Write                               | 9<br>9<br>9            |                            | Ausgänge                 |

| RFRSH                                  | 28a          | Refresh                             | 9                      |                            | / rusgunge               |

| HLT                                    | 25c          | Halt                                | 9                      |                            |                          |

| WAIT                                   | 10a          | Wait                                |                        | 1 mA Low 4,7 kPull up      | CPU-                     |

| INT                                    | 21c          | Interrupt                           |                        | 1 mA Low 4,7 kPull up      | Steuer-                  |

| NMI                                    | 20c          | non Mask. Int.                      |                        | 1 mA Low 4,7 kPull up      | Eingänge                 |

| RESET                                  | 31c          | Reset                               |                        | 1,4 mA Low 4,7 kPull up    |                          |

| IEI 1                                  | 11c          | Int. enable in                      |                        | 1 mA Low, 4,7 kPull up     | Daisy Chain-             |

| IEO 1                                  | 16c          | Int. enable out                     | 1                      | -                          | Interrupt-               |

|                                        |              |                                     |                        |                            | Steuerung                |

| PWRCL                                  | 26c          | Power on clear                      | 9                      |                            |                          |

| Φ                                      | 29c          | Clock 2,45 MHz                      | 1 (330Ω Pull up)       |                            | Ausgänge                 |

| 2Ф                                     | 16a          | $2 \times \text{Clock}$             |                        | •                          |                          |

| nΦ                                     | 25a          | $n \times Clock$                    |                        |                            |                          |

| BUSRQ                                  | 11a          | Busrequest                          |                        | 1 mA Low 4,7 kPull up      | Bus-Steuerung            |

| BUSAK                                  | 31a          | Busacknowledge                      | 9                      | ,, ni un up                | für DMA-                 |

| BAI 1                                  | 12a          | Busprioritätssteuerung Ein          |                        |                            | basierende               |

| BAO 1                                  | 17a          | Busprioritätssteuerung Aus          |                        |                            | Systeme                  |

| WRITE EN                               | 26a          | Write Enable                        |                        |                            | Schreibfreigabe          |

|                                        |              |                                     |                        |                            | für ECB/D                |

| DPR                                    | 23a          |                                     |                        |                            | Synchronisation          |

|                                        |              |                                     |                        |                            | für ECB/V                |

| +5                                     | 1a,c         | + 5 V                               |                        |                            | Spannungsversor          |

| GND                                    | 32a,c        | Ground                              |                        |                            | gungsleitungen           |

| + 12                                   | 13a          | + 12 V } für EPROMS                 |                        |                            |                          |

| - 5                                    | 15a          | -5V)                                |                        |                            |                          |

| +15                                    | 19a          | + 15 V \ für V 24 und               |                        |                            |                          |

|                                        |              | <ul><li>15 V J AD-Wandler</li></ul> | I                      |                            | 1                        |

| - 15<br>VC MOS                         | 15c<br>24a   | + 5 V Batterie-Spannung             |                        |                            |                          |

# Speicher-erweiterungsbaugruppe

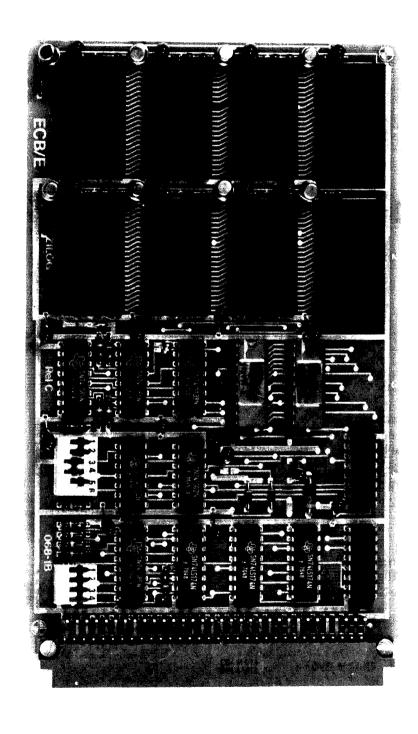

# 3. Die Erweiterungsbaugruppe Z80-ECB/E

# 3.1 Schaltungsbeschreibung

Die Baugruppe umfaßt folgende Funktionseinheiten:

- 1...8 kByte Festwertspeicher (ROM, PROM oder EPROM)

- 1 kByte statisches RAM

- Decoder

- Schalter zur Speicherbereichsfestlegung

- Busseitiger 64-poliger Stecker nach DIN 41612 (VG 95324)

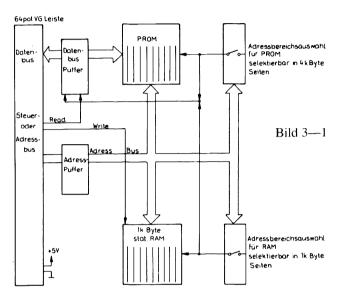

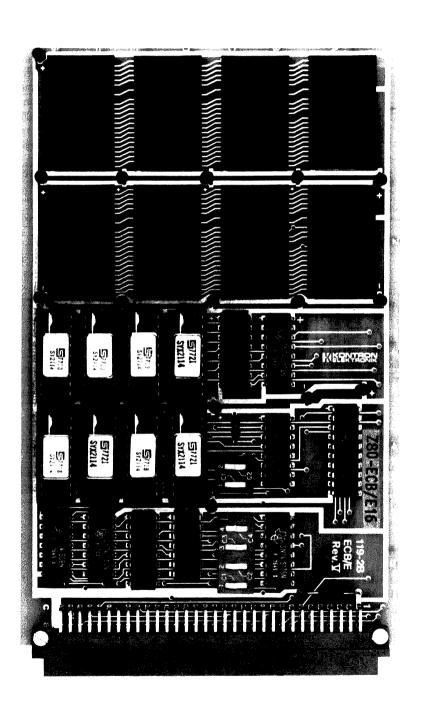

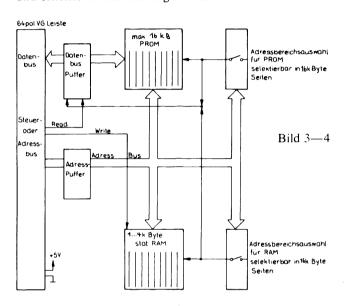

Bild 3—1 ist das zugehörige Blockschaltbild. Man sieht, daß auch hier die Systembusse gepuffert sind; dadurch ergibt sich zusammen mit den Puffern auf der Zentralplatine Z80-ECB/C eine zweifache Pufferung, was volle Erweiterbarkeit und erhöhte Störsicherheit garantiert.

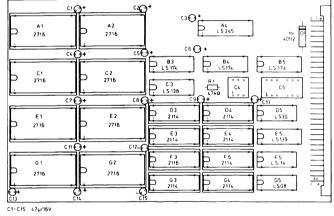

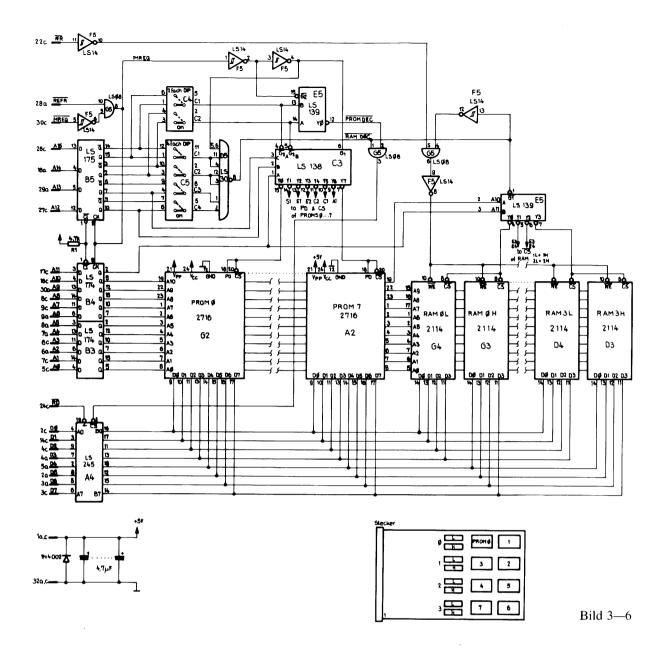

Bild 3—2 zeigt die Gesamtschaltung der Baugruppe, die in folgendem näher erläutert wird.

# 3.1.1 Pufferung und Decodierung

Die Übertragungsrichtung der bidirektionalen Datenbus-Puffer wird durch das  $\overline{RD}$ -Signal bestimmt.

Die logischen Verknüpfungen sind wie folgt:

$\frac{\overline{CS}}{\overline{RD}} = \frac{\overline{MEMSEL} \wedge \overline{MRQ}}{\overline{RD}}$   $= \overline{RD}\text{-Signal der Z80-CPU}$

Dabei sind:

RD = Richtungssignal

(High = zur betreffenden Karte hin)

CS = Aktivierung (High = Puffer gesperrt)

MEMSEL = Anforderung für Speicher auf ECB/E

# 3.1.2 Programmspeicher

Die Baugruppe enthält 8 24-Pin-Sockel, in die wahlweise folgende Festwertspeicherbausteine (bzw. hierzu pinkompatible Bausteine) eingesteckt werden können

HARRIS HM 7641 fusible PROM  $\frac{1}{2}$  k  $\times$  8 (=  $\frac{1}{2}$  KByte) HARRIS HM 7608 oder 7681 fusible PROM 1 k  $\times$  8 (= 1 KByte)

2708/8708/2758 EPROM 1 k×8 (= 1 KByte)

Bausteine 2716 können durch Eingriffe in die Verdrahtung eingesetzt werden.

Gelieferte Verdrahtung ist für HM 7641. Sollen HM 7608 oder 2708/8708-Bausteine eingesetzt werden, sind die Drahtbrücken (= "Jumpers") entsprechend Tab. 1 zu verdrahten.

Für 2708 EPROM's müssen zusätzliche externe -5 und +12 V-Versorgungsspannungen am Busstecker angelegt werden Der auf der Platine befindliche 4-fach-Dil-Schalter dient zur Festlegung der Anfangsadresse des Festwertspeicherbereichs. Bitte beachten Sie, daß die Festwertspeicherkapazität bei Verwendung von HM 7641 4 KByte, bei Verwendung von HM 7608 oder 2708/2758 8 KByte beträgt.

Bestückung und Verdrahtung ist in diesem Fall entsprechend Tabelle 1 zu ändern.

Da die Worst-Case Zugriffszeit der EPROM's ein Arbeiten mit maximaler Z80-CPU-Taktfrequenz nicht erlaubt, können nur selektierte (tc<380 nsec.) 2708-Bausteine verwendet werden, oder aber die CPU-Taktfrequenz ist entsprechend zu erniedrigen. Das Einfügen eines Wait-Zyklus ist über einen hardwaremäßigen Zusatz zur Baugruppe möglich. Die entsprechende Schaltung findet man im CPU Manual (Adding a Wait State to any M 1 Cycle). Sie besteht aus lediglich einem D-Flipflop-Baustein. Eine entsprechende Schaltung ist auf der Rückwandverdrahtung der ECB/R vorgesehen. Ein Umstellen der Verdrahtung zum Einsatz von 16 kbit (= 2 kByte) EPROM's (INTEL 2716) ist folgendermaßen möglich:

- a) Änderung am Chipauswahlbaustein (LS 138 IC Nr. D3):

- Jumper 3 und 4 öffnen

- IC D3 Pin 1 auf Pin 12 von E3

- IC D3 Pin 2 auftrennen und auf Pin 13 von IC E3

- IC D3 Pin 3 auftrennen und auf Pin 15 von IC E3

- b) Änderung des PROM-Bereich-Decoders (LS 85 IC Nr. E5)

- Jumper 5 öffnen

- Pin 12 von IC E5 öffnen und mit Pin 10 vom gleichen IC verbinden.

- Schalterblock F5 (Prom Auswahl) Schalter 3 und 4 immer AUS.

Schalter 1 und 2 ergeben dann 4 mögliche Adreßbereiche:

| S1  | S2  | Adresse  |

|-----|-----|----------|

| EIN | EIN | 03FFF    |

| EIN | AUS | 40007FFF |

| AUS | EIN | 80003FFF |

| AUS | AUS | C000FFFF |

- c) Änderung der Adreßleitungen der PROMS:

- Jumper J1 öffnen, J2 schließen.

- Zuleitung +12 V Pin 13a von VG-Leiste auftrennen, zugehörige Block-C (oberhalb D2) und Diode D2 entfernen. Leitung dann mit Adresse 10 IC D5 Pin 15 verbinden.

- Zuleitung -5V Pin 15a von VG Leiste auftrennen, Diode D3 und Block-C links unterhalb D3 entfernen. Leitung dann mit +5V verbinden.

| Tab. 1: | :              |            |               |

|---------|----------------|------------|---------------|

| 1/2 kB  | Bipolare Proms | <b>J</b> 1 | geschlossen   |

|         | 7.4            | مير        | geschlossen   |

|         |                | <b>J</b> 5 | geschlossen   |

| 1 kB    | Bipolare Proms | J 1        | geschlossen   |

| l       |                | J4         | geschlossen   |

| 1 kB    | 8708           | J2         | geschlossen 🗸 |

|         |                | J 4        | geschlossen 🗸 |

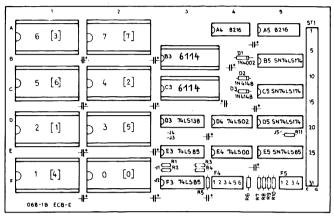

Die Zuweisung der Prom Sockel zu den Adressen ist im Bestückungsplan angegeben. Die Zahlen in eckigen Klammern beziehen sich auf die Verwendung von 1 kB Proms.

Der Seitenwahl-Schalter F 5 für die Proms legt die Seite in der die ECB/E arbeitet wie folgt fest:

| S 1 | <b>S</b> 2 | <b>S</b> 3 | <b>S</b> 4 | Seite |

|-----|------------|------------|------------|-------|

| AUS | AUS        | AUS        | AUS        | 15    |

| AUS | AUS        | AUS        | EIN        | 14    |

| AUS | AUS        | EIN        | AUS        | 13    |

| AUS | AUS        | EIN        | EIN        | 12    |

| AUS | EIN        | AUS        | AUS        | 11    |

| AUS | EIN        | AUS        | EIN        | 10    |

| AUS | EIN        | EIN        | AUS        | 9     |

| AUS | EIN        | EIN        | EIN        | 8     |

| EIN | AUS        | AUS        | AUS        | 7     |

| EIN | AUS        | AUS        | EIN        | 6     |

| EIN | AUS        | EIN        | AUS        | 5     |

| EIN | AUS        | EIN        | EIN        | 4     |

| EIN | EIN        | AUS        | AUS        | 3     |

| EIN | EIN        | AUS        | EIN        | 2     |

| EIN | EIN        | EIN        | AUS        | 1     |

| EIN | EIN        | EIN        | EIN        | 0     |

Werden 1 kB Proms verwendet, ist der Schalter S4 offen zu halten. Die Zuweisung ergibt sich dann analog zu obiger Tabelle mit der halben Anzahl von Seiten.

AUS & OPEN

# 3.1.3 Schreib/Lesespeicher

Der Schreib/Lesespeicher ist aus 2 Stück 1 Kbit  $\times$  4-Bausteinen aufgebaut.

Seine Anfangsadresse wird durch den 6-fachen DIL-Schalter auf die Platine festgelegt. (Position F4auf Best.-Plan). Dabei entspricht der Schalter S 1 der Adresse 15, der Schalter S 6 der Adresse 10. Zu beachten ist, daß eine Adresse auf logisch Null verglichen wird, wenn der entspechende Schalter geschlossen ist.

alle Widerstände  $4.7k\Omega$ alle Elkos  $4.7\mu$ F

Bild 3—3

# Speicher-erweiterungsbaugruppe

# 3.2 Die Erweiterungsbaugruppe Z80-ECB/E16

# 3.2.1 Schaltungsbeschreibung

Die Baugruppe umfaßt folgende Funktionseinheiten:

- Bis zu 16 kByte Festwertspeicher (ROM, PROM oder EPROM)

- 1 kByte statisches RAM, bis zu 4 kByte nachrüstbar.

- Decoder

- Schalter zur Speicherbereichsfestlegung

- Busseitiger 64-poliger Stecker nach DIN 41612 (VG 95324)

Bild 3—1 ist das zugehörige Blockschaltbild. Man sieht, daß auch hier die Systembusse gepuffert sind; dadurch ergibt sich zusammen mit den Puffern auf der Zentralplatine Z80-ECB/C eine zweifache Pufferung, was volle Erweiterbarkeit und erhöhte Störsicherheit garantiert.

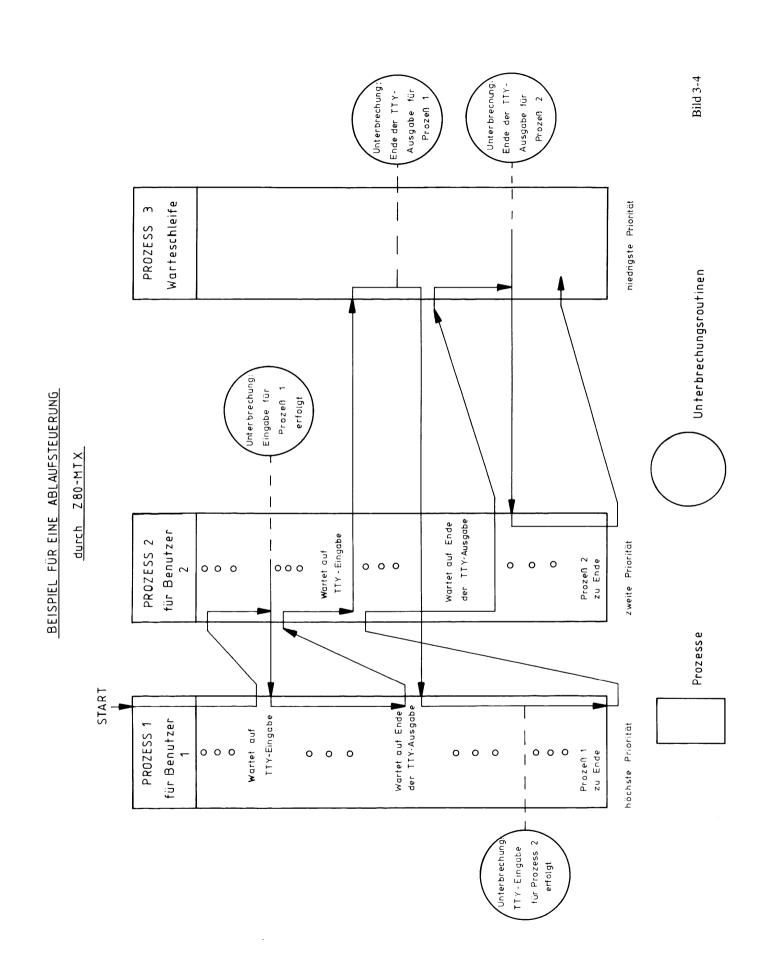

Bild 3—4 zeigt die Gesamtschaltung der Baugruppe, die in folgendem näher erläutert wird.

# 3.2.1.1 Pufferung und Decodierung

Die Übertragungsrichtung der bidirektionalen Datenbus-Puffer wird durch das  $\overline{RD}$ -Signal bestimmt.

Die logischen Verknüpfungen sind wie folgt:

$\overline{CS}$  =  $\overline{MEMSEL} \wedge \overline{MRQ}$  $\overline{RD}$  =  $\overline{RD}$ -Signal der Z80-CPU

Dabei sind:

RD = Richtungssignal

(High = zur betreffenden Karte hin)

CS = Aktivierung (High = Puffer gesperrt)

MEMSEL = Anforderung für Speicher auf ECB/E

# 3.2.1.2 Programmspeicher

Die Baugruppe enthält 8 24-Pin-Sockel, in die wahlweise folgende Festwertspeicherbausteine (bzw. hierzu pinkompatible Bausteine) eingesteckt werden können

i 2716 bzw. Z6716 (2 kByte) i 2758 (1 kByte)

Gelieferte Verdrahtung ist für i 2716/Z6716.

Bei der Verwendung von 2758-Bausteinen ist zu beachten, daß sich dabei ein nicht zusammenhängender Speicherbereich ergibt (jedes 2. kByte wird physikalisch "doppelt" adressiert).

Da die Worst-Case Zugriffszeit der EPROM's ein Arbeiten mit maximaler Z80-CPU-Taktfrequenz nicht erlaubt, können nur selektierte (t<sub>c</sub><380 nsec.) 2716-Bausteine verwendet werden, oder aber die CPU-Taktfrequenz ist entsprechend zu erniedrigen. Das Einfügen eines Wait-Zyklus ist über einen hardwaremäßigen Zusatz zur Baugruppe möglich. Die entsprechende Schaltung findet man im CPU Manual (Adding a Wait State to any M 1 Cycle). Sie besteht aus lediglich einem D-Flipflop-Baustein. Eine entsprechende Schaltung ist auf der Rückwandverdrahtung der ECB/R vorgesehen.

Die Adreßdecodierung erfolgt durch den zweipoligen DIL-Schalter. Sein Schalter 1 schaltetAdreßbit 14, Schalter 2 Adreßbit 15. Schalter auf der den RAM's zugewandten Seite niedergedrückt entspricht dem Wert Null des zugehörigen Adreßbits.

# 3.1.3 Schreib/Lesespeicher

Der Schreib/Lesespeicher ist aus 2 Stück 1 Kbit × 4-Bausteinen aufgebaut. Durch Einstecken weiterer 1K×4-Bausteinen in die 6 freien Fassungen läßt sich der Speicherbereich auf der Platine in 1 kB-Schritten auf 4 kByte erweitern.

Die Anfangsadresse wird durch den 4-fachen DIL-Schalter auf der Platine festgelegt.

Die RAM-Dekodierung erfolgt mittels des 4-poligen DIP-Schalters.

Die vier höchstwertigen Adreßbits werden wie folgt geschaltet:

Schalter 1 : Adreßbit 12 Schalter 2 : Adreßbit 13 Schalter 3 : Adreßbit 14 Schalter 4 : Adreßbit 15

Schalter auf der den RAM's zugewandten Seite niedergedrückt entspricht dem Wert des Adreßbits von 0.

Bild 3-5

# **Z80-ECB/I**

# Ein/Ausgabe-Erweiterungsbaugruppe

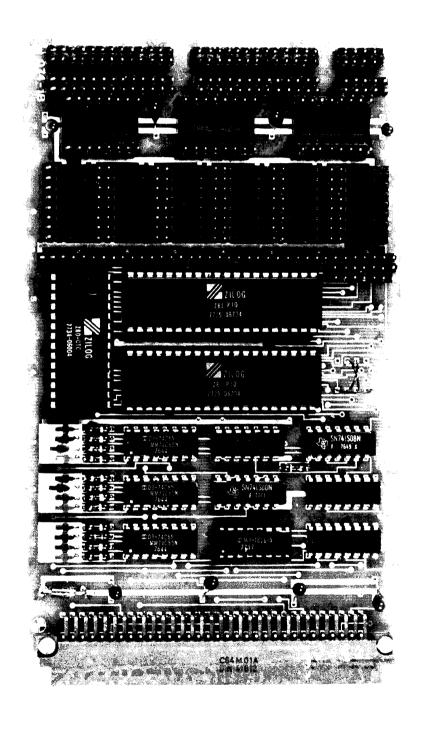

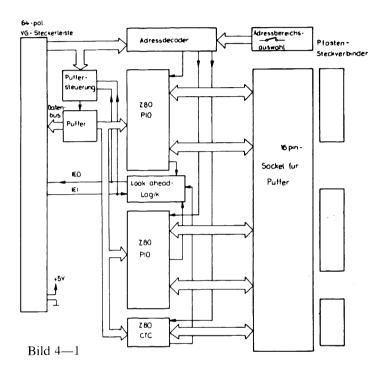

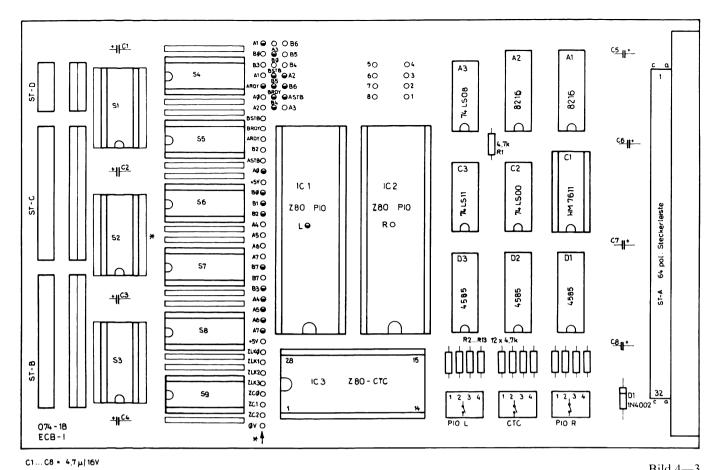

# 4. Die Ein/Ausgabebaugruppe Z80-ECB/I

Die Baugruppe umfaßt folgende Funktionseinheiten

- 4 Parallelschnittstellen (2 Stück Z80-PIO)

- 4 Zeitgeber/Ereigniszählkanäle (1 Stück Z80-CTC)

- 9 Unverdrahtete Fassungen für Standard-Interface-Bausteine

- Busseitig 64-poliger Stecker nach DIN 41612 (VG 95324)

- I/O-seitig 3M-WWP-Pfostensteckverbinder

Bild 4—1 zeigt das zugehörige Blockschaltbild:

Die Baugruppe behandelt mit ihren 2 Bausteinen Z80-PIO und dem 1 Baustein Z80-CTC insgesamt vier 8bit-Ein/Ausgabekanäle, die jeweils über 2 zusätzliche Leitungen für Quittungsbetrieb verfügen, und vier Ereigniszähler/Zeitgeberkanäle. Einzelheiten über den Baustein Z80-PIO finden Sie im Z80-PIO-Technical Manual; der Baustein Z80-CTC ist im Z80-CTC-Technical Manual beschrieben.

Auch bei dieser Baugruppe wurde das Prinzip der doppelten Pufferung weiterverfolgt.

Der hierdurch bedingte Aufwand besteht in den beiden bidirektionalen Puffern 8216 und einem entsprechend Bild 2—3 programmierten Puffer-Steuer PROM HM 7611.

Die zugehörigen logischen Verknüpfungen sind:

$$\overline{IIOIN} = (\overline{IORQ} \wedge \overline{IODEC} \wedge \overline{RD}) \vee IO READ$$

$$(\overline{IORQ} \wedge \overline{MI} \wedge IIEI \wedge \overline{IIEO})$$

$$\overline{INTA}$$

$$\overline{CS} = 0$$

Dabei sind:

**IIOIN** = Richtungssteuersignal

(High = zur betreffenden Karte hin)

CS = Aktivierungssignal (High = Puffer gesperrt)

M1: Maschinenzyklus 1

IORQ: I/O Anforderung

IODEC: I/O Auswahl

RD: Read

IIEI: Interrupt Enable IN IIEO: Interrupt Enable OUT

Die Adressen der einzelnen Ports können über DIL-Schalter festgelegt werden.

Es stehen 16 Adressen für jeden PIO bzw. CTC zur Verfügung. Die Schalterstellung ist invertiert zu betrachten:

**S4 S**3 S2 S1 Adresse FXH =**AUS AUS AUS** AUS und 0XH =EIN EIN EIN EIN

Durch direkte Auswahl der I/O-Bausteine auf der ECB/C-Karte müssen die Adreßbits 2 und 3 immer auf log 1 sein. Bei einer Schalterstellung

S4 S3 S2 S1 AUS EIN AUS EIN

am Schalter E 3 muß der PIO links wie folgt adressiert werden:

S4  $\triangleq$  I/O Adreßbit 7 S3  $\triangleq$  I/O Adreßbit 6 S2  $\triangleq$  I/O Adreßbit 5 S1  $\triangleq$  I/O Adreßbit 4 SX = AUS  $\rightarrow$  Adresse = 1 SX = EIN  $\rightarrow$  Adresse = 0

I/O Adresse (hex)

ACH = PI0 L Port A Data ADH = PI0 L Port B Data AEH = PI0 L Port A Control AFH = PI0 L Port B Control

Auf diese Weise ist es möglich das ECB-System auf insgesamt 5 I/O-Karten zu erweitern. Es stehen dann 20 I/O-Ports = 200 Leitungen und 5 Zähler/Zeitgeberbausteine zur Verfügung.

Zur Realisierung anwenderspezifischer Interfaces wurden auf der Baugruppe neun 16-polige Fassungen untergebracht, deren Ausgänge über Wire-Wrap-Stifte entsprechend der im Anwendungssystem gewünschten Steckerbelegung mit den 3 Pfostensteckverbindern verdrahtet werden.

Für den Fall, daß komplexere Interface-Schaltungen oder Verbindungen zur Busseite der Platinen hergestellt werden sollen, können diese Pfostensteckverbinder als Verbindungen zu "Huckepack"-(="Sandwich")-Platinen verwendet werden. Sollen die Ausgänge der PIO- bzw. CTC-Bausteine ohne zwischengeschaltete Puffer benutzt werden, sind die Grenzwerte bzw. Charakteristika zu beachten:

Z80-PIO:  $I_{OL}$  = 1,8 mA bei  $V_{OL}$  = max. 0,4 V (Port A)  $I_{OHD}$  = 1,5 . . . 3,8 mA bei  $V_{OH}$  = 1,5 V und Rext = 390  $\Omega$ (Darlington-Ausgänge der Ports B)

Z80-CTC  $I_{OL}$  = 1,8 mA bei  $V_{OL}$  = max. 0,4 V  $I_{OHD}$  = 1,5 . . . 3,8 mA bei  $V_{OH}$  = max. 1,5 V und Rext = 390  $\Omega$

\$1... \$9 \* Sockel 16 polig \* \* Wire Wrap Feld Bild 4—3

# Dynamische Speichererweiterungsbaugruppen

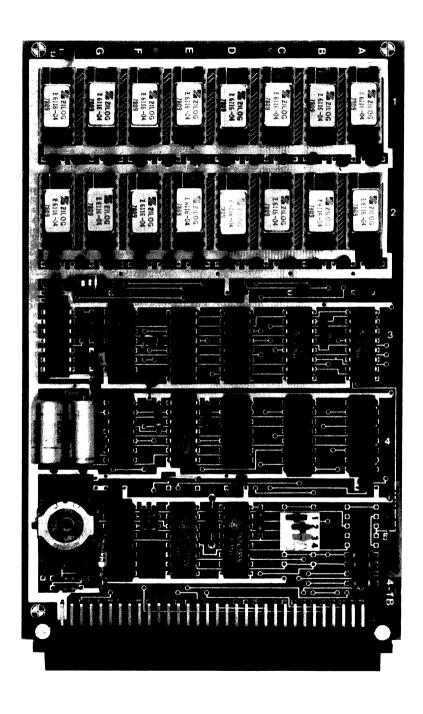

# 5. Speichererweiterungsbaugruppen der Serie Z80-ECB/D (/D8, /D16 und /D32)

Die Baugruppen der Serie ECB/D sind Baugruppen zur Schreib/Lesespeichererweiterung für RAM-intensive Systeme, die mit der Familie ECB aufgebaut sind. Sie sind in 3 Versionen erhältlich:

☐ Z80-ECB/D8 ist eine 8 kByte-Speichererweiterungseinheit, die mit dynamischen 4 kbit- 16 pin-RAM-Bausteinen realisiert ist. Die Anfangsadresse des gesamten Speicherbereichs auf der Platine läßt sich mit einemDIL-Schalter auf Speicheradressen zwischen 0 und 56k in 8k-Schritten einstellen.

| Bild 5—1: ECB/D8 Adreßauswahl-Schalterstellungen 4-fach DIP Schalter B5 |     |     |            |                 |  |  |  |

|-------------------------------------------------------------------------|-----|-----|------------|-----------------|--|--|--|

| S1                                                                      | S 2 | S3  | <b>S</b> 4 | ADRESSE (HEX)   |  |  |  |

| AUS                                                                     | EIN | EIN | EIN        | 0 1 <b>FFFH</b> |  |  |  |

| AUS                                                                     | AUS | EIN | EIN        | 2000 3FFFH      |  |  |  |

| AUS                                                                     | EIN | AUS | EIN        | 4000 5FFFH      |  |  |  |

| AUS                                                                     | AUS | AUS | EIN        | 6000 7FFFH      |  |  |  |

| AUS                                                                     | EIN | EIN | AUS        | 8000 9FFFH      |  |  |  |

| AUS                                                                     | AUS | EIN | AUS        | A000 BFFFH      |  |  |  |

| AUS                                                                     | EIN | AUS | AUS        | C000 DFFFH      |  |  |  |

| AUS                                                                     | AUS | AUS | AUS        | E000 FFFFH      |  |  |  |

□ Z80-ECB/D16 ist eine 16 kByte-Speichererweiterungseinheit, die mit dynamischen 16 kbit-16-pin-ZILOG-RAM-BausteinenZ6116 (oder Äquivalenztyp) realisiert ist. Die Baugruppe ist durch Einstecken weiterer 8 Bausteine Z6116 auf 32 kByte erweiterbar.

Bei Bestückung mit nur 16 kByte ist die Anfangsadresse wie bei der Z80-ECB/ D32 nur auf die Anfangsadressen 0H und 8000 H zu legen.

S4 = EIN : OHS4 = AUS : 8000HS2, 3 geschlossen S1 offen.

□ Z80-ECB/D32

ist eine 32 kByte-Speichererweiterungseinheit, die mit dynamischen 16 kbit-16pin-ZILOG-RAM-Bausteinen Z6116 (oder Äquivalenztyp) realisiert ist. Die Anfangsadresse des Speicherbereichs läßt sich auf 0 oder auf 8000H festlegen.

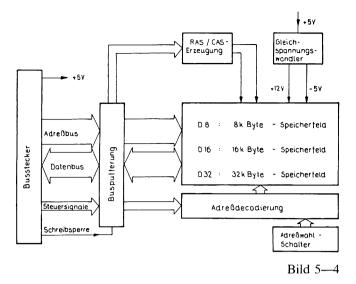

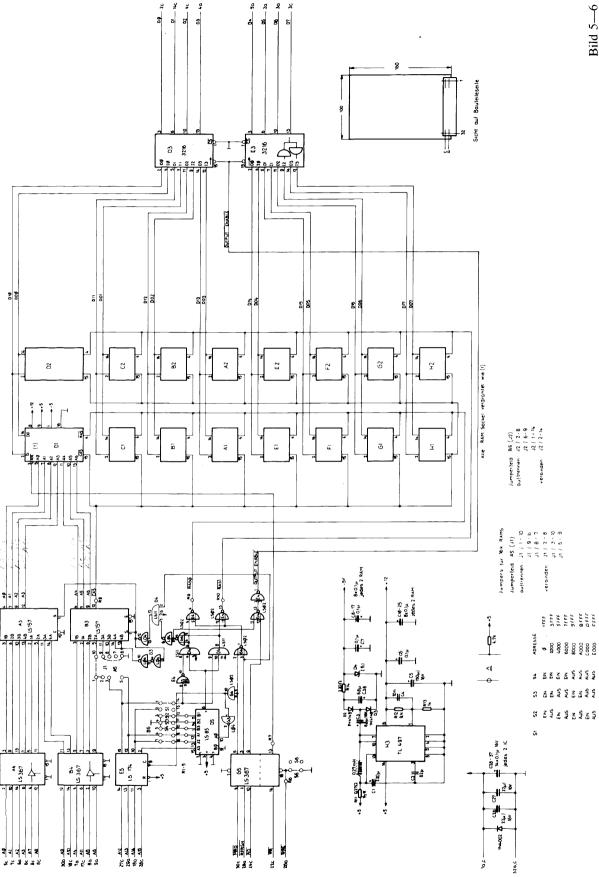

S4 = EIN : OHS2,3 geschlossen = AUS : 8000H S1

In allen Fällen ist die Zugriffszeit im Temperaturbereich von 0 ... 50°C zu 350 nsec. garantiert, so daß die Baugruppe zusammen mit der Z80-ECB/C mit der maximalen Betriebsfrequenz von 2,5 MHz ohne das Einfügen von WAIT-Zyklen arbeiten kann. Die für die dynamischen RAM-Bausteine zusätzlich benötigten Speisespannungen -5 V und +12 V werden mit einem Gleichspannungswandler auf der Platine erzeugt, so daß der gesamten Platine von außen her lediglich eine einzige +5 V-Versorungsspannung (0,6 A max.) zuzuführen ist.

Die gesamte Logik zum Demultiplexen und zur Erzeugung des Speicherrefresh in Z80-CPU-gesteuerten Systemen ist mit auf der Baugruppe untergebracht. Der Refresh erfolgt abhängig vom laufenden Programm max. alle 0,7 msec unter

der Kontrolle der Z80-CPU vollautomatisch ohne zusätzliche Software und ohne Verlust von Verarbeitungszeit, d.h. für den Anwender verhält sich die Baugruppe nach außen hin genauso wie jede statische Speichererweiterung.

Folgende Punkte sind jedoch zur Vermeidung von Informationsverlusten im dynamischen Speicher zu beachten:

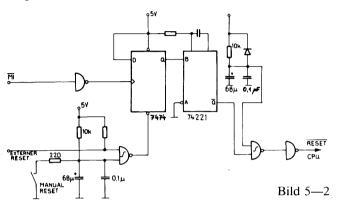

☐ Bei Verwendung des Signals RESET ist dafür Sorge zu tragen, daß die Dauer dieses Signals unter 2 msec liegt, da die CPU kein Refresh-Signal erzeugt, solange ihr RESET-Eingang auf LOW liegt. Ein einfacher Schalter genügt an dieser Stelle also nicht, falls Informationsverluste im dynamischen RAM beim Systemrückstellvorgang unerwünscht ist; die Problematik kann z. B. mit einem Differenzierglied umgangen werden, das der RESET-Leitung der CPU vorgeschaltet wird.

☐ Bei direktem Speicherzugriff (DMA) ist die Länge der DMA-Zugriffe so kurz zu wählen, daß immer noch alle 2 msec sämtliche Speicherstellen des dynamischen RAM's "aufgefrischt" werden.

Die Z80-CPU schaltet bei jedem M1-Zyklus die Refresh Adresse um 1weiter. Der Zeitraum zwischen zwei Refreshvorgängen ist abhängig von der Art der Befehle, die in einem Programm vorkommen. Geht man von den längsten Befehlen (23 Taktzyklen) aus, so beinhalten diese zwei M1-Zyklen.

Damit ergibt sich:

1 Refreshzyklus =

$$\frac{23}{2}$$

Taktzyklen · 128

$\approx 0.7$  ms bei einer Taktfrequenz von

2.5 MHz

Da die RAMS alle 2 ms einen vollständigen Refreshzyklus durchlaufen haben müssen, ergibt sich eine Restzeit von 1,3 msec für andere Aktivitäten.

Das eben über DMA Gesagte ist sinngemäß auch auf die Benützung des WAIT-Eingangs der Z80-CPU anzuwenden. da auch WAIT-Zyklen den Refresh-Vorgang vorübergehend unterbinden (s. Z80-CPU-Technical Manual).

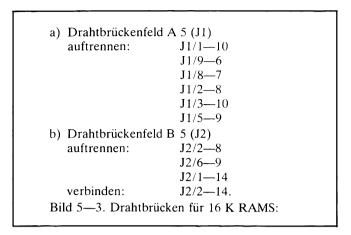

Die Dauer eines periodisch anliegenden WAIT-Signals muß also unter 1,3 msec liegen. Die Baugruppe Z80-ECB/ D8 läßt sich durch Austausch der 4 kbit-16 pin-Bausteine gegen pinkompatible 16 kbit-16 pin-Bausteine (z.B. ZILOG Z6116) und durch Verlegung der folgenden Drahtbrücken auf den Leistungsumfang der Z80-ECB/ D16 oder Z80-ECB-D32 erweitern (s. Bild 5—3):

Die Pinbelegung ist identisch mit der Zentralbaugruppe ECB/C, so daß 1:1 Verdrahtung möglich ist. Einzig zusätzlich belegte Leitung ist Pin 26a mit dem in Anschluß beschriebenen WRITE EN-Signal.

Auf den Baugruppen wurde außerdem ein Signal implementiert, das das Einschreiben in die RAM's verhindert ("WRITE EN"). Dieses Signal wurde auf den Systembus auf Pin 26a herausgeführt. Ausgeliefert wird die Baugruppe mit geschlossener Drahtbrücke S1, so daß der

Schreibzugriff freigegeben ist. Soll WRITE EN von externer Logik kontrolliert werden, ist diese Drahtbrücke zu entfernen und das entsprechende Bus-Signal zur Verfügung zu stellen.

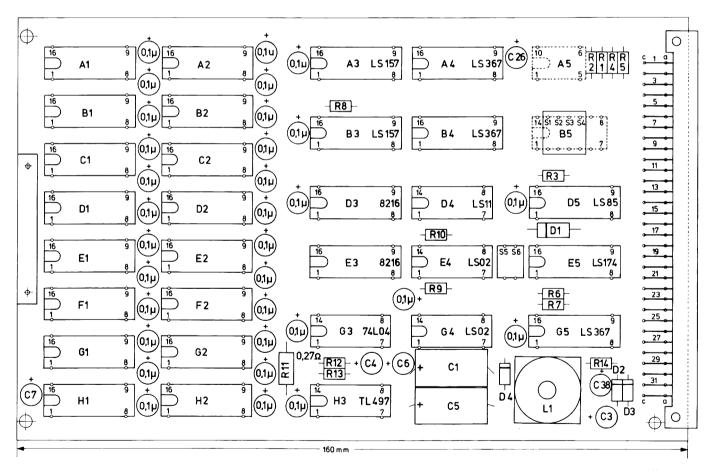

Weitere Eingriffe in die Schaltung sind nicht erforderlich. Die Schaltung der Baugruppen finden Sie im Bild 5—6.

# Zur Beachtung:

Dynamischer Speicher sind grundsätzlich störempfindlich und kritisch im Zeitverhalten.

Es empfiehlt sich daher, Baugruppen der ECB/D-Serie möglichst in Steckplätzen nahe der Zentralbaugruppe einzusetzen.

Bild 5-5

# Z80-ECB/V

# CMOS-Speichererweiterungsbaugruppe

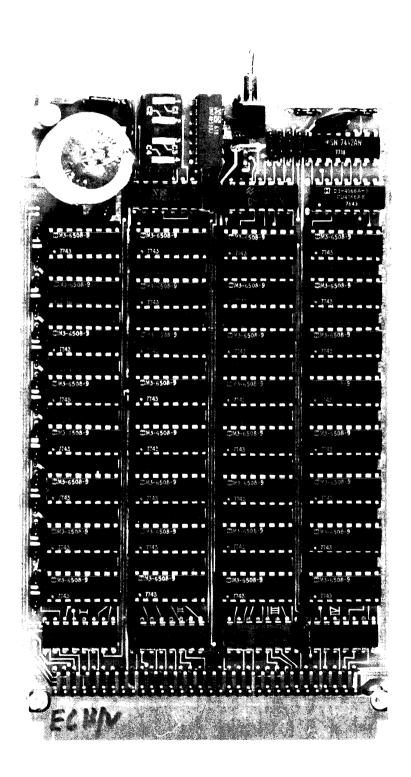

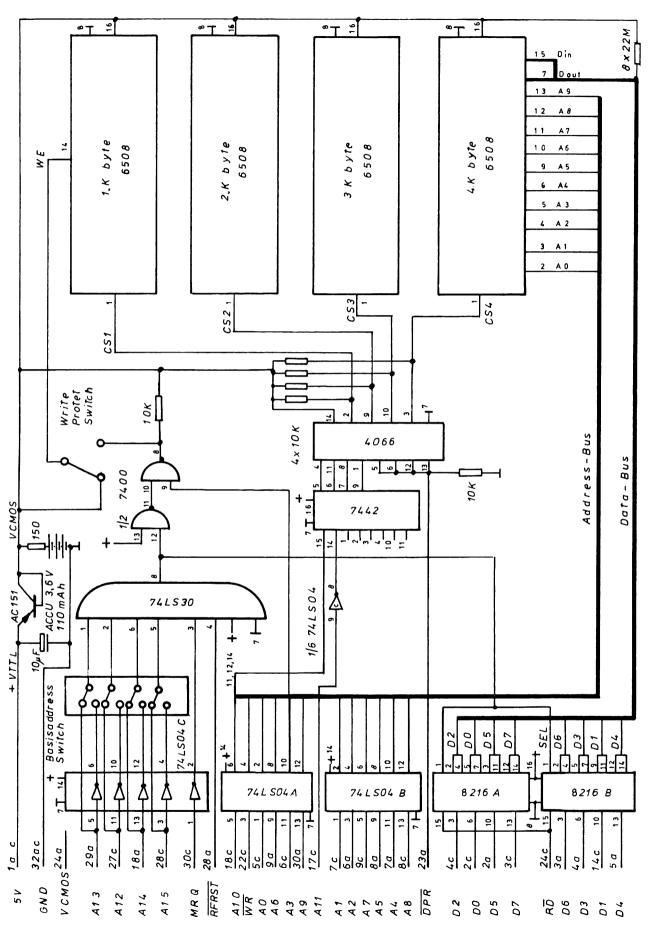

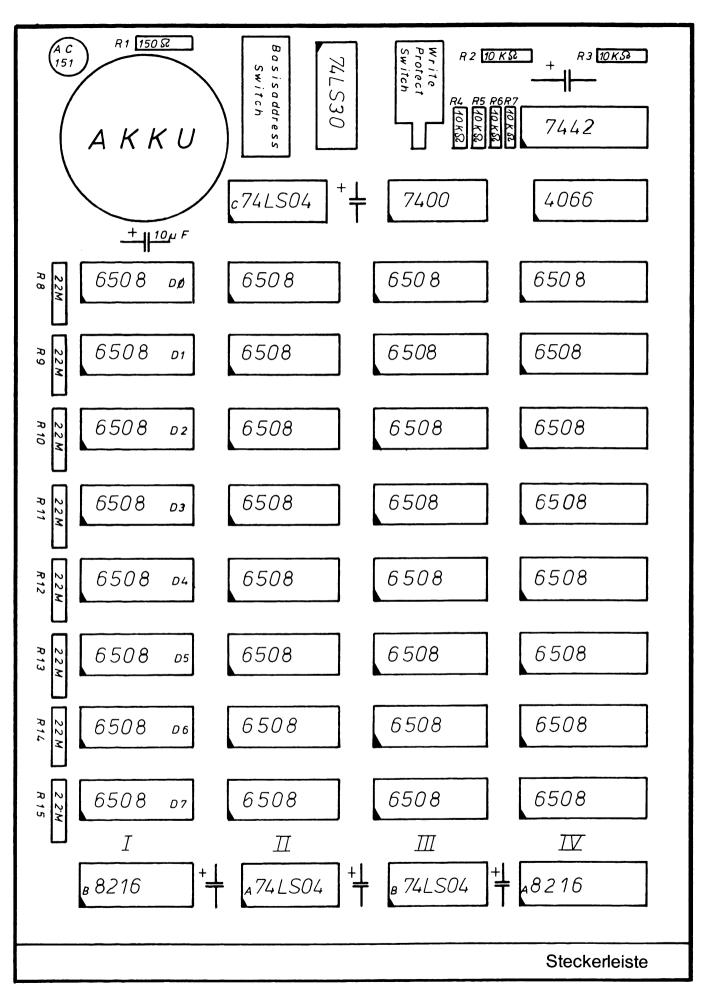

# 6. 4 kByte-CMOS-RAM-Karte Z80-ECB/V

# 6.1 Beschreibung

Die Einfach-Europakarte ECB/V ist eine voll statische 4 kByte-CMOS-Speicherbaugruppe hoher Flexibilität und Packungsdichte. Wegen der extrem niedrigen Stromaufnahme ist sie besonders für folgende zwei Anwendungen geeignet:

- ☐ Große und schnelle Arbeitsspeicher: z.B. 64 kByte = 16 Karten mit 2,5 A-Netzteil in einem 19"-Einschub evtl. über Zentral-Akku zu puffern: 20 mA Ruhestrom. Diese Packungsdichte ist nur durch die vernachlässigbare Wärmeentwicklung der CMOS-RAMS möglich.

- ☐ Nicht-flüchtige Speicher.

Programme und Daten können beim Austesten gegen Überschreiben geschützt werden (Speicher-Schutz-Schalter). Beim Abschalten des Systems oder bei Stromausfall bleiben die eingegebenen Daten erhalten.

Ferner kann man bei der System-Entwicklung auf die Verwendung von löschbaren PROM's verzichten,weil z.B. Programme bis zu ihrer endgültigen Festlegung auf der Karte erhalten bleiben (Speicherschutzschalter in Stellung "ROM"). Löschungen und Modifikationen können selektiv durch die normalen WRITE-Operationen vorgenommen werden, dazu muß lediglich der Speicherschutzschalter auf "RAM" geschaltet werden.

In gewissem Sinne bietet also diese CMOS-RAM-Karte eine preisgünstige, schnelle und platzsparende Alternative zu Kernspeicher-Systemen.

Eine oft willkommene Erleichterung für die Microcomputer-Entwickler bieten auch die auf der Karte angebrachten Basis-Adreß-Umschalter. Durch Betätigung eines 4 bit-DIL-Schalters kann so der Ansprechbereich der Karte z.B. im 64 kByte Adreßraum beliebig gewählt werden.

Die Worstcase-Zugriffszeit der Baugruppe ist im Temperaturbereich  $0\dots 50\,^{\circ}\text{C}$  zu 350 nsec garantiert, so daß die Verwendung zusammen mit der Baugruppe Z80-ECB/C ohne das Einfügen von WAIT-Zyklen bei einer max. Taktfrequenz von  $2.5\,\text{MHz}$  möglich ist.

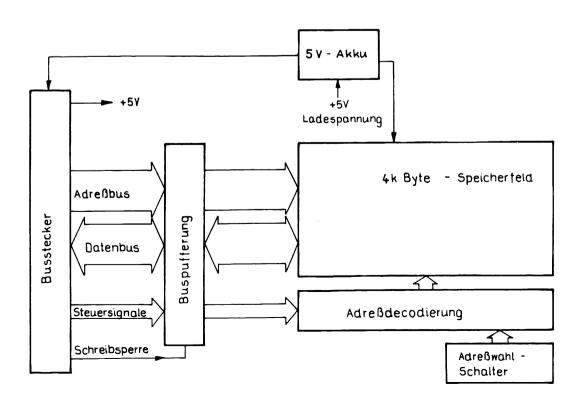

Die Blockschaltung zeigt Bild 6—1.

Die vollständige Schaltung der Baugruppe finden Sie in Bild 6—2; die Pinbelegung ist identisch mit der Zentral-Baugruppe ECB/C, so daß 1:1-Verdrahtung möglich ist.

## **6.2** Bedienungsanleitung

- a) Speicherschutzschalter (Write-Protect).

- Der Schalter in Stellung Leiterbahnseite ergibt Betriebsart "Quasi-ROM", in Richtung Bestückungsseite können Informationen in die RAM-Bausteine eingeschrieben werden

- b) Adreß-Vorwahlschalter (Basis-Adresse)

Der DIL-Schalter dient zur Vorwahl der höchstwertigen 4 Adreßbits. Nr. 4 schaltet das höchstwertige bit A15, Nr. 3, 2, 1 entsprechen A14, A13, A12. Schalter in Richtung Pufferbatterie: Adreßbit muß 1 sein, damit die Karte angesprochen wird. Schalter in Richtung des Kippschalters: Adreßbit = 0 für die Selektion.

# Beispiel:

DIL-Schalter Nr. 1 und 2 zum Akku, Nr. 3, 4 in Richtung Kippschalter, Write-Protect-Schalter zeigt zur Lötseite.

Die HEX Adresse 3000 — 3FFF ist für die Betriebsart "Ouasi-ROM" reserviert.

# ☐ Zur Beachtung:

Die Baugruppe ECB/V wird mit geladenem Akkumulator und aufgetrennter Verbindung zum Akkumulator geliefert, um seine Entladung während der Lagerungszeit zu vermeiden.

Ebenso ist vom Anwender dafür Sroge zu tragen, daß der Akkumulator vor Einsatz der Baugruppe als Netzausfallsicherung aufgeladen ist und zu berücksichtigen, daß sich der Akkumulator bei ausgeschaltetem Gerät entlädt.

Die Information im Speicher der Baugruppe bleibt nach Stromausfall oder Abschaltung ca. 5 Tage erhalten, vorausgesetzt, daß der Akkumulator zu diesem Zeitpunkt voll aufgeladen war.

Der Eingang DPR dient zur Synchronisation des CS-Eingangs bei Spannungsausfall.

Ist dies irrelevant, wirkt  $\overline{DPR}$  als Schreibschutz und ist über einen  $1 \, k\Omega$ -Pull-Up-Widerstand auf  $+5 \, V$  zu legen. Nähere Einzelheiten über Verwendung von  $\overline{DPR}$  s. Abschnitt 6.3.

Bild 6—1

Bild 6—3

$\overline{\mathsf{MRQ}}$ 30c

V<sub>CMOS</sub> pin 24 a V<sub>TTL</sub> 1 a, 1 NMI\* 20 c 1a, 1c RES 31c und 23a bei ECB/V

**GND** 32 a, c \* nur für Interrupt-Auslösung bei Stromausfall

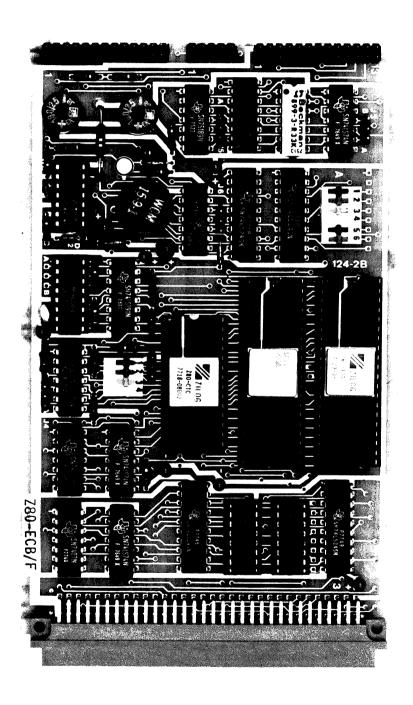

# Z80-ECB/F

# Ein/Ausgabe-Baugruppe für allgemeine Aufgaben und Floppy-Disk-Steuerung

Vorläufige Beschreibung

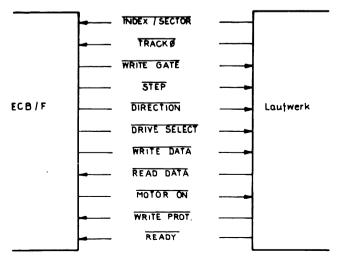

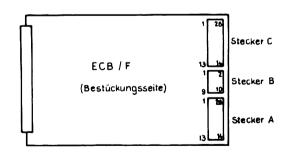

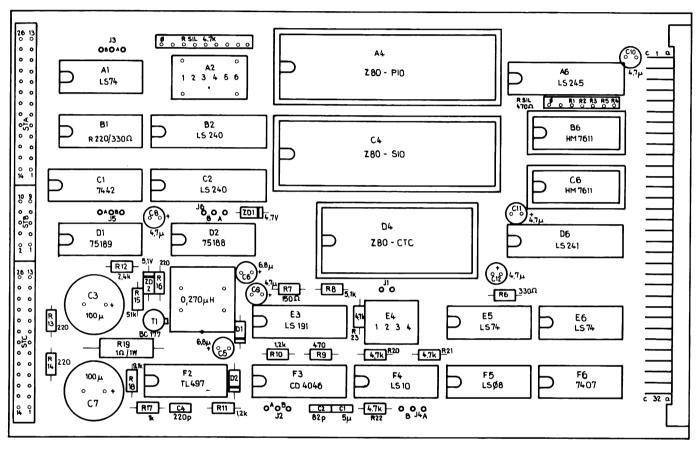

### 7. Ein/Ausgabe-Baugruppe für allgemeine Aufgaben und Floppy-Disk-Steuerung Z80-ECB/F

#### 7.1 Übersicht

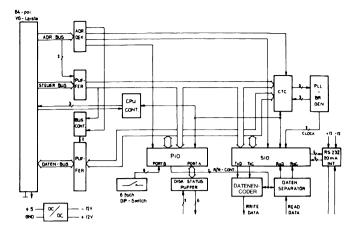

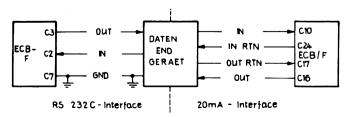

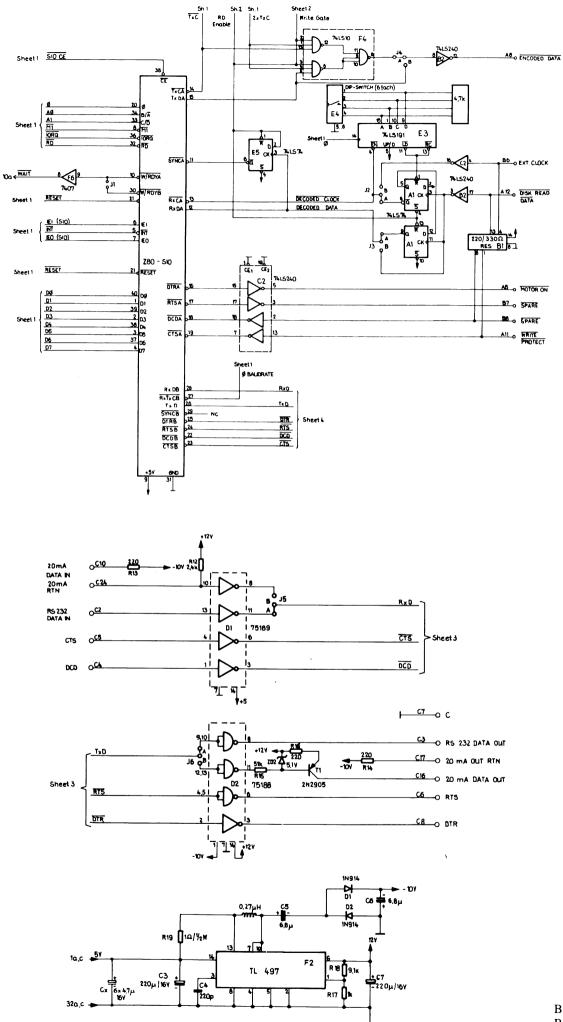

Die Baugruppe ECB/F ist eine universell einsetzbare Serienein- bzw. Ausgabeeinheit. Sie ist kompatibel zur Z80-ECB-Baugruppenserie im Einfach-Europaformat und vereint die Leistungsfähigkeit von drei Z80-Peripheriebausteinen, nämlich des Z80-CTC, des Z80-PIO und des Z80-SIO. Zwei separate Voll-Duplex-Kanäle erlauben serielle Datenübertragung in nahezu allen bekannten asynchronen und synchronen Verfahren. Über den Z80-CTC und einen PLL-Frequenzsynthesizer sind alle gebräuchlichen Baudraten für den Asynchronkanal bzw. alle Übertragungsraten von 0—550 kbit/s für den Synchronkanal programmierbar.

Die Baugruppe ermöglicht den unmittelbaren Anschluß von bis zu acht hardsektorierten Floppy-Disk-Laufwerken verschiedener Größen und Speicherkapazitäten, sowie asynchron arbeitenden Datenendgeräten mit genormten RS232C- oder 20 mA Current Loop-Schnittstellen. Durch den Einsatz des Z80-SIO ist die ECB/F in hervorragender Weise auch für Rechner-Rechnerkopplungen geeignet. International genormte Übertragungsprozeduren wie SDLC und HDLC werden vom Z80-SIO abgehandelt.

Zum Betrieb der Baugruppe genügt eine einzige Versorgungsspannung von +5 Volt. Die Betriebsspannungen für das RS 232 C-Interface werden durch Gleichspannungswandler auf der ECB/F erzeugt.

Eine leistungsfähige, in zwei Stufen implementierte Floppy-Disk Betriebssoftware steht ebenfalls zur Verfügung. Zusammen mit der Zentragbaugruppe ECB/C stellt die ECB/F somit das Kernstück eines Floppy-Disk basierenden Anwendersystems dar.

#### 7.2 Eigenschaften und Hardwarekomponenten

Die Baugruppe enthält folgende Funktionseinheiten:

- a) CPU-Interface

- Schmitt Trigger Pufferung sämtlicher Bussignale

- Adreßdekoder für CTC, PIO und SIO

- Look Ahead Logik für Interruptprioritätssteuerung (Daisy Chain)

- 64-poliger Busstecker nach DIN 41612

- b) SIO-Synchronkanal (Floppy Disk Interface)

- Voll programmierbarer PLL-Frequenzsynthesizer zur Erzeugung der Übertragungsrate (2 CTC-Kanäle)

- Programmierbarer, rein digitaler Datenseparator mit 16 Zeitkonstanten

- Datenencoder zur Daten-/Clock-Gemischerzeugung

- Diskstatussignale über Z80-PIO

- Schmitt Trigger Pufferung aller Ein-/Ausgänge

- c) SIO-Asynchronkanal

- Voll programmierbare Baudratenerzeugung von 50—38 400 Baud (1 CTC-Kanal)

- RS 232C und 20 mA Current Loop Interface

- Gleichspannungswandler für ±12 Volt

- 6 Modem Signale im RS 232C Pegel

- d) Sonstiges

- 6 DIP Schalter (über PIO) zur Programmierung von Systemvariablen

- Steckbare Jumper zur Umstellung des Synchronkanals an andere Peripherie

- I/O seitig drei Standardstecker zum Anschluß der Peripheriegeräte

#### 7.2.1 CPU-Interface

Sämtliche Bussignale der ECB/F sind über die 64-polige VG-Messerleiste entsprechend der PIN-Belegung der übrigen Z80-ECB-Baugruppen herausgeführt (siehe Abschnitt 1).

Bild 7—1 zeigt das Blockschaltbild der Baugruppe

Bild 7—1: Blockschaltbild der ECB/F

Alle Leitungen sind gepuffert und stellen pro Eingang nicht mehr als eine LS TTL-Last (≜ 0,25 mA bei LOW) dar. Schmitt Trigger Bausteine erhöhen hierbei die Störsicherheit. Alle Ausgänge erlauben den Anschluß von kapazitiv hochbelasteten Bussystemen.

Die Leitungen WAIT und INT sind Open Collector-Ausgänge ohne Pull up Widerstände, da diese bereits auf der Zentralbaugruppe ECB/C vorhanden sind. Eine "Look ahead Logik" (Baustein F5: 74LS08) sorgt für die schnelle Durchschaltung der Z80-Interruptprioritätssteuerung (Daisy Chain). Die ECB/F-interne Priorität ist: CTC, SIO, PIO.

#### 7.2.2 Adressierung

Die Adressierung der Bausteine Z80-CTC, Z80-PIO und Z80-SIO erfolgt über das Dekoderprom B6 (HM7611). Da die Floppy-Disk-Treibersoftware feststehende I/O-Adressen verwendet, wurde darauf verzichtet, einstellbare Adressierung zu ermöglichen. Das Dekoderprom dekodiert aus den Adressen A2—A7 folgende I/O-Adressen:

|         |               | <b>A</b> 7 | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | <b>A</b> 3 | <b>A</b> 2 | Αl | <b>A</b> 0 |  |

|---------|---------------|------------|------------|------------|------------|------------|------------|----|------------|--|

| Z80-CTC | $\rightarrow$ | 0          | 0          | 0          | ()         | 1          | 1          | X  | X          |  |

| Z80-SIO | $\rightarrow$ | 0          | 0          | 0          | 1          | 1          | 1          | X  | X          |  |

| Z80-PIO | $\rightarrow$ | ()         | 0          | 1          | 0          | 1          | l          | X  | X          |  |

Es liefert außerdem ein  $\overline{I/O\text{-}DEC}$  Signal, welches immer dann aktiv ist, wenn einer der drei Z80-Bausteine auf der ECB/F adressiert wird. Dieses Signal wird zur Datenbussteuerung benötigt.

Die Adreßleitungen A0 und A1 sind in der üblichen Weise mit den Port- bzw. Channel-Select-Eingängen von PIO, SIO und CTC verbunden.

Tabelle 7.1 enthält sämtliche I/O-Adressen der ECB/F in hexadezimaler Form.

| CTC-KANAL 0       | 0CH |

|-------------------|-----|

| CTC-KANAL 1       | 0DH |

| CTC-KANAL 2       | 0EH |

| CTC-KANAL 3       | 0FH |

| SIO PORTA DATA    | 1CH |

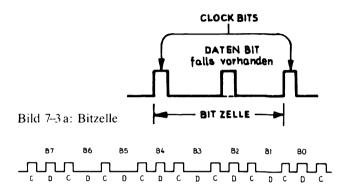

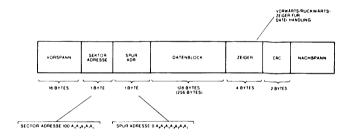

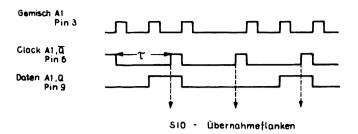

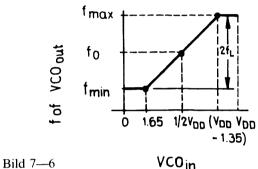

| SIO PORTB DATA    | 1DH |