# Olympia Service

The Better Service The Higher Reputation The More Favorable Sales

# PEOPLE

Funktionsbeschreibung Description of function Description de fonctionnement Descripción de Funciones

**Olympia International**

Olympia Werke AG · Wilhelmshaven · Central Service Department · Tel. 0 44 21 / 781

## CONTENT

|     |      |      |            |      |     |      |    |     |    |    |   |    |   |   |   |   |   |   |   |   |   |   | Page  |

|-----|------|------|------------|------|-----|------|----|-----|----|----|---|----|---|---|---|---|---|---|---|---|---|---|-------|

| 1.  | GENE | RAL  |            | ••   | •   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 002   |

| 2.  | CPU  | AND  | PE         | RIP  | HEI | RAI  | S  |     | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1000  |

| 3.  | MEMO | RY   | •          | ••   | •   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 10 10 |

| 4.  | KEYB | OAR  | D          | • •  | ٠   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1014  |

| 5.  | CRT  | CON  | IROI       | ն    | •   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1027  |

| 6.  | FDD  | CON  | <b>FRO</b> | ն    | •   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1033  |

| 7.  | SERI | AL   | INTI       | ERF  | ACI | Ξ    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1039  |

| 8.  | PARA | LLE  | L II       | NTE  | RFZ | ACE  | E  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1044  |

| 9.  | TIME | R C  | ONTI       | ROL  | LEI | ર    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1051  |

| 10. | POWE | R S  | UPPI       | ΓX   | UN  | IT   |    | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 1053  |

| 11. | MAIN | ITEN | ANC        | E N  | AN  | IU A | ٩L | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 2000  |

| 12. | TEST | P RC | GRI        | MA   | •   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 2038  |

| 13. | FLOP | PY   | DISE       | K D  | RIV | VE   | TE | CAC | :- | FD | - | 55 | • | • | • | • | • | • | • | • | • | • | 2100  |

| 14. | MONI | т Or |            | •••  | •   | •    | •  | •   | •  | •  | • | •  | • | • | • | • | • | • | • | • | • | • | 2150  |

| 15. | ERSA | TZTE | SILE       | : PI | EOP | LE   | •  | •   | -  |    | • | •  | - | • | • | • | • | • |   | • | • | • | 2180  |

•

,

1. GENERAL

#### 1. GENERAL

#### 1.1 General Information

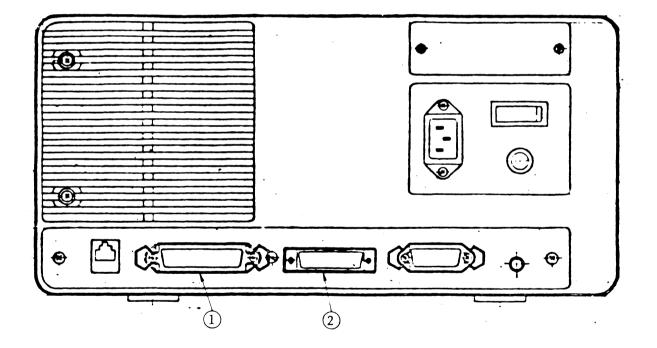

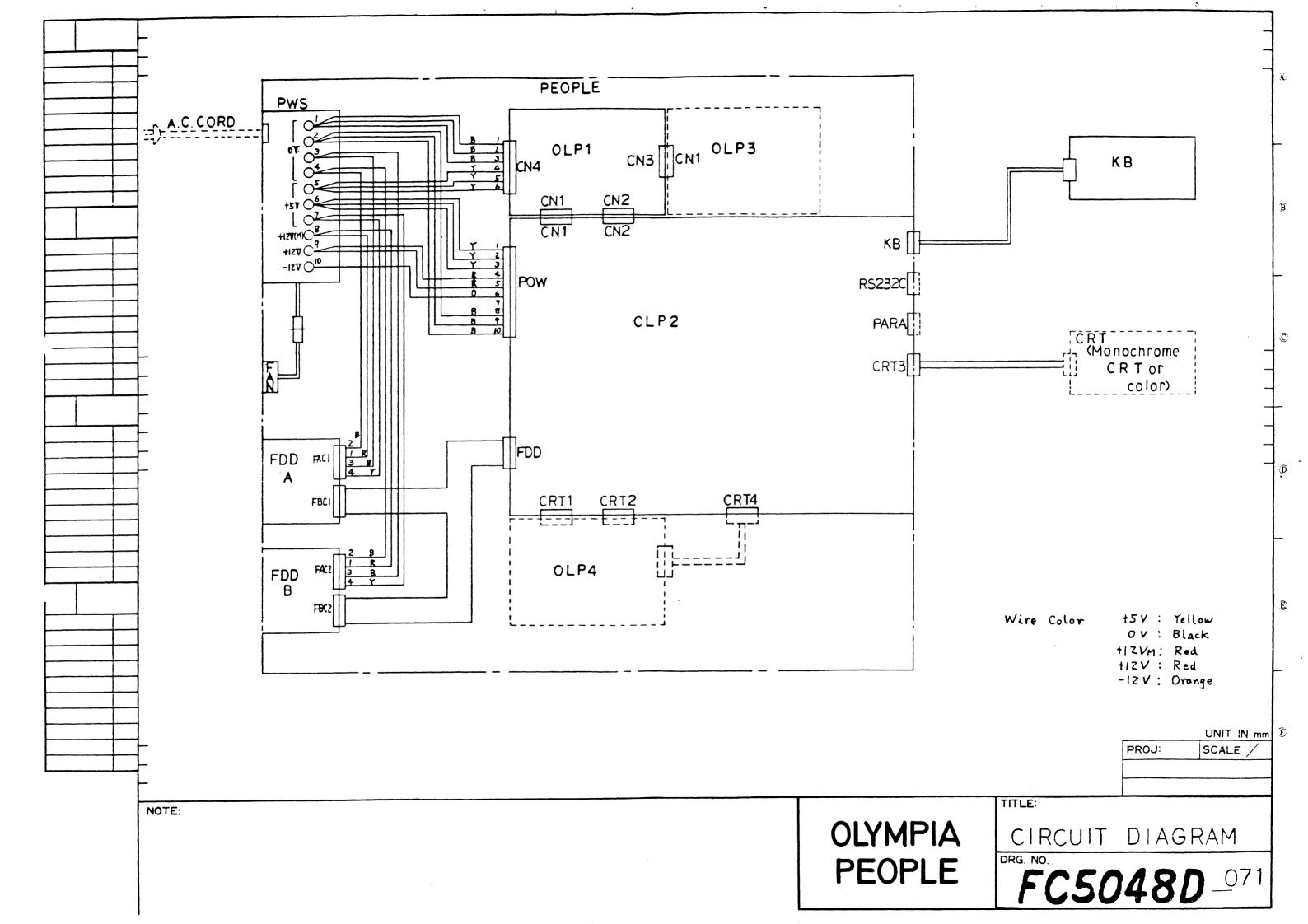

People is based on a 8086 CPU with basically a total of 264 KB of RAM-Memory, two Floppy Disk Drives, a typewriter style keyboard, several interfaces and various options like, disk extension, RS232C-extension, GPIB-interface, memory extension.

It's designed to be a field-upgradable system. It basically consists of three units: the main unit, the keyboard, the CRT, extensions may be housed separately. People is designed for applications such as data processing, office accounting and word processing. It also can handle educational, scientific, technical problems and also process control applications. It is designed to be used by untrained people. There are no special installation requirements, it operates under the following conditions:

| - | Operating temperature      | +5°C to +40°C          |

|---|----------------------------|------------------------|

| - | Humidity                   | 20% to 80%             |

|   |                            | (without condensation) |

| - | Storage temperature        | -22°C to +47°C         |

| - | Resistance against         | 5KV                    |

|   | electrostatical discharges |                        |

|   | (Condenser method)         |                        |

#### 1.2 Configuration

PEOPLE has a 16-bit CPU (8086), with 256 KW RAM as the main memory and it is provided with a boot ROM (2732A) for program loading when power is switched on or REST operation, this having a capacity of up to 4Kwords. The peripheral control elements of the CPU include timer controller 8253 and interrupt controller 8259A. The following can be connected to PEOPLE:

- (1) Floppy disk drive unit (5 1/4 inch type) 2 decks

- (2) Micro disk

- (3) CRT display (monochrom)

- (4) CRT display (color)

- (5) Printer (parallel I/F) Centronics specification

- (6) RS232C I/F 3 channels

- (7) Keyboard

- (8) GPIB I/F

#### 1.3 BUS CONNECTION

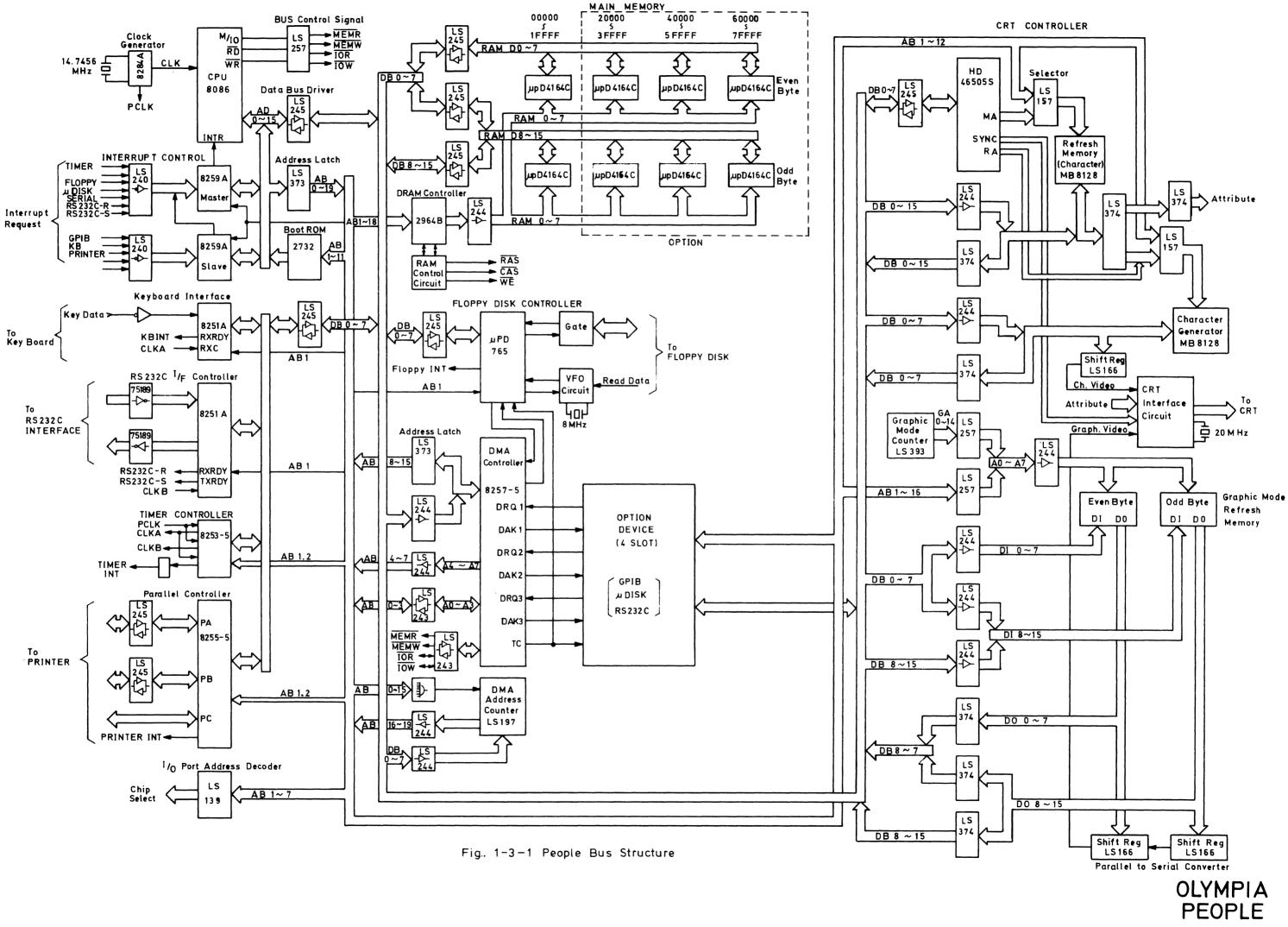

The CPU and the peripheral devices are connected together via data and address buses. The bus connection for PEOPLE appears in Fig. 1.3.1.

Appendix The installation and environmental stipulations

The system contains a variety of measures designed to ensure the serviceability at all times, with particular attention being paid to the influence of factors such as power cuts and defects due to static discharge.

The installation and environmental stipulations listed have been compiled so as to ensure the maximum possible freedom of interference from external sources.

Connection to the local power supply

The design of the machine corresponds with the international radio interference suppression regulations.

However, due to the fact that not all electrical appliances on the market comply with such regulations, the system should only be connected to circuits to which other appliances are connected which comply with such regulations. Within the Federal Republic of Germany, such appliances bear the interference suppression symbol of the VDE or the FTZ test number of the Federal Postal Authorities.

Variations of the power supply

In order to ensure the correct functioning of the system, the voltage and frequency of the power supply to which the system is connected should not exceed the following variations :

Voltage : + 10 - 15% Frequency : +/- 1%

The system is not affected by brief voltage variations up to a maximum of 2000 V, pulse widths of up to 300 ns or rise times of up to 5 ns.

In the event of the possibility of variations of the voltage occuring due to the connection of other appliances, either a voltage regulator or supplementary filter should be incorporated in the circuit. Point of installation

The system should be set up at spots not subject to vibration, dampness and dust, as well as away from direct sunlight and/or radiators.

In connection with the above, the following stipulations must be complied with :

The angle of inclination of the system should not exceed  $2^{\circ}$

Vibration during operation should not exceed 10 - 100 Hz 0.2 g

Vibration during transit should not exceed 10 - 100 Hz 2 g

Environmental temperature :

| In operation :     | between 5 <sup>°</sup> and 40 <sup>°</sup> C      |

|--------------------|---------------------------------------------------|

| In storage :       | between - 22 <sup>°</sup> and + 47 <sup>°</sup> C |

| Relative humidity: | between 20 and 80 %                               |

On no account should the ventilation slots of the system be covered in whatever manner, either by the documents or by being partially masked by office furniture.

Those cables connected externally to the system must be protected against damage and as well as being arranged to prevent possible tripping.

Electrostatic charging

Factors which influence electrostatic charging are the relative humidity, the material of the floor covering, wall to wall carpeting, and the soles of shoes, the material of the cushioning of chairs and the dress of the operator.

The systems are protected against defects brought about by electrostatic discharge within normal limits.

# 2. CPU AND PERIPHERALS

# 2. CPU AND PERIPHERALS

2.1 CPU

PEOPLE uses the 8086 CPU.

#### 2.1.1 Use

| (1) | Operation clock | 4.9152 MHz                  |

|-----|-----------------|-----------------------------|

| (2) | Mode            | Minimum mode                |

|     |                 | Usually the RAM Read/write  |

|     |                 | operations involve one wait |

|     |                 | each. Then CPU Cycle time   |

|     |                 | is l µS.                    |

## 2.1.2 The CPU

2.2 Clock Generator 8284A

.

#### 2.4 Reset Circuit

This circuit outputs reset signals if the reset switch behind the main cabinet is pressed. When the reset circuit becomes active, the system program is read from the system disk, if it is mounted on floppy disk drive, and is then stored to the memory. This is known as initialization.

#### 2.5 Bus Control Signal

Bus control signals include the memory read signal (MEMR), memory write signal (MEMW), I/O read signal (IOR), and I/O write signal (IOW). These signals control the timing of the opening and closing of the data bus for memory read/write, and I/O read/write operations.

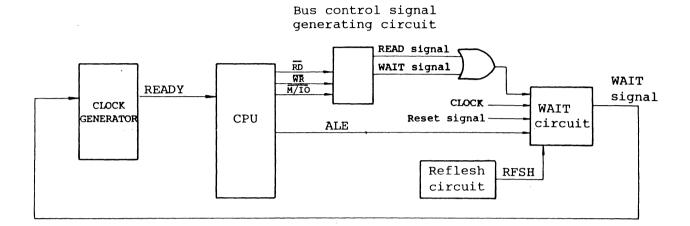

#### 2.6 WAIT CIRCUIT

When the CPU accesses memory or the I/0, this circuit generates the Wait signal to match CPU operation speed with the memory or I/0 operation speed.

#### 2.6.1 Circuit Configuration

Fig. 2.6.1 Wait circuit

Operating speed of the I/O control IC is slower than the CPU'S. Again, because of the refresh operation, the memory cycle time is slower than the CPU access time. When accessing the bus, therefore, the CPU requires one wait cycle.

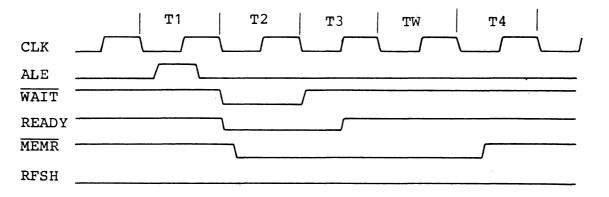

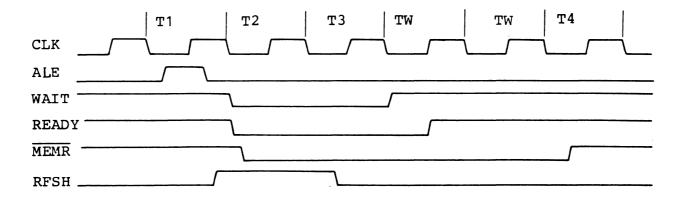

#### 2.6.2 RAM Access Timing

The main memory uses the dynamic RAM IC, making it necessary for the refresh circuit to refresh RAM periodically. The main memory is refreshed every time after a CPU memory access. However, if the next CPU memory access does not take more than  $3.5\mu$  sec, the next refresh cycle starts. In this case, CPU memory access and refresh operation may be over lapped. (Fig. 2.6.3). 2.6.2 Time Chart

(1) If there is no contention between memory Ready/Write and Refresh operations

Fig. 2.6.2

(2) If there is contention between memory Read/Write

and Refresh operations

2.7 Interrupts

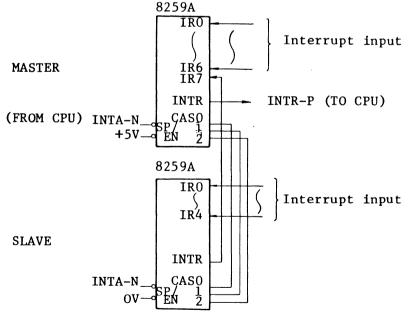

The interrupt signals are fed to the CPU via interrupt controller 8259A. When the CPU receives the interrupt signals, it sends the corresponding response signal (INTA) to 8259A.

When 8259A receives INTA, it sends an interrupt vector signal to CPU, according to the factor that caused the interrupt signal.

#### 2.7.1 Interrupt Controller 8259A

#### 2.7.2 Block Diagram

PEOPLE uses two 8-level input interrupt controller 8259A for reception of 12-level interrupt inputs.

Fig. 2.7.1 Interrupt circuit block diagram

# 2.7.3 List of Interrupts

.

.

.

The factors causing interrupts in PEOPLE are listed in Table 2.7.1 according to their priorities.

| r             | ·              |                  | 1             | []             |                    |

|---------------|----------------|------------------|---------------|----------------|--------------------|

| Pri-<br>ority | Signal<br>name | Descripiton      | Pri-<br>ority | Signal<br>name | Description        |

| 1             | TIMER          | Timer interrupt  | 7             | CCUS           | RS232C send        |

|               |                |                  | 8             | GPINT          | GPIB interface     |

| 3             | FDINT          | Floppy disk      | 9             | KBINT          | KB interface       |

| 4             | μ <b>i nt</b>  | Micro disk       | 10            | PINT           | Parallel interface |

| 5             | CINT           | Serial interface | 11            | INTO           | Reserved           |

| 6             | CCUR           | RS232C receive   | 12            | INTI           | Reserved           |

Table 2.7.1 List of interrupts

#### 2.8 I/O Port

· ,

The I/O ports in CPU are defined as follows:

| Port<br>No. | Device       | Output                     | Input                  |

|-------------|--------------|----------------------------|------------------------|

| 18H         | 8259A master | •                          |                        |

| lah         | 11           | ١                          |                        |

| 14H         | 8259A slave  |                            |                        |

| 16H         | 11           |                            |                        |

| 20H         | 8257         | Channel 0 DMA address      |                        |

| 22H         | 11           | Channel 0 Terminal counter |                        |

| 24H         | 11           | Channel l DMA address      |                        |

| 26H         | 11           | Channel l Terminal counter |                        |

| 28H         | 11           | Channel 2 DMA address      |                        |

| 2AH         | 11           | Channel 2 Terminal counter |                        |

| 2CH         | 11           | Channel 3 DMA address      |                        |

| 2EH         | 11           | Channel 3 Terminal counter |                        |

| 30н         | 11           | Mode setting               |                        |

| 40H         | 8255         | Data bus → port A          | Port A → device        |

| 42H         | "            | Data bus → port B          | Port B → device        |

| 44H         | 11           | Data bus 🗲 port C          | Port C + device        |

| 46H         | 11           | Control word               |                        |

| 48H         | 8253         | Loading counter 0          | Reading from counter 0 |

| 4AH         | 11           | Loading counter l          | Reading from counter l |

| Port<br>No. | Device   | Output                                      | Input                     |

|-------------|----------|---------------------------------------------|---------------------------|

| 4CH         | 11       | Loading counter 2                           | Reading from<br>counter 2 |

| 4EH         | Ħ        | Control word                                |                           |

| 54H         | 8251     |                                             | KB receive data           |

| 56H         | 11       | Control data                                | Status data               |

| 5СН         | . U      | RS232C send data                            | RE232C receive<br>data    |

| 5EH         |          | Control data                                | Status data               |

| 64H         | µPD765   |                                             | Status data               |

| 66H         | 11       | Command data                                |                           |

| 6CH         | HD46505S | Address resister                            |                           |

| 6EH         | 11       | Data                                        | Data                      |

| 70H         |          | Channel 0 DMA address,<br>4 high order bits |                           |

| 72H         |          | Channel l DMA address,<br>4 high order bits |                           |

| 74H         |          | Channel 2 DMA address,<br>4 high order bits |                           |

| 76H         |          | Channel 3 DMA address,<br>4 high order bits |                           |

| 7CH         |          | *1                                          | RS232C status data        |

| 7AH         |          |                                             |                           |

| 80H         | RESERVED |                                             |                           |

| 5           |          |                                             |                           |

| 8FH         |          |                                             |                           |

.

• •

\*1 2° = 1 Timer interrupt reset

2 = 1 Graphic mode 2 = 0 Character mode

2 = 1 CRT display inhibit

2 = 1 CRT color mode 2 = 0 Monochrome mode

Table 2.7.1 Input-output port list

#### 2.9 DMA

#### 2.9.1 DMA Using Device

| (1) | Floppy disk interface        | Channel | 0 |

|-----|------------------------------|---------|---|

| (2) | GPIB interface (option)      | Channel | 1 |

| (3) | Microdisk interface (option) | Channel | 2 |

#### 2.9.2 DMA Controller

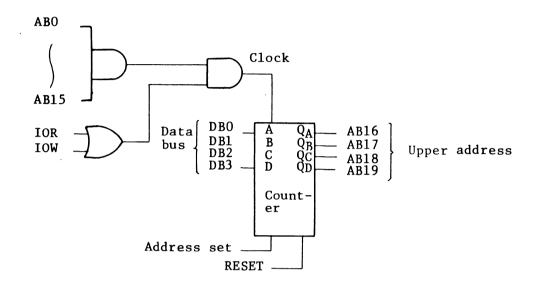

#### 2.9.3 Address counter

The DMA controller 8257-5 has only 16-bit address counter. As a result, it can specify addresses within a 64KB memory space. On the other hand, 8086 can access a memory space of up to 1MB. Thus, a 4-bit counter must be added to 8257-5 to achieve a total of 20 bits. For each DMA channel, a 4-bit address counter is added, making it possible to specify any address within the 1MB memory address range.

Fig. 2.9.1 Address counter circuit

ę.

3. MEMORY

#### 3. MEMORY

#### 3.1 TYPE, CAPACITY

.

PEOPLE uses the following memory:

| Туре                                   | IC              | Capacity   | Access time |

|----------------------------------------|-----------------|------------|-------------|

| Boot ROM                               | 2732            | 4 kW       | 350 nS      |

| Main Memory                            | μ <b>PD4164</b> | Max 256 kW | 200 nS      |

| Character generator                    | MB8128          | 4 kB       | 100 nS      |

| Refresh memory<br>(for character mode) | MB8128          | 2 kW       | 100 nS      |

| Refresh memory<br>(for graphic mode)   | MB8264          | 64 kW      | 100 nS      |

7

#### 3.2 MEMORY MAP

| 00000н           |                                   |          |

|------------------|-----------------------------------|----------|

| 0000011          | Basic                             |          |

| 20000            |                                   |          |

| 20000H           | Option                            |          |

| 40000            | Main Memory                       |          |

| 40000H           | Option                            |          |

|                  |                                   |          |

| 60000н           | Option                            |          |

|                  |                                   |          |

| 80000H           | Graphic Option (Blue)             |          |

| A0000H           | " (Green)                         |          |

| С0000н<br>Е0000н | Graphic Basic (Red)               |          |

| E0000H<br>E4000H | CRT Charactor Mode Refresh Memory |          |

| E6000H           | CRT " Charactor Generator         |          |

| FEOOOH           |                                   | Reserved |

|                  | Boot ROM                          |          |

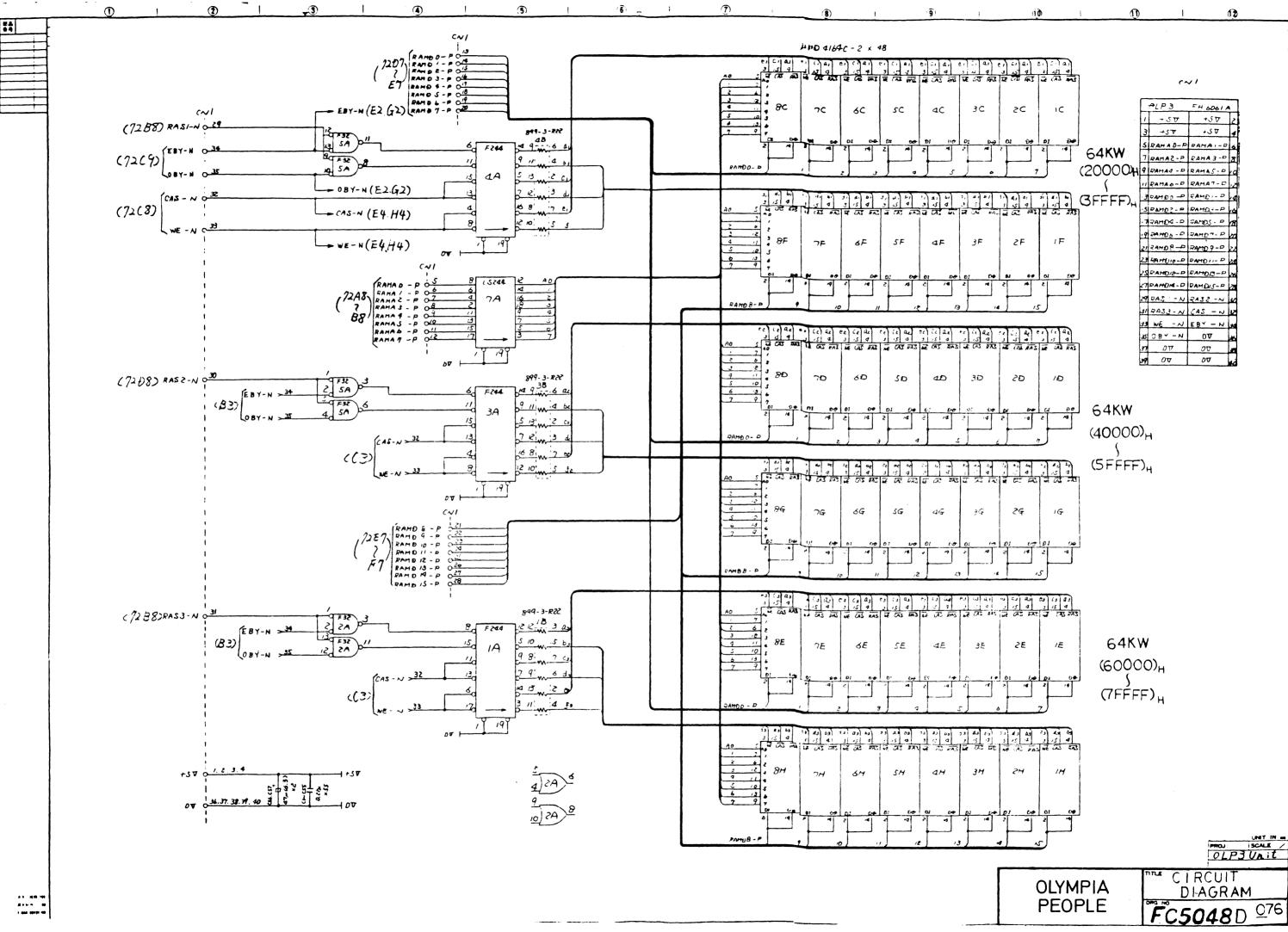

# 3.3 MAIN MEMORY

Component of the main memory is a dynamic RAM IC having a capacity of 64K x l bits.

·

The OLP1 unit can be provided with a 128KByte memory and OLP3 with 128KBytes. The rest, that is 256 K Bytes, is provided through IC socket.

.

#### 3.4 PRINCIPAL FEATURES OF DYNAMIC RAM

- (1) Type  $\mu$  PD4164C-2 or equivalent

- (2) Access time 200 nS

- (3) Refresh cycle Max 2mS

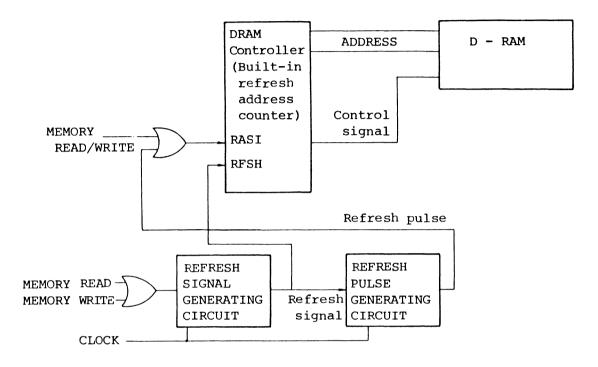

#### 3.5 DYNAMIC RAM CONTROLLER

The dynamic RAM controller is Am2964B. The main functions of this controller are detailed below:

- Dividing the 16-bit address bus line into 8 bits each, and supplying these as, respectively, the ROW and the Column addresses to the dynamic RAM.

- (2) Controlling dynamic RAM refresh in response to external refresh signals, using a built-in refresh counter.

- (3) Dynamic RAM controller 2964B

#### 3.6 REFRESH CIRCUIT

Except during RAM Read or Write operations, the refresh circuit controls refreshing of the dynamic memory to prevent erasing of the RAM stored data. Refresh signals are output by the refresh circuit, synchronizing them to the CPU DRAM access.

#### 3.6.1 Circuit Block Diagram

Fig. 3.6.1 Refresh circuit block diagram

#### 3.6.2 Time Chart

Unless the CPU is performing the Read/Write operation, the memory is refreshed successively at an interval of about 4  $\mu$ s. When the CPU issues the Read or the Write signal, refreshing operation is stopped.

It starts again when the CPU ends the Read or Write operation.

.

4. KEYBOARD

#### 4. KEYBOARD

#### 4.1 KEYBOARD INTERFACE (KB)

A curled cord connects the PEOPLE's main cabinet and the keyboard. The interface specifications are listed below:

#### 4.1.1 Specifications

| Terminal<br>number | Signal name | Function           |  |  |  |  |

|--------------------|-------------|--------------------|--|--|--|--|

| 1                  | RDATA-N     | Key input data     |  |  |  |  |

| 2                  | GND         | Signal ground      |  |  |  |  |

| 3                  | RESET-N     | Keyboard reset     |  |  |  |  |

| 4                  | GND         | Signal ground      |  |  |  |  |

| 5                  | GND         | Power source (0V)  |  |  |  |  |

| 6                  | FG          | Frame ground       |  |  |  |  |

| 7                  | + 5V        | Power source (+5V) |  |  |  |  |

| 8                  | + 5V        | Power source (+5V) |  |  |  |  |

(1) Signal names and terminal connections

Table 4.1.1 Keyboard connection

(2) Method of sending

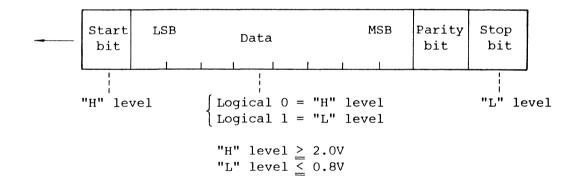

The key input data is sent from the keyboard to the mainframe controller according to the following specifications:

- (i) Transmission rate 1200 BPS

- (ii) Synchronization method Start-Stop

- (iii) Transmission unit 11 bits

1 (start bit) + 8 (data bits) +

1 (even parity bit) + 1 (stop bit)

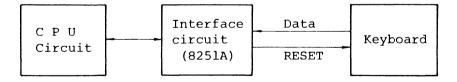

(3) Connection block diagram

When 8251A receive 1 character (8 bits) of the serially sent keyboard data, it stores the data in the buffer register, and notifies the CPU (8086) about it by issuing an interrupt. Then the CPU receives the 8-bit keyboard data from the 8251A buffer.

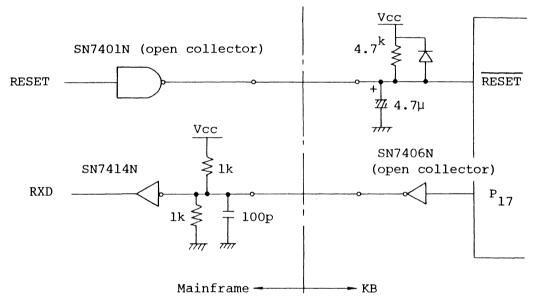

#### 4.1.2 Interface Circuit

Fig. 4.1.1 KB Interface

#### 4.2 MAINFRAME CONTROL CIRCUIT

#### 4.2.1 Controller

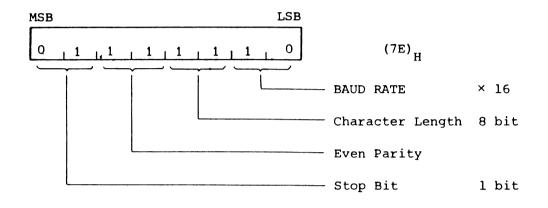

The keyboard controller used for the mainframe is 8251A. This is a serial data communication controller controlling data send and receive operations. The operation modes in 8251A is programable. The mode command, conforming to the keyboard interface, is (7E)<sub>u</sub>.

The transmission rate is determined by (i) the frequency of the clock pulses connected to the R×C terminal of 8251A, and (ii) Baud rate set for the mode commands issued to 8251A.

Frequency of the clock\* sent to the R×C terminal is 19.2kHz, Baud rate setting being ×16. Transmission rate, therefore, is given by the following:

19.2 kHz  $\div$  16 = 1.2 kHz

\* The clock signal sent to the R×C terminal for the keyboard interface controller (8251A) is generated by the timer controller (8253). For the method of generation, see 9.3.

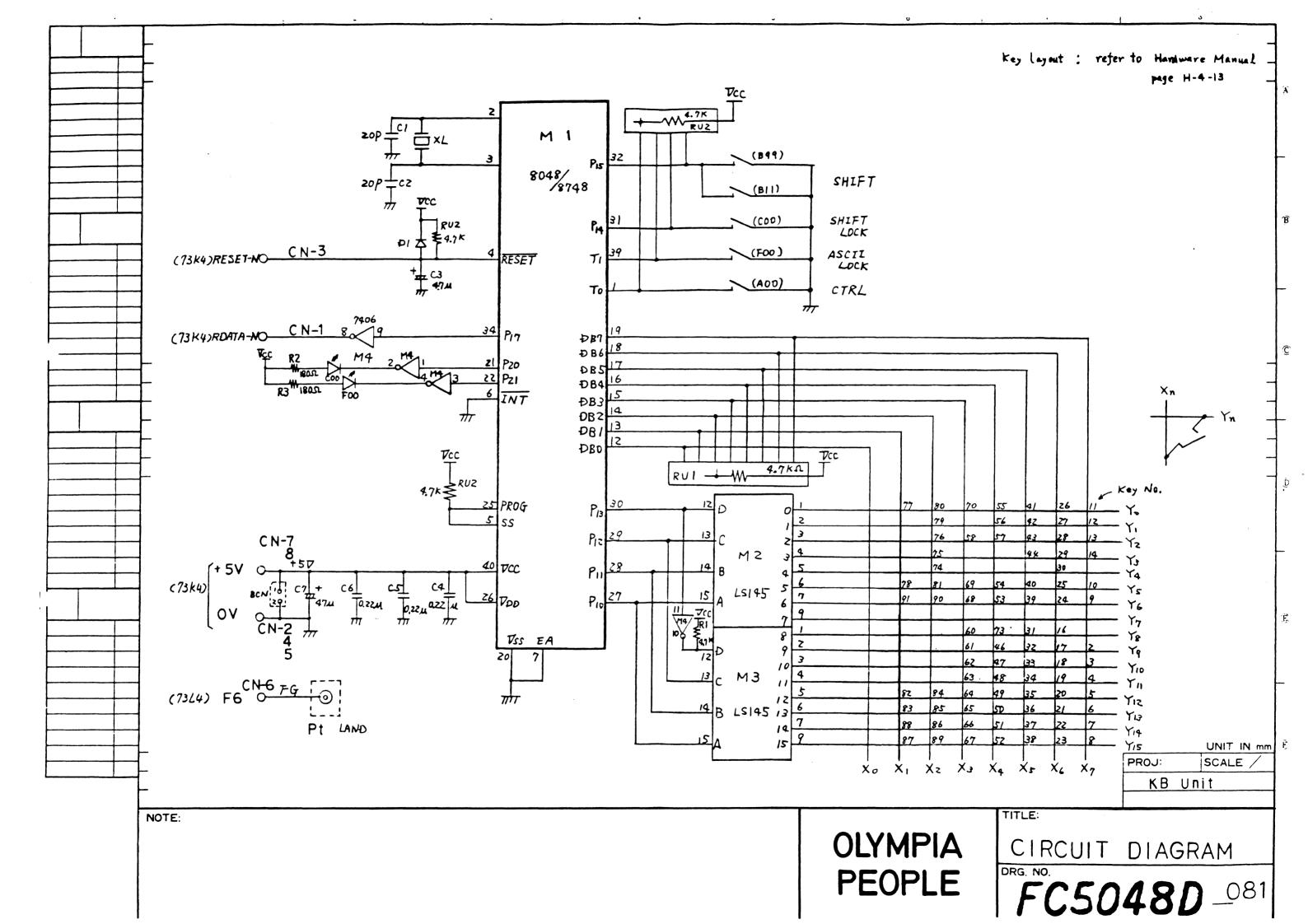

#### 4.3 KEYBOARD CONTROL CIRCUIT

#### 4.3.1 Overview

The keyboard uses a 1-chip microcomputer (8048). This microcomputer controls monitoring and encoding of the key inputs, and sending of the codes to PEOPLE mainframe.

#### 4.3.2 8048

Microcomputer 8048 incorporates ROM and RAM. ROM stores the key code encode tables and the control program. The control program controls all the operations. RAM is used as the buffer for storing the input key codes. For its external interface, the microcomputer uses a 16-bit I/O port, to which two test bits are added. Furthermore, it has an 8-bit data bus. Of the 16-bit input port,  $P_{10} \sim P_{13}$  (4bits) are used for row address of key matrix,  $P_{14}$  and  $P_{15}$  (2 bits) for shift control key, and  $P_{17}$  for send data output for PEOPLE mainframe. Test bits  $T_0$  and  $T_1$  are for ASCII lock key and CTRL key inputs. Data bus bits DB<sub>0</sub>  $\sim$  DB<sub>7</sub> are used for key matrix column data input,

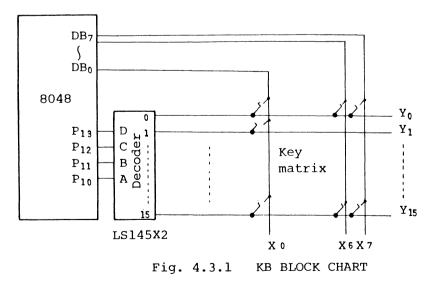

#### 4.3.3 Key Input Control

The 8048 output key matrix row addresses cyclically thus: 0, 1, 2, ...., 15, 0, 1. The row address output at  $P_{10} \, \ldots \, P_{13}$  is decoded by the decoder driver (SN74LS145N), one line (Y<sub>1</sub>) alone being selected from out of the 16 lines (Y<sub>0</sub>...Y<sub>15</sub>). One of the terminals of a maximum of eight keys is connected to a line. The other terminal, divided into eight columns is connected to the data bus of 8048 (DB<sub>0</sub>  $\sim$  DB<sub>7</sub>). If 8048 selects a line, status of a maximum of eight keys connected to the line appears to the data bus. Since 8048 reads this status, if it sequentially outputs the line addresses corresponding to lines 0  $\sim$  15 at P<sub>10</sub>  $\sim$  P<sub>13</sub>, and reads the contents of the data bus, it can find out the status of the keys connected to the 16 row 8 column matrix.

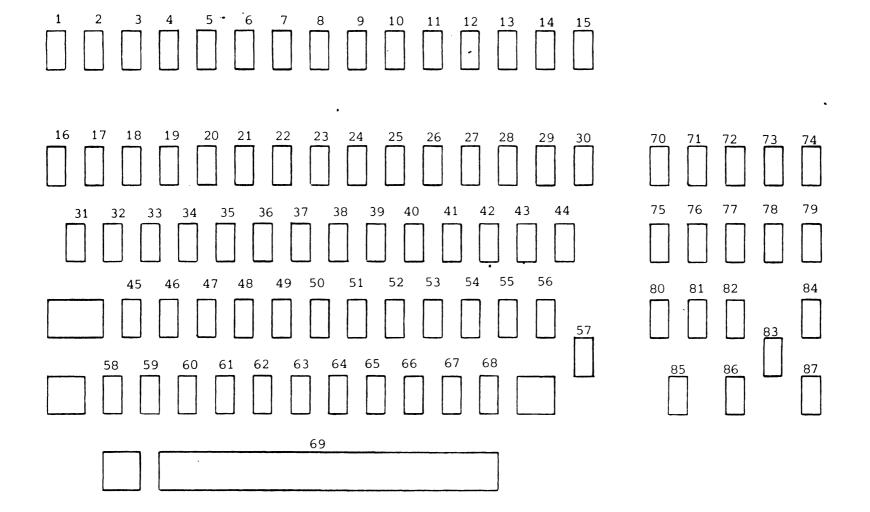

#### 4.3.4 Key Input Code

Depending on its position, each key on the keyboard has an independent code. The key codes are shown in 4.3.6.

In its ROM, 8048 stores a table of these key codes. As described in 4.3.3, 8048 retrieves the code corresponding to this key from the table when the key is pressed, and stores it in the buffer.

#### 4.3.5 Key Code Send Operation

From the buffer memory, 8048 sends the key codes to the CPU (PEOPLE mainframe) as a series of bits. Using the stored program, it sends data to conform to the specifications given in 4.1.1 (2). Terminal P<sub>17</sub> of 8048 is the data outlet.

NOTE: The key codes are sent to the CPU as shown in table 4.3.1. These, however, are converted into other codes by the system program.

#### 4.3.6 Key Codes

The key positions and the corresponding codes are shown below. For the key arrangement, see Fig. 4.3.6.

| Key<br>No. | Code                   | Key<br>No. | Code              | Key<br>No. | Code     | Key<br>No. | Code            |

|------------|------------------------|------------|-------------------|------------|----------|------------|-----------------|

| 1          | 8E/8F <sup>*</sup>     | 24         | 38/28/28          | 47         | 53/73/13 | 70         | 2F/3F/2F        |

| 2          | A4                     | 25         | 39/29/29          | 48         | 44/64/04 | 71         | SHIFT *4        |

| 3          | 90                     | 26         | 30/20/20          | 49         | 46/66/06 | 72         | CTRL *5         |

| 4          | 91                     | 27         | 2D/3D/2D          | 50         | 47/67/07 | 73         | A5              |

| 5          | 92                     | 28         | 5C/7C/1C          | 51         | 48/68/08 | 74         | В7              |

| 6          | 93                     | 29         | A0                | 52         | 4A/6A/0A | 75         | В8              |

| 7          | 94                     | 30         | A3                | 53         | 4B/6B/0B | 76         | В9              |

| 8          | 95                     | 31         | Al                | 54         | 4C/6C/0C | 77         | 84//C4 *6       |

| 9          | 96                     | 32         | 51/71/11          | 55         | 3B/2B/2B | 78         | 83//C3          |

| 10         | 97                     | 33         | 57/77/17          | 56         | 3A/2A/2A | 79         | В4              |

| 11         | 98                     | 34         | 45/65/05          | 57         | 5D/7D/1D | 80         | В5              |

| 12         | 99                     | 35         | 52/72/12          | 58         | A2       | 81         | B6              |

| 13         | 9A                     | 36         | 54/74/14          | 59         | SHIFT *4 | 82         | AD              |

| 14         | 9B                     | 37         | 59/79/19          | 60         | 5F/7F/1F | 83         | 85//C5          |

| 15         | 9C                     | 38         | 55/75/15          | 61         | 5A/7A/1A | 84         | Bl              |

| 16         | 5E/7E/1E <sup>**</sup> | 39         | 49/69/09          | 62         | 58/78/18 | 85         | В2              |

| 17         | 31/21/21               | 40         | 4F/6F/0F          | 63         | 43/63/03 | 86         | В3              |

| 18         | 32/22/22               | 41         | 50/70/10          | 64         | 56/76/16 | 87         | A7              |

| 19         | 33/23/23               | 42         | 40/60/00          | 65         | 42/62/02 | 88         | 81∥C1           |

| 20         | 34/24/24               | 43         | 5B/7B/1B          | 66         | 4E/6E/0E | 89         | в0              |

| 21         | 35/25/25               | 44         | A6                | 67         | 4D/6D/0D | 90         | AE              |

| 22         | 36/26/26               | 45         | SHIFT ***<br>LOCK | 68         | 2C/3C/2C | 91         | 82 <i>//</i> C2 |

| 23         | 37/27/27               | 46         | 41/61/01          | 69         | 2E/3E/2E |            |                 |

All codes are in hexadecimal.

Table 4.3.1 KEY CODE TABLE

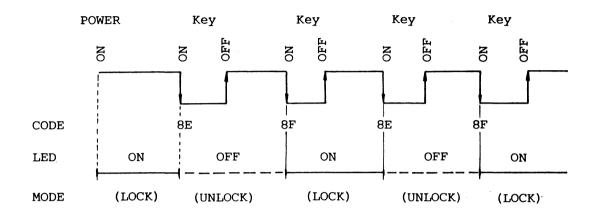

# NOTE: \* Key No. 1 is the ASCII lock key codes as shown below:

Fig. 4.3.2 ASCII LOCK OPERATION

\*\* Keys marked A/B/C output three codes depending on the shift status and the status (on/off) of the control key.

NORMAL / SHIFT / CTRL (Shifted or Unshifted)

- \*\*\* Key No. 45 is the shift lock. If pressed, this

key causes a shift state unconditionally (LED

lights now).

- \*4 Keys 59 and 71 are shift keys. If pressed, shift and unshift states alternate. If these are pressed in the shift lock mode, the system enters the unshift status.

- \*5 Key 72 is the CTRL key. If a key is pressed with key 72 held pressed, the code corresponding to the key is output in the CTRL mode.

- \*6 Keys marked A//B outputs codes in the CTRL mode if the CTRL key is pressed. Otherwise, they output codes in other modes (Normal Modes). Not CTRL // CTRL

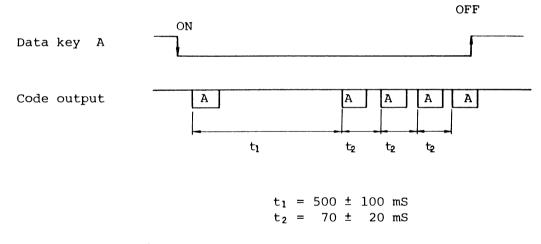

#### 4.3.7 Repeat Function

All code output keys (except the ASCII LOCK, SHIFT LOCK, SHIFT, AND CTRL keys) have the following repeat function.

Fig. 4.3.3 REPEAT FUNCTION

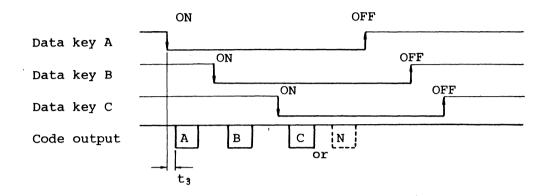

If three keys are pressed together, an unspecified key code may be sent.

$t_3 = 30 \text{ mS max}$

Fig. 4.3.4 2 KEY ROLL OVER

4.3.9 Keyboard Layout

Fig. 4.3.5 shows the layout of the key tops (ASCII).

4.3.10 Key Matrix

Each key on the keyboard is assigned a number as shown in Fig. 4.3.6. The keys are wired in the form of matrix as shown in Table 4.3.2.

| O<br>ASCII ESC     | F1 | F2     | F3      | F4      | F5            | F6   | F7      | F8     | F۹  | F 10 | F11 | F12           | PRINT |

|--------------------|----|--------|---------|---------|---------------|------|---------|--------|-----|------|-----|---------------|-------|

|                    | 2  | #<br>3 | \$<br>4 | %<br>5. | <b>%</b><br>6 | 7    | (<br>8  | )<br>9 | -0. | =    |     | BACK<br>SPACE | C,    |

| ТАВ Q              | W  | Ē      | F       | 2       | - ) ( Y       |      | J       |        | 7 F |      |     |               | EL    |

| O<br>SHIFT<br>LOCK | A  | S      | D       | F       | G             | Н    | J       | K      |     | +    | *   | }             | RET   |

| SHIFT _            | Z  |        |         |         | / [E          | B    |         | 1 ,    |     | >    |     | HFT           | DRZ   |

| CTI                | RĽ |        |         |         | (S PA         | ACE) | <u></u> |        |     |      |     |               |       |

| 7 | 8 | 9 | -           | $\rightarrow$             |

|---|---|---|-------------|---------------------------|

| 4 | 5 | 6 | _           |                           |

| 1 | 2 | 3 | RET         | $\left[ \uparrow \right]$ |

| ( |   | • | U<br>R<br>N | $ \downarrow$             |

| 01 | 2   | 3   | 4   | 5   | 6   | 7   | 8   | - 9 | 10  | 11  | 12  | 13  | 14  | 15 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| 16 | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30 |

| 31 | 3   | 2 3 | 3 3 | 4 3 | 5 3 | 6 3 | 7 3 | 8 3 | 9 4 | 0 4 | 1 4 | 2 4 | 3 4 | 44 |

| °2 | 15  | 46  | 47  | 48  | 49  | 50  | 51  | 52  | 53  | 54  | 55  | 56  | 57  | 58 |

| 59 | ) 6 | 0 6 | 1 6 | 2 6 | 3 6 | 4 6 | 56  | 6 6 | 7 6 | 8 6 | 9 7 | 0   | 71  |    |

|    |     | 72  |     |     |     | 7   | 3   |     |     |     |     |     |     |    |

| 74 | 75    | 76 | 77 | 78 |  |

|----|-------|----|----|----|--|

| 79 | 80 81 |    | 82 | 83 |  |

| 84 | 85    | 86 | 87 | 88 |  |

| 8  | 9     | 90 |    | 91 |  |

| X | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|---|----|----|----|----|----|----|----|---|----|----|----|----|----|----|----|----|

| 0 |    |    |    |    |    |    |    |   |    |    |    |    |    |    |    |    |

| 1 | 77 |    |    |    |    | 78 | 91 |   |    |    |    |    | 82 | 83 | 88 | 87 |

| 2 | 80 | 79 | 76 | 75 | 74 | 81 | 90 |   |    |    |    |    | 84 | 85 | 86 | 89 |

| 3 | 70 |    | 58 |    |    | 69 | 68 |   | 60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 |

| 4 | 55 | 56 | 57 |    |    | 54 | 53 |   | 73 | 46 | 47 | 48 | 49 | 50 | 51 | 52 |

| 5 | 41 | 42 | 43 | 44 |    | 40 | 39 |   | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 |

| 6 | 26 | 27 | 28 | 29 | 30 | 25 | 24 |   | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 |

| 7 | 11 | 12 | 13 | 14 | 15 | 10 | 9  |   |    | 2  | 3. | 4  | 5  | 6  | 7  | 8  |

Fig. 4-3-6 KEY NO. & MATRIX

•

# 5. CRT CONTROL

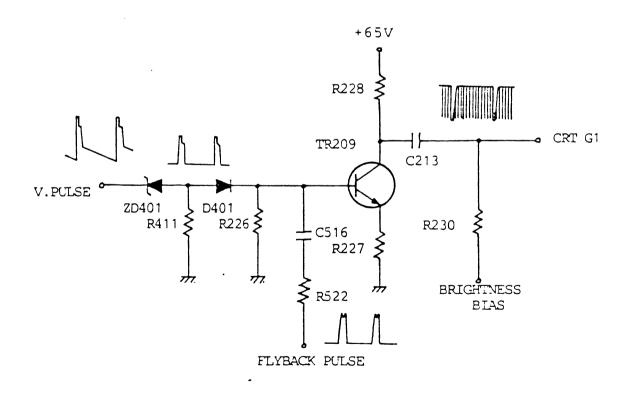

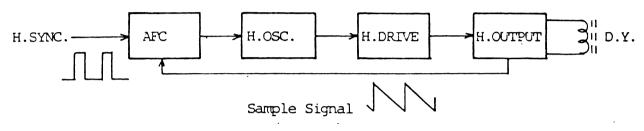

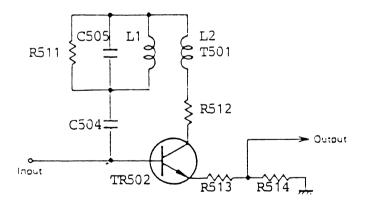

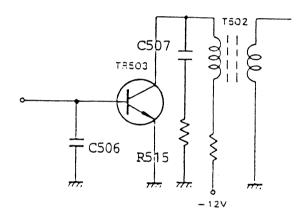

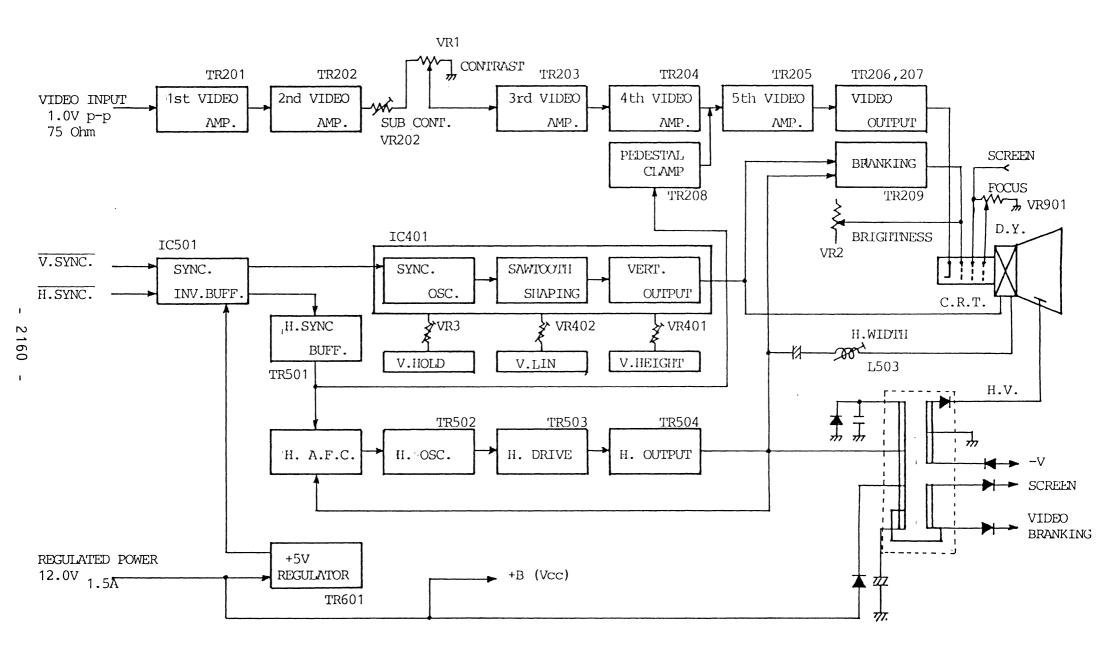

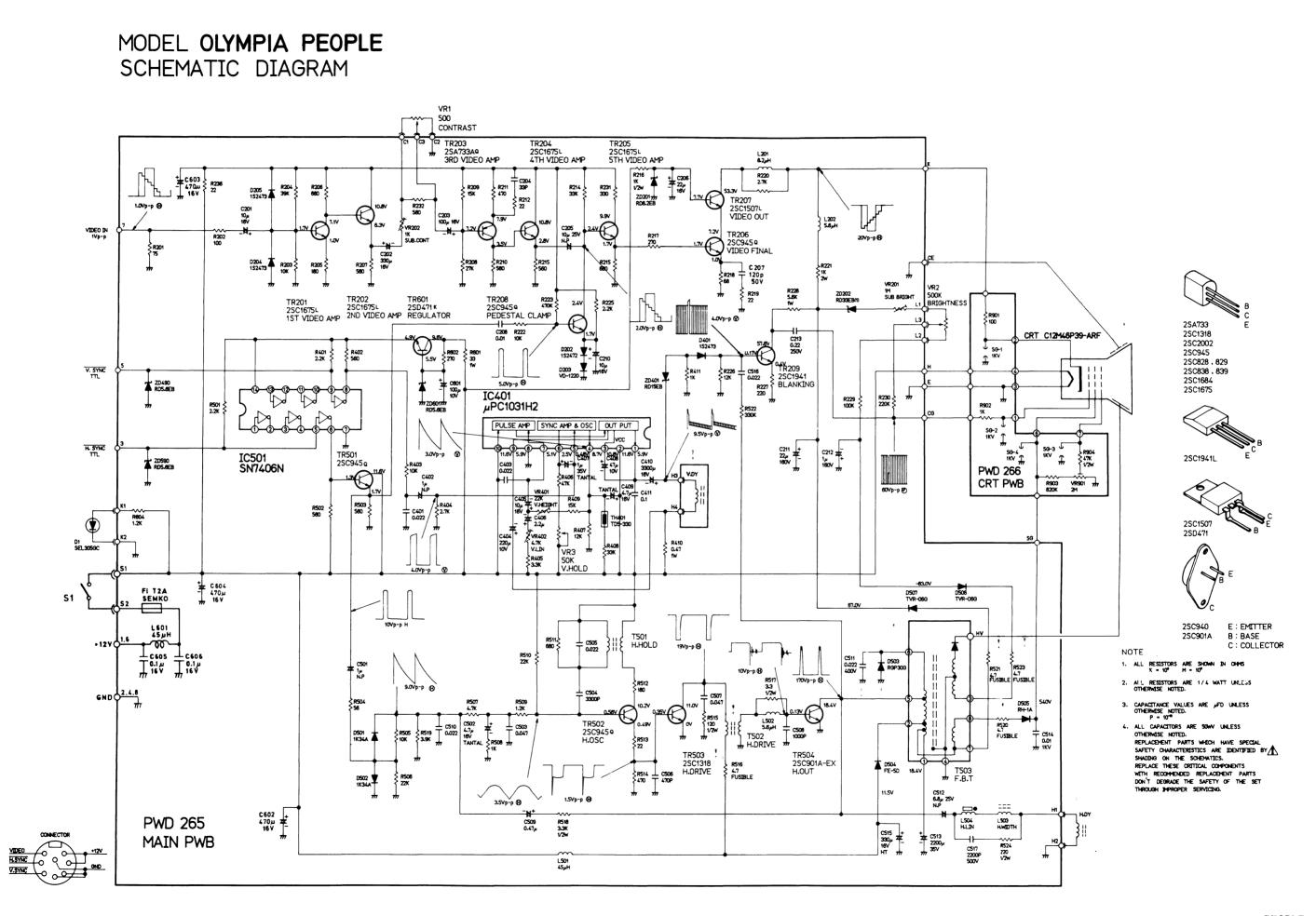

## 5. MONOCHROME CRT CONTROL SECTION

#### 5-1 Overview

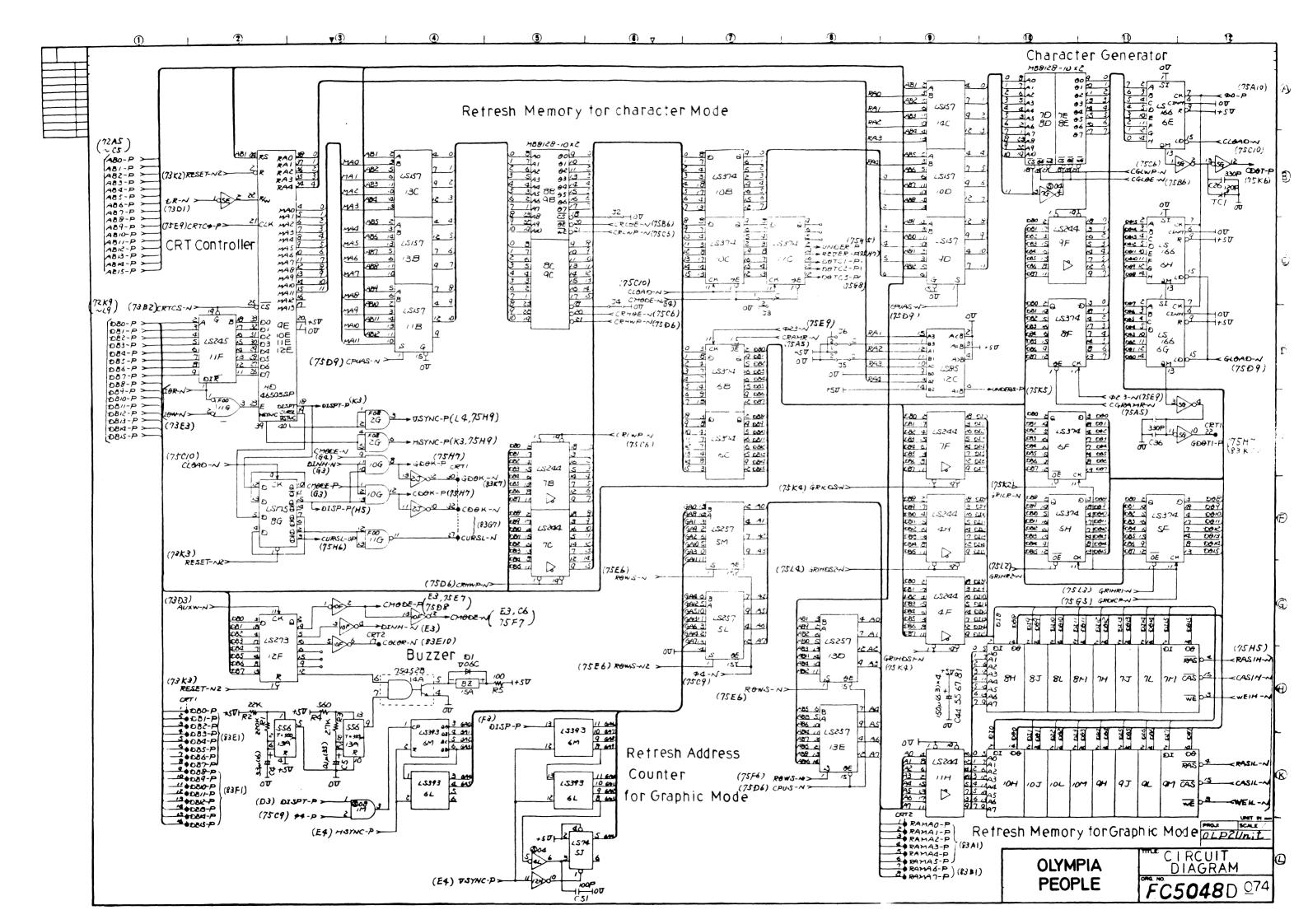

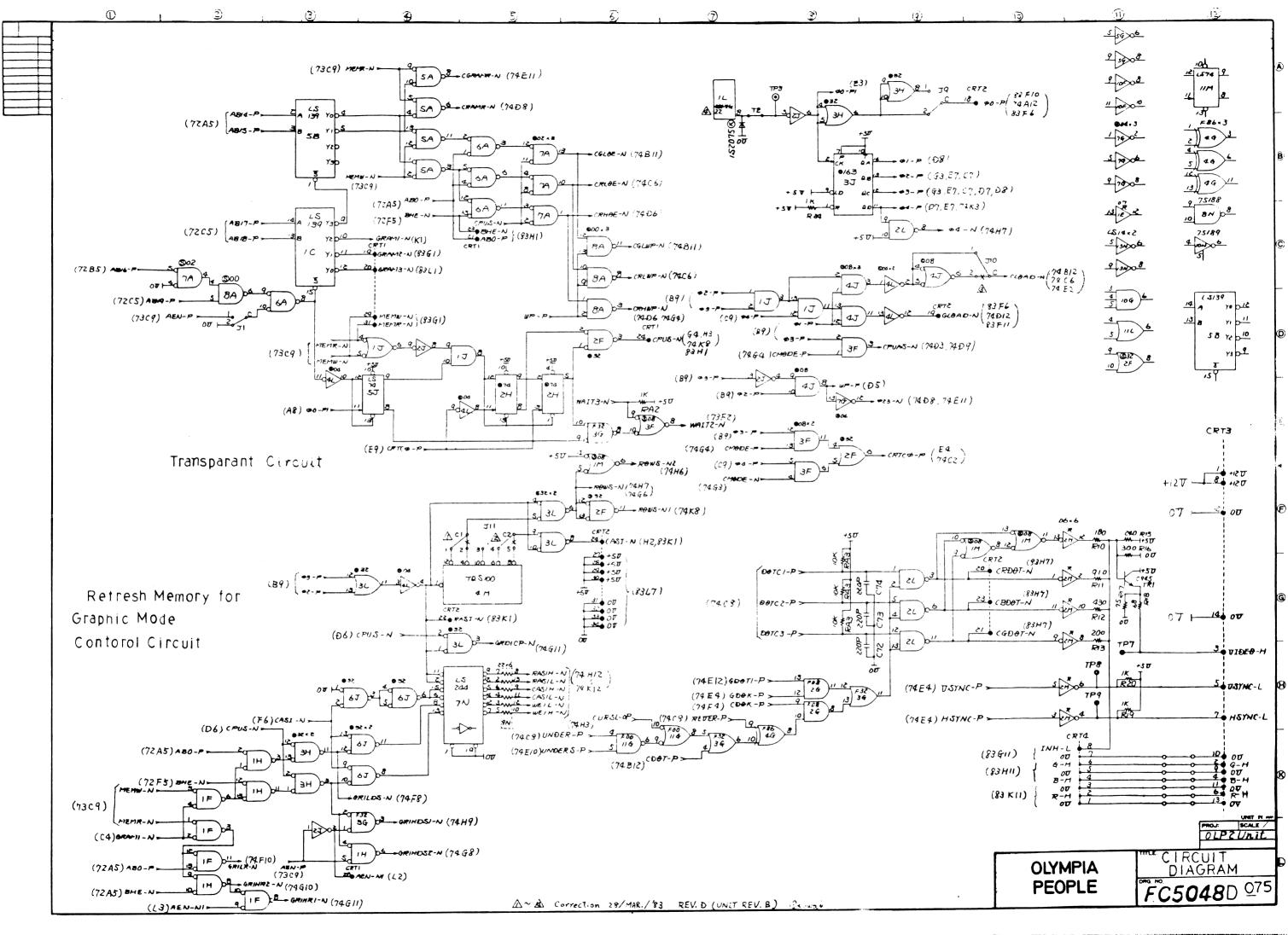

The CRT control section is connected to the monochrome CRT in the format explained in Section 5-6 and designed to control in the mode described in Section 5-2. In the CRT control section, the CRT controller (CRTC) LSI (HD 46505SP) is used.

5-2 Control Mode

In the CRT control section, both the character mode (semigraphic mode) and the full-graphic mode can be specified.

# 5-2-1 Character mode

| o One-cell configuration      | 8 dots x 19 dots           |

|-------------------------------|----------------------------|

| o One character configuration | 7 dots x 15 dots           |

| o One-screen configuration    | 80 cells x 25 cells        |

| o Character generator mode    | The character generator    |

|                               | mode is specified in the   |

|                               | character mode and the     |

|                               | dot pattern of characters  |

|                               | can be changed in          |

|                               | programming.               |

|                               | The patterns up to the     |

|                               | maximum 128 can be stored  |

|                               | in the character generator |

|                               |                            |

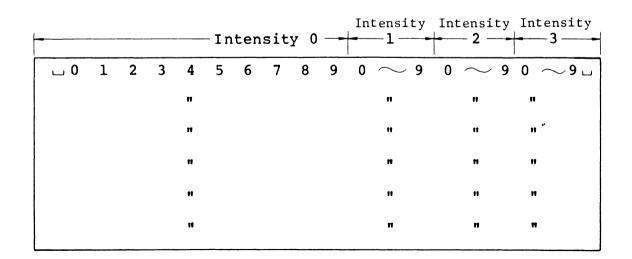

o Attributes Reverse for each cell

Brightness control for

each cell (4 phases)

Underline for each cell

(17, 18 lines fixed)

o Cursor One-cell-painted mode

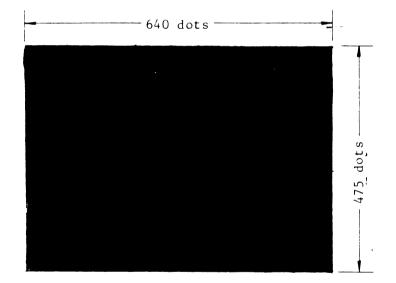

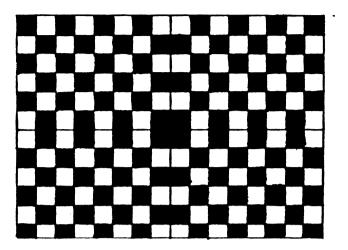

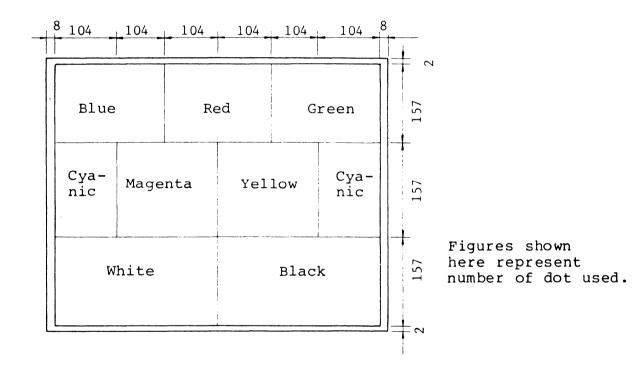

- 5-2-2 Full-graphic mode

- O One-screen configuration640 dots x 475 dotsThere is no attribute and no cursor function.

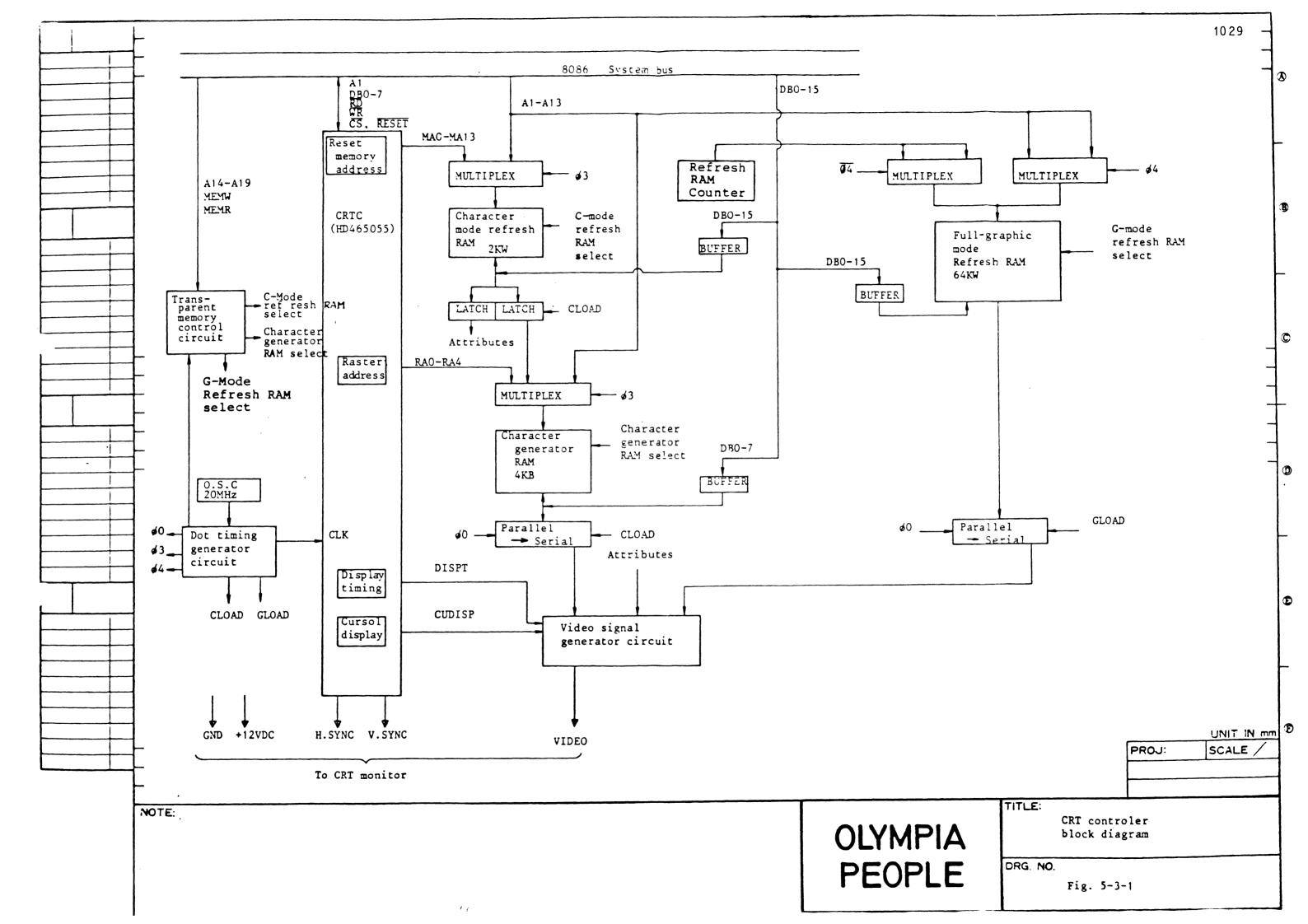

- 5-3 Control Section Configuration

- 5-3-1 Block diagram

For details, see Fig. 5-3-1 "CRT controller Block Diagram".

5-3-2 CRT controller LSI

5-3-3 Character mode refresh RAM

The Character Mode Refresh RAM can specify the characters displayed in the CRT screen.

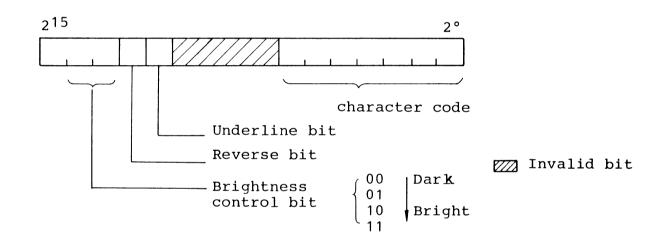

The characters are specified by one word and consists of the character code and the attribute bits.

(Bit configuration is shown as below.) The capacity of C-Mode R-RAM is 2KW. (Two 2K x 8 bit-Static RAMs are used.) CPU can access to C-Mode R-RAM for each word or each byte at any time. The address space of C-Mode R-RAM is E0000<sub>H</sub> to E07FF<sub>H</sub>.

Fig. 5-3-2 Character mode refresh RAM BIT configuration

## 5-3-4 Character Generator RAM (CG-RAM)

The Character Generator RAM stores the character dot pattern and consists of the byte configuration.

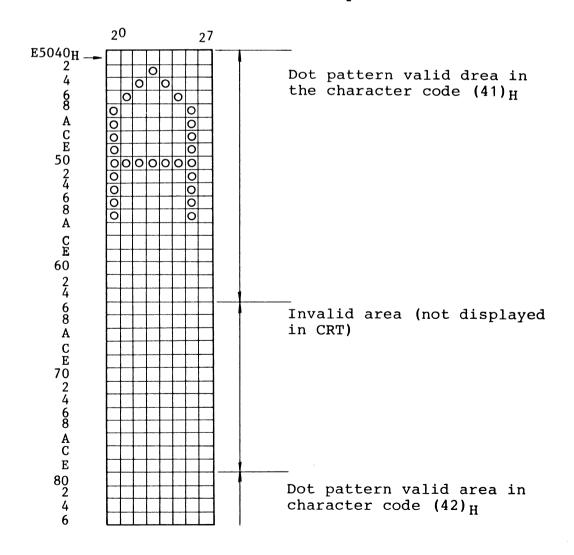

The capacity of CG-RAM is 4K Bytes (two 2K x 8 bit-static RAMs are used) and CPU can access to CG-RAM only for each byte (in the even-numbered addresses). [Example]

When character code  $41_{\rm H}$  is specified, CG-RAM stores the dot pattern indicating character "A".

The header address in CG-RAM for CPU is E4000<sub>H</sub>. The header address in RAM storing the dot pattern is shown as follows:

$E4000_{H} + (100 0001 00000 0)_{B} - E5040_{H}$ Character Line - At any time, 0 is code counter specified.

5-3-5 Full-graphic mode refresh RAM (FG-Mode R-RAM)

Full-graphic mode refresh RAM (FG-Mode R-RAM) is valid when the full-graphic mode is specified, the memory in FG-mode R-RAM is the refresh memory in which one bit corresponds to one dot in the CRT screen.

The memory capacity is 64KW (in which sixteen  $64K \times 1$  bit-dynamic RAMs are used).

CPU can access to FG-Mode R -RAM for each byte or each word.

The following table shows the correspondence of the RAM addresses to the CRT screen from CPU. The addresses within the part bordered with a bold line are displayed in the CRT screen.

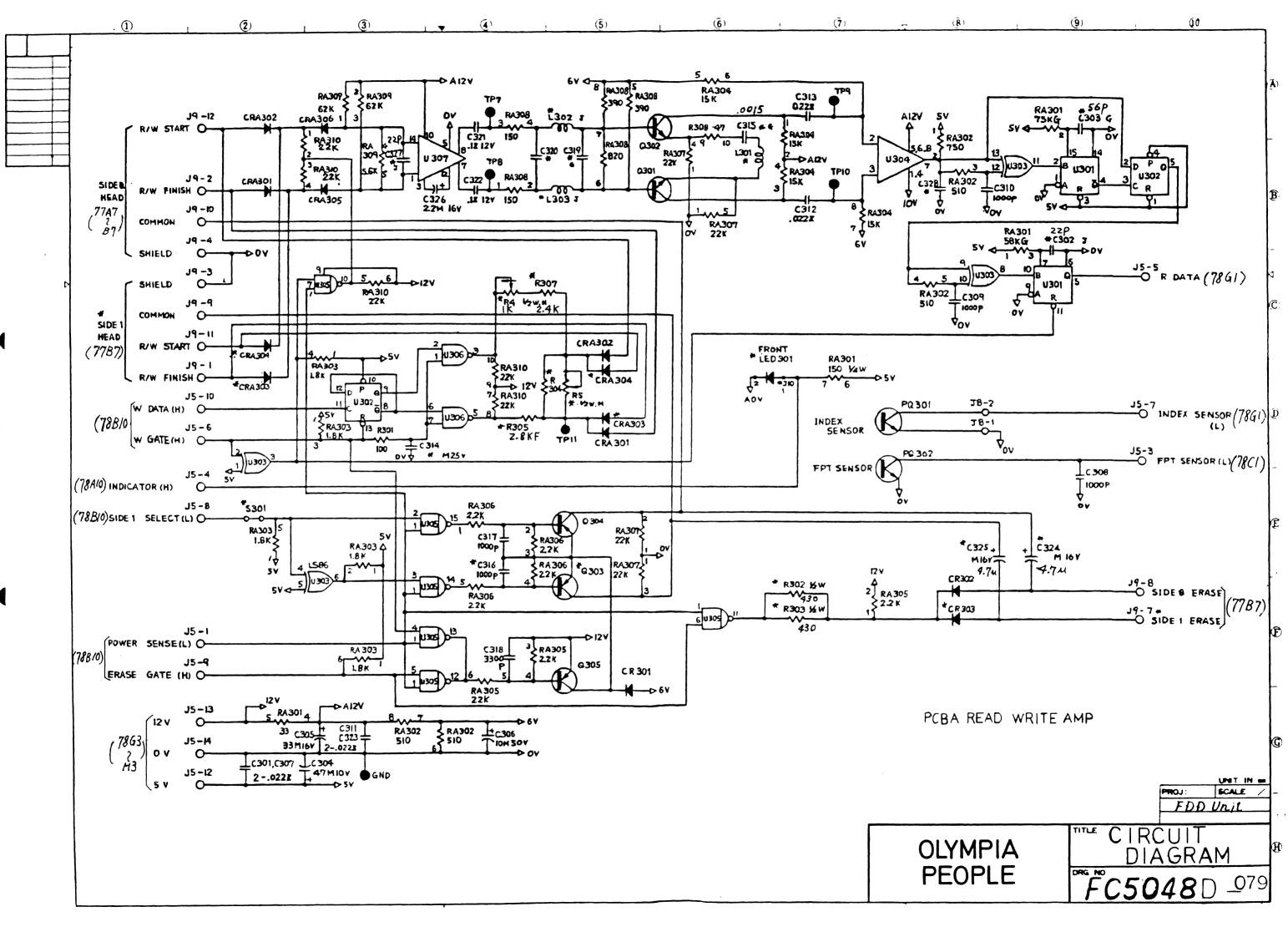

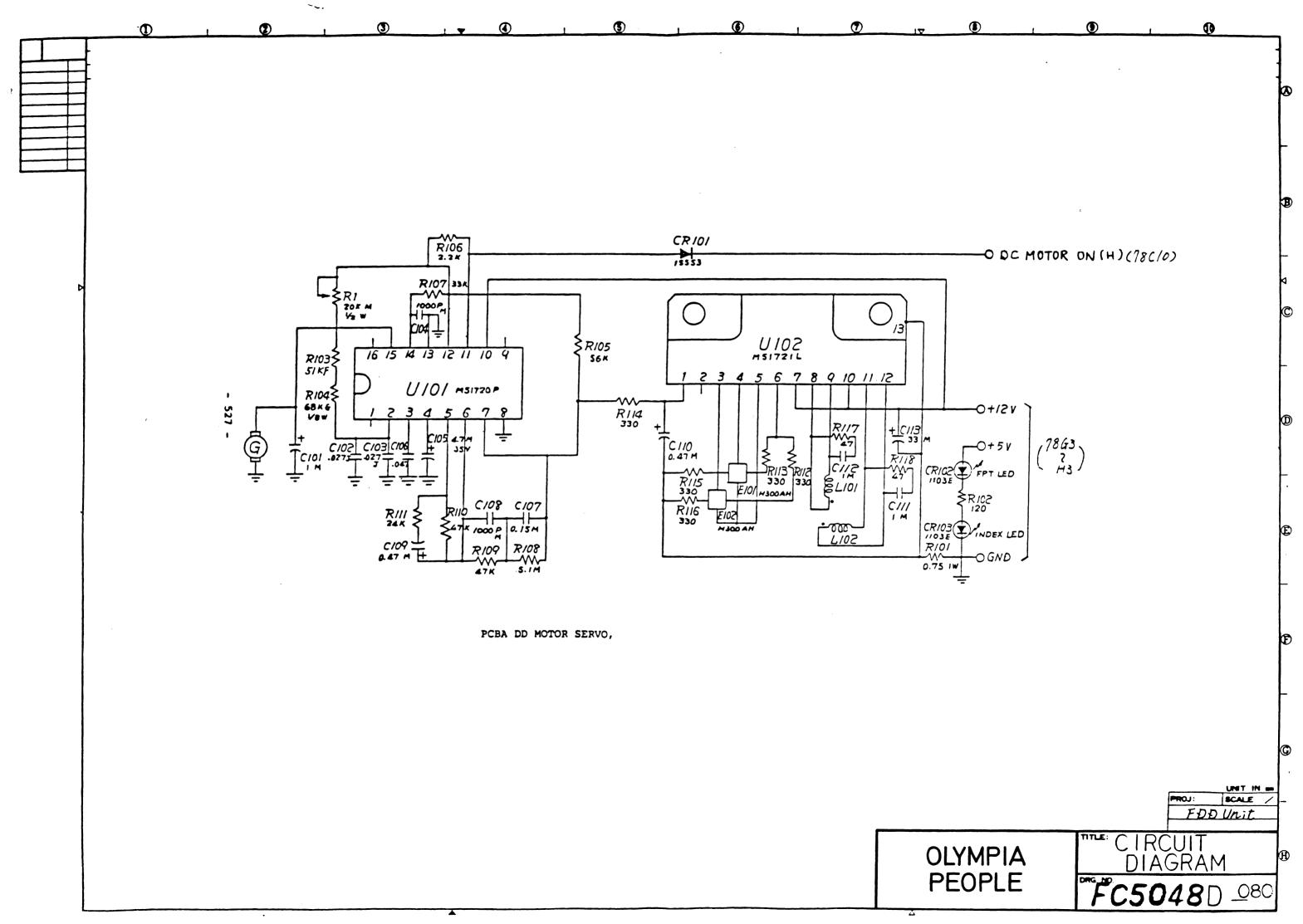

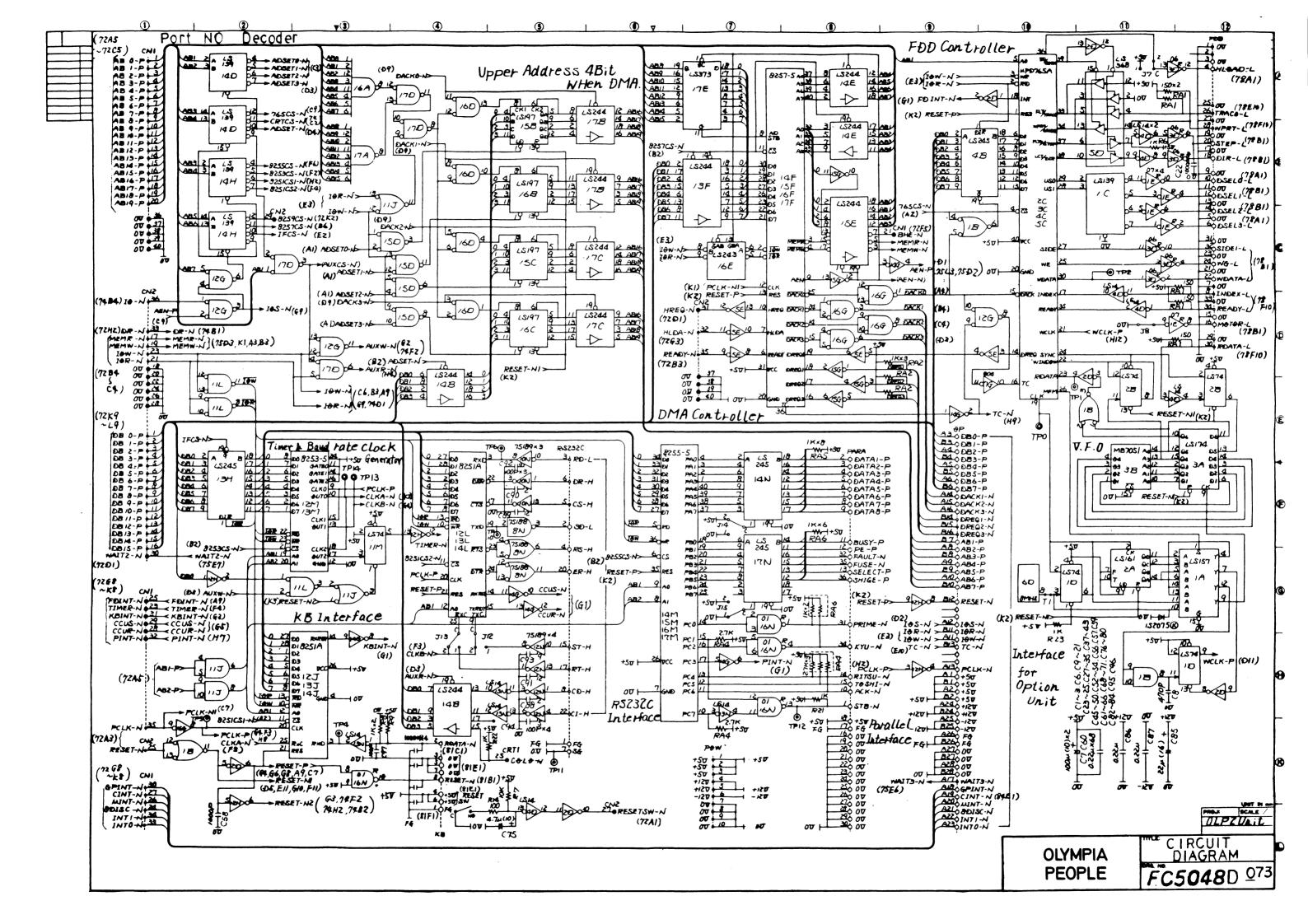

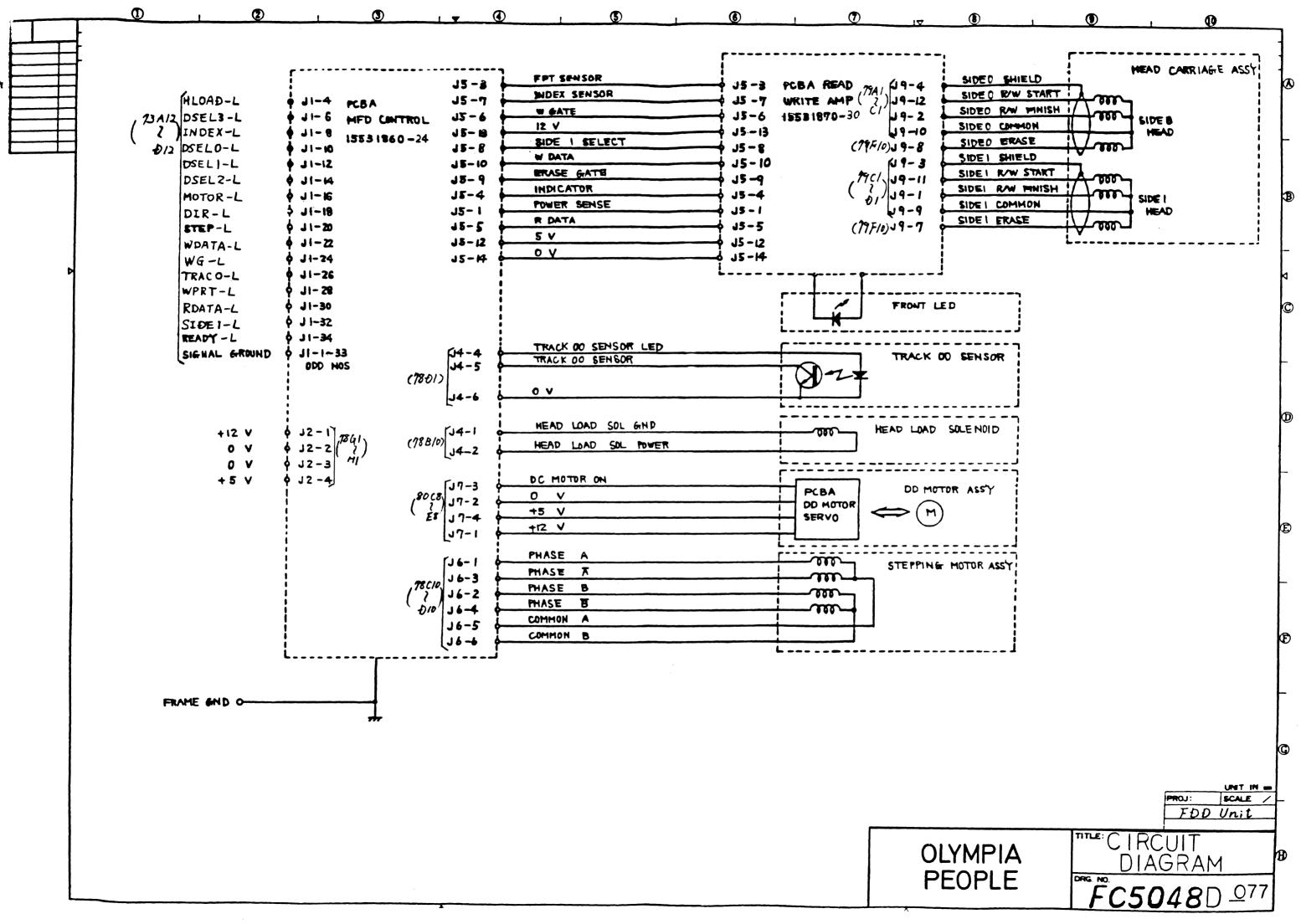

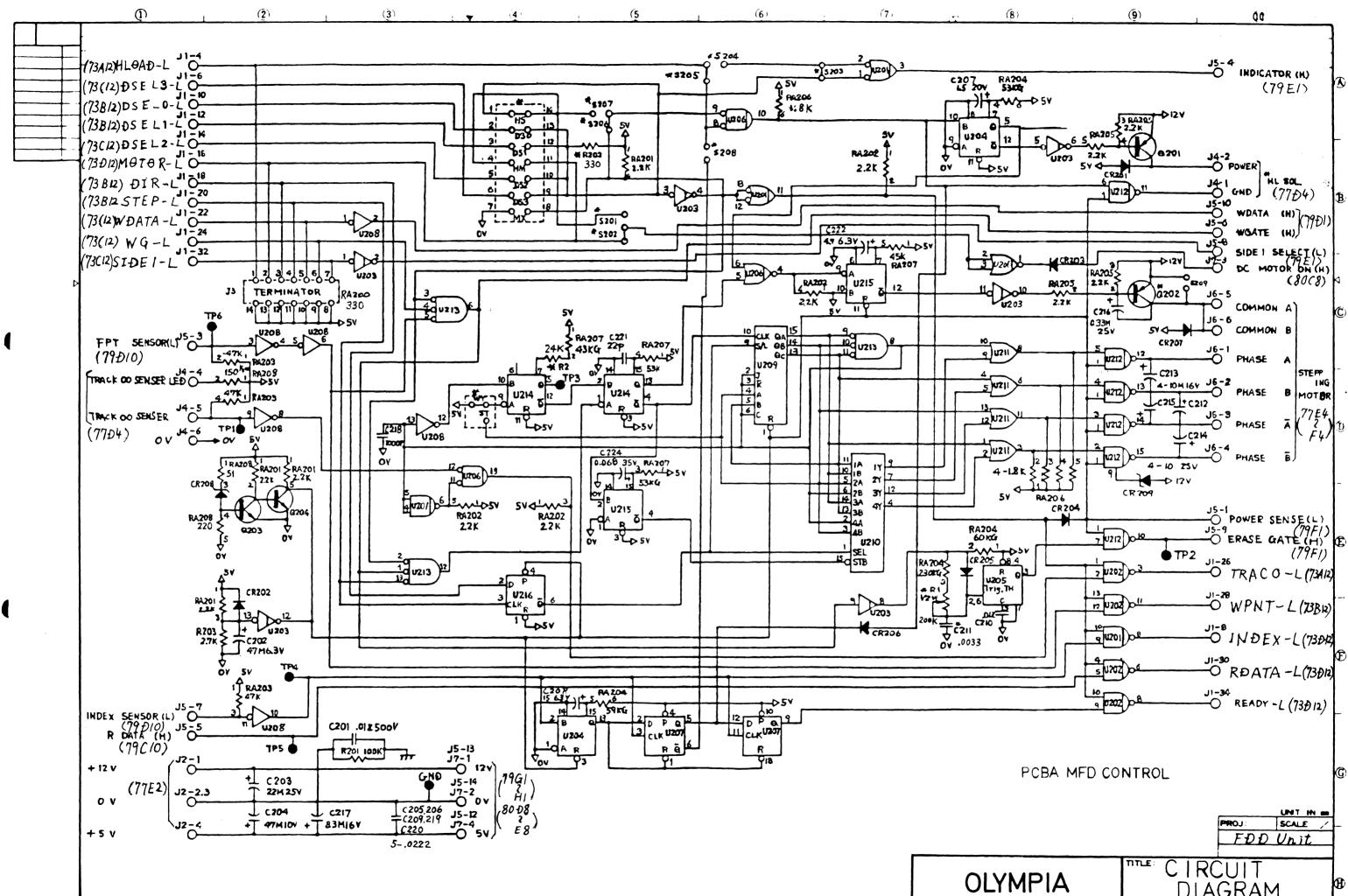

6. FDD CONTROL

.

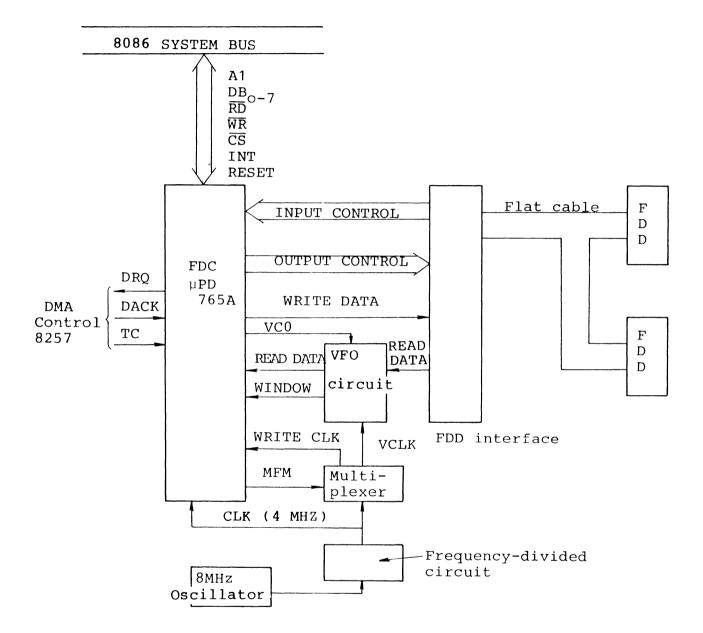

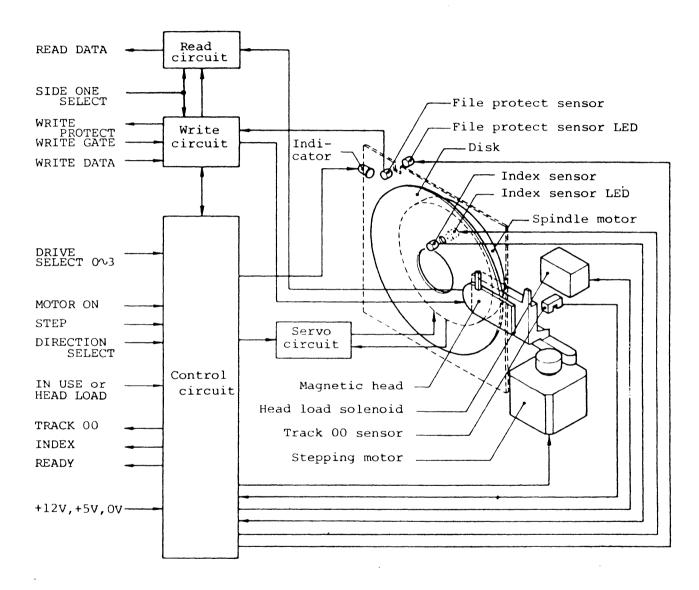

6-1 Overview

FDD control part is designed to control the double-density (in both sides) and double-track-type minifloppy disk up to the maximum two, using Floppy Disk Controller (FDC) LSI ( $\mu$ PD765A).

Fig. 6-2-1 FDD control block diagram

# 6-3 Floppy Disk Controller (FDC)

6-4 Clock Generation Circuit

The clocks used in the FDDcontrol part are shown as follows:

o µPD 765A clock (CLK)

o WRITE clock

o VFO clock (VCLK)

The above clocks are generated by dividing the frequency of the 8-MHz oscillator. These frequencies depend on the densities, such as single-density and double-density. (The frequency is selected depending on the MFM mode signal from FDC.)

|           | Single density | Double density |  |  |  |  |

|-----------|----------------|----------------|--|--|--|--|

| CLK       | 4MHz           | 4MHz           |  |  |  |  |

| WRITE CLK | 4MHz           | 8MHz           |  |  |  |  |

| V CLK     | 250KHz         | 500KHz         |  |  |  |  |

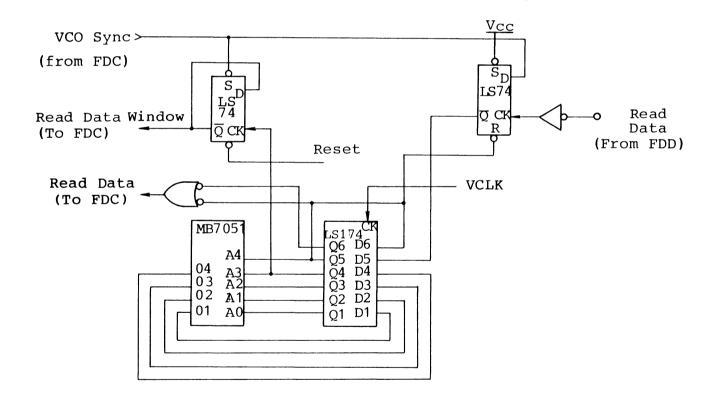

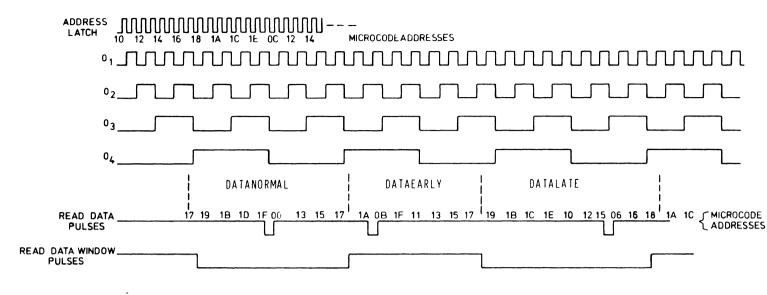

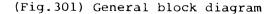

The Variable Frequency Oscillator (V.F.O) circuit consists of PROM (MB7051) with the capacity of 32 words x 8 bits, Address Latch (74LS174), and two flip-flops (74LS74). (See Fig. 6-5-1)

The thirty-two-word micro code (from addresses 00H to 1FH, for the contents of it, see Table 6-5-1) is stored in PROM.

When the read-mode is not specified in FDC (when the VCO signal is "L"), or even if the read-mode is specified in FDC (when the VCO signal is "H"), when the read-data (RD) is not received, the free-run mode is specified in PROM and Address Latch (Repeat the processings using the data from addresses 10H to 1FH).

When the read-mode is specified in FDC and RD is received from FDD, the mode to be specified changes from the free-run mode to the V.F.O mode.

When the flip-flop is set by the rise edge signal of RD, address A4 is low-level and the address to be specified next jumps to one of low-order address 16 (addresses 00H to 0FH) in PROM.

The data to delay or advance the Read Data Window(RDW) signal by one or two clocks is stored in the jump address. (See Table 6-5-1).

The distance from the generated RD to the center of the RDW signal determines the selection either to delay, or to advance the RDW signal.

When adress A<sub>4</sub> is high-level, the free-run mode is specified again.

For details, refer to Fig. 6-5-1 "V.F.O Circuit" and Fig. 6-5-2 "V.F.O Circuit Timing Chart."

Circuit timing

Fig. 6-5-2 V.F.O Circuit timing chart

Table 6-5-1

.

#### PROM MICROCODE

| FOI<br>ADDRESS <sub>H</sub> | R DISK<br><sup>DATA</sup> H | DRIVE DATA RECOVERY<br>CLOCK ACTION TAKEN |

|-----------------------------|-----------------------------|-------------------------------------------|

| 00:                         | 01                          | :NONE                                     |

| 01:                         | 01                          | RETARD BY ONE COUNT                       |

| 02:                         | 02                          | : " " " "                                 |

| 03:                         | 03                          | : " " " "                                 |

| 04:                         | 03                          | :RETARD BY TWO COUNTS                     |

| 05:                         | 04                          | : " " " "                                 |

| 06:                         | 05                          | : " " " "                                 |

| 07:                         | 06                          | : " " " "                                 |

| 08:                         | ОВ                          | ADVANCE BY TWO COUNTS                     |

| 09:                         | 00                          | : " " " "                                 |

| 0A:                         | 0 D                         | : " " " "                                 |

| OB:                         | 0 E                         | ADVANCE BY ONE COUNT                      |

| 0C:                         | 0 E                         | : " " " "                                 |

| 0D:                         | 0 F                         | ADVANCE BY ONE COUNT                      |

| 0E:                         | 00                          | : " " " "                                 |

| 0F:                         | 01                          | : " " " "                                 |

| 10:                         | 01                          | FREE RUN                                  |

| 11:                         | 02                          | : " "                                     |

| 12:                         | 03                          | : " "                                     |

| 13:                         | 04                          | : " "                                     |

| 14:                         | 05                          | : " "                                     |

| 15:                         | 06                          | : " "                                     |

| 16:                         | 07                          | : " "                                     |

| 17:                         | 08                          | : " "                                     |

| 18:                         | 09                          | : " "                                     |

| 19:                         | 0 A 0                       | : " "                                     |

| 1A:                         | 0 B                         | : " "                                     |

| 1B:                         | 00                          | : " "                                     |

| 10:                         | O D                         | : " "                                     |

| 10:                         | 0 E                         | : " "                                     |

| 1E:                         | 0 F                         | : " "                                     |

| 1F:                         | 00                          | : " "                                     |

1038

7. SERIAL INTERFACE

## 7. SERIAL INTERFACE

## 7-1 Overview

PEOPLE has the serial interface according to the RS232C standard as one of the general interfaces. The units connected to the serial interface are shown as follows.

MODEM, Printer, Keyboard Typewriter, Tape Reader, Tape Puncher, or the composite device combinated with some of the above devices.

Therefore, programming according to the unit connected to the serial interface allows People to apply to the various application program.

7-2 Specification

7-2-1 Standard

RS-232C

## 7-2-2 Interface circuit

(1) Output

Driver I.C. is SN75188N (T.I. or equivalent)

(2) Input

Receiver I.C. is SN75189N (T.I. or equivalent)

7-2-3 Cable length

Cable must be 10m long maximum.

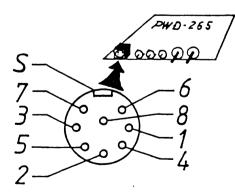

7-2-4 Connector ( PEOPLE side)

DB-25SA-J4-2-L (JAE or equivalent)

As seen from connecting side

#### 7-4 Transmission Speed

The methods of synchronizing the transmission timing are classified into Internal Synchronization and External Synchronization. Switching External Synchronization or Internal Synchronization depends on the jumper line. It is set to INTERNAL when the unit is shipped out. Printed foil is used for INTERNAL setting ; when shifting to External,cut the foil and connect to EXTERNAL with a jumper.

|   | J12                | J13                          |

|---|--------------------|------------------------------|

| - | oo<br>C 2<br>(INT) | • ••<br>1 C 2<br>(EXT) (INT) |

## 7-4-1 External synchronization

The transmission speed is determined by the clock pulse which are transmitted from the external units. In this case, the mode command specified to 8251A set BAUD RATE to X1.

## 7-4-2 Internal synchronization

The transmission speed can be programmed by timer controller (8253), and can be set on software basis to either one of 150, 300, 600, 1200, 2400, 4800 and 9600 BPS.

For Timer Controller 8253, refer to Chapter 9. In this section, how to set it explains as below.

# 7-2-5 Interface signals

|         |             | Direct | ion                                    |                                       |

|---------|-------------|--------|----------------------------------------|---------------------------------------|

| Pin No. | Signal name | CPU    | ЕХТ                                    | Remarks                               |

| 1       | FG          |        |                                        | Frame ground                          |

| 2       | SD          |        |                                        | Transmission data                     |

| 3       | RD          |        |                                        | Receiving data                        |

| 4       | RS          |        |                                        | Request to send                       |

| 5       | CS          |        |                                        | Clear to send                         |

| 6       | DR          |        |                                        | Data set ready                        |

| 7       | SG          |        |                                        | Signal ground                         |

| 8       | CD          |        |                                        | Carrier detect                        |

| 15      | ST2         | -      |                                        | Transmission signal<br>element timing |

| 17      | RT          |        |                                        | Receiving signal<br>element timing    |

| 20      | ER          |        |                                        | Terminal ready                        |

| 22      | CI          |        | ······································ | Calling indicator                     |

Table 7-2-1 Serial I/F signals

# 7-3 Interface Controller

The serial interface employs 8251A as controller.

One of the three timer counters on timer controller (8253) is used for setting the serial interface baud rate.

Since 2.4576 MHz clock is applied to the clock input terminal of the corresponding timer counter, 2.4576 MHz ÷16 ÷N (Timer setting) =Transmission speed

| N | =   | 16   | 9600 | BPS |

|---|-----|------|------|-----|

|   | =   | 32   | 4800 | BPS |

|   | =   | 64   | 2400 | BPS |

|   | =   | 128  | 1200 | BPS |

|   | =   | 256  | 600  | BPS |

|   | . = | 512  | 300  | BPS |

|   | =   | 1024 | 150  | BPS |

In this case, the baud rate for serial controller (8251) must be set to 1/16. The mode of timer controller (8253) must be set to 3 (binary count mode).

# 8. PARALLEL INTERFACE

## 8. PARALLEL INTERFACE

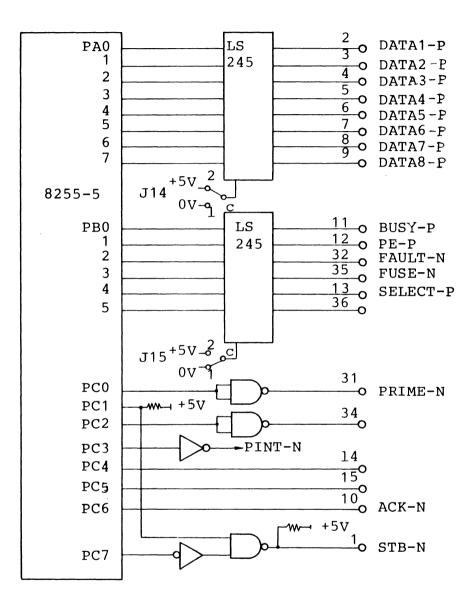

8-1 Overview

The parallel 8-bit data is output or input. The interface controller (8255) and the bidirectional driver are used. The circuit is set to output or input by switching the 8255A program and the jumper wire on the seat.

8-2 Interface Circuit

Fig. 8-2-1

## 8-3 Connector

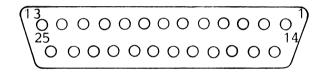

(1) Connector 57LE-40360-2700 (D3)

(2) Pin array

#

Fig. 8-3-1 Pin array

(The figure viewed from the

connector-connected section.)

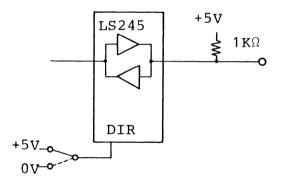

## 8-4 Switching the Interface Direction

Fig. 8-4-1 Interface circuit

#### 8-4-1 Data output circuit

The following are set when the interface circuit is used as a data output circuit.

- (1) The output direction is the signal direction of the bidirectional bus drive LS245 (14N). Set J14 connection to C to 2. (When shipped from the factory, the interface circuit is set with the print foil.)

- (2) The input direction is the signal direction of the bidirectional bus drive LS245(17N). Set J15 connection to C to 1. (When shipped from the factory, the interface circuit is set with the print foil.)

- (3) Set control IC8255-5 to the data output operating mode by the program.

## 8-4-2 Data input circuit

The following are set when the interface circuit is used as a data input circuit.

(1) The input direction is the signal direction of the bidirectional bus driver LS245(14N). Set J14 connection to C to 1. (Cut the print foil in C to 2).

- (2) The output direction is the signal direction of the bidirectional bus driver LS245(17N). Set J15 connection to C to 2. (Cut the print foil in C to 1.)

- (3) Set control IC 8255A to the data input operating mode by the program.

8-4-3 Interface Controller

## 8-5 Printer Interface

The examples for using this circuit as a printer interface are shown as below.

8-5-1 Setting the circuit

When shipped from the factory, this circuit is set for the printer interface as follows: J14: C to 2 J15: C to 1

8-5-2 Setting the controller by the program

Set the controller as shown in Table 8-5-1 by the program.

| Control words    | Group A |                  |        |      |      |                      | Group B |        |        |  |    |

|------------------|---------|------------------|--------|------|------|----------------------|---------|--------|--------|--|----|

| D7D6D5D4D3D2D1D0 | Port A  |                  | Port C |      |      |                      |         | Port   | Port B |  |    |

|                  |         |                  | PC6    | PC 5 | PC 4 | PC 3                 | PC 2    | PC1    | PC 0   |  |    |

| 1 0 1 0 1 0 1 0  | OUT     | OBF <sub>A</sub> | ACKA   | IN   |      | in intr <sub>a</sub> |         | A OU'I |        |  | IN |

Table 8-5-1 Example for setting the ports in the printer interface

# 8-5-3 Interface signals

Table 8-5-2 List of the printer interface signals

| Pin No. | Signal-name   | Direction    |                                                                                    |

|---------|---------------|--------------|------------------------------------------------------------------------------------|

|         |               | CPU Exterior | Contents                                                                           |

| 1       | STB-N         |              | Sample the data                                                                    |

| 2       | DATA 1-P      |              |                                                                                    |

| 3       | 2             |              |                                                                                    |

| 4       | 3             |              |                                                                                    |

| 5       | 4             |              |                                                                                    |

| 6       | 5             | <b>&gt;</b>  | Output data                                                                        |

| 7       | 6             |              |                                                                                    |

| 8       | 7             | <b>-</b>     |                                                                                    |

| 9       | 8             |              |                                                                                    |

| 10      | ACK-N         |              | Request the subsequent data.                                                       |

| 11      | BUSY-P        |              | The external unit cannot receive the data.                                         |

| 12      | PE-P          |              | The forms are short when<br>the circuit is connected to<br>the printer             |

| 13      | SELECT-P      |              | The SELECT state occurs.                                                           |

| 14      |               |              |                                                                                    |

| 15      |               |              |                                                                                    |

| 16      | 0V            |              | SIGNAL GROUND                                                                      |

| 17      | FG            |              | FRAME GOUND                                                                        |

| 18      | +5V           |              | Power                                                                              |

| 19-30   | TWIST PAIR GN | D            | TWIST PAIR RETURN                                                                  |

| 31      | PRIME-N       |              | Set the external unit to the initial state.                                        |

| 32      | FAULT-N       |              | When one of the PE, SELECT,<br>and FUSE state occurs, the<br>circuit is low-level. |

| 33      |               |              |                                                                                    |

| 34      |               |              |                                                                                    |

| 35      | FUSE-N        |              | When the fuse is off, the circuit is low-level.                                    |

| 36      |               |              |                                                                                    |

# 9. TIMER CONTROLLER

#### 9. TIMER CONTROLLER

#### 9-1 Overview

The timer controller (8253-05) has three timer counters. These three timer counters are independent respectively and used as follows:

- (1) Interval timer

- (2) Clock for setting BAUD RATE of RS232C Serial Controller

- (3) Clock for receiving to the keyboard interface controller

# 9-2 Generating the Clock for KB Interface (Channel 0)

The series data transmission format is specified in the interface with KB, as described in Section 4-1-1.

The data transfer rate is 1200 BPS and the data transmission is controlled by 8251A.

As described in Section 4-2-1, the clock of 19.2 KHz must be given to 8251A.

The clock of 2.4576 MHz (PCLK) is given to Channel 0 in 8253-5. Therefore, when the timer counter in channel 0 is set to 128, the clock of 19.2 KHz is output as follows:

2.4576 (MHz)  $\div$  128 = 19.2 (KHz) The mode to be specified in the timer (Channel 0) is as below.

```

Mode = 3

binary-count

```

9-3 Setting the Transfer Rate in the Serial Interface (CHANNEL 1)

Channel 1 in 8253-5 output the clock determining the transfer rate to the serial interface controller (8251A).

The input clock is the same clock of 2.4576 MHz (PCLK) as that in channel 0. The operating mode is 3, and the binary count mode.

For the timer-set value for determining the transfer rate, refer to Section 7-4-2.

9-4 Interval Timer (CHANNEL 2)

Channel 2 in 8253-5 is used as an interval timer.

The clock output (CLKA) in channel 0 is given to the input clock. (The frequency is 19.2 KHz).

The interval timer interrupts to CPU (8086) periodically, and the cycle depends on the value set in the timer counter in Channel 2. When the set value is N,

$N \div 19200 = T [sec],$

that is, T is the cycle of the interval timer.

The optional value from 0 to  $(FFFF)_{16}$  is set in N, however, value 0 is equivalent to value  $(10000)_{16}$ . Therefore, the following are obtained.

l ≦ N ≦ 65536

52  $\mu$ s < T < 3.42 sec

The value from 52  $\mu$ s to 3.42 sec can be set in T, for each unit of about 52  $\mu$ s.

The operating mode is 2, and set to binary count mode.

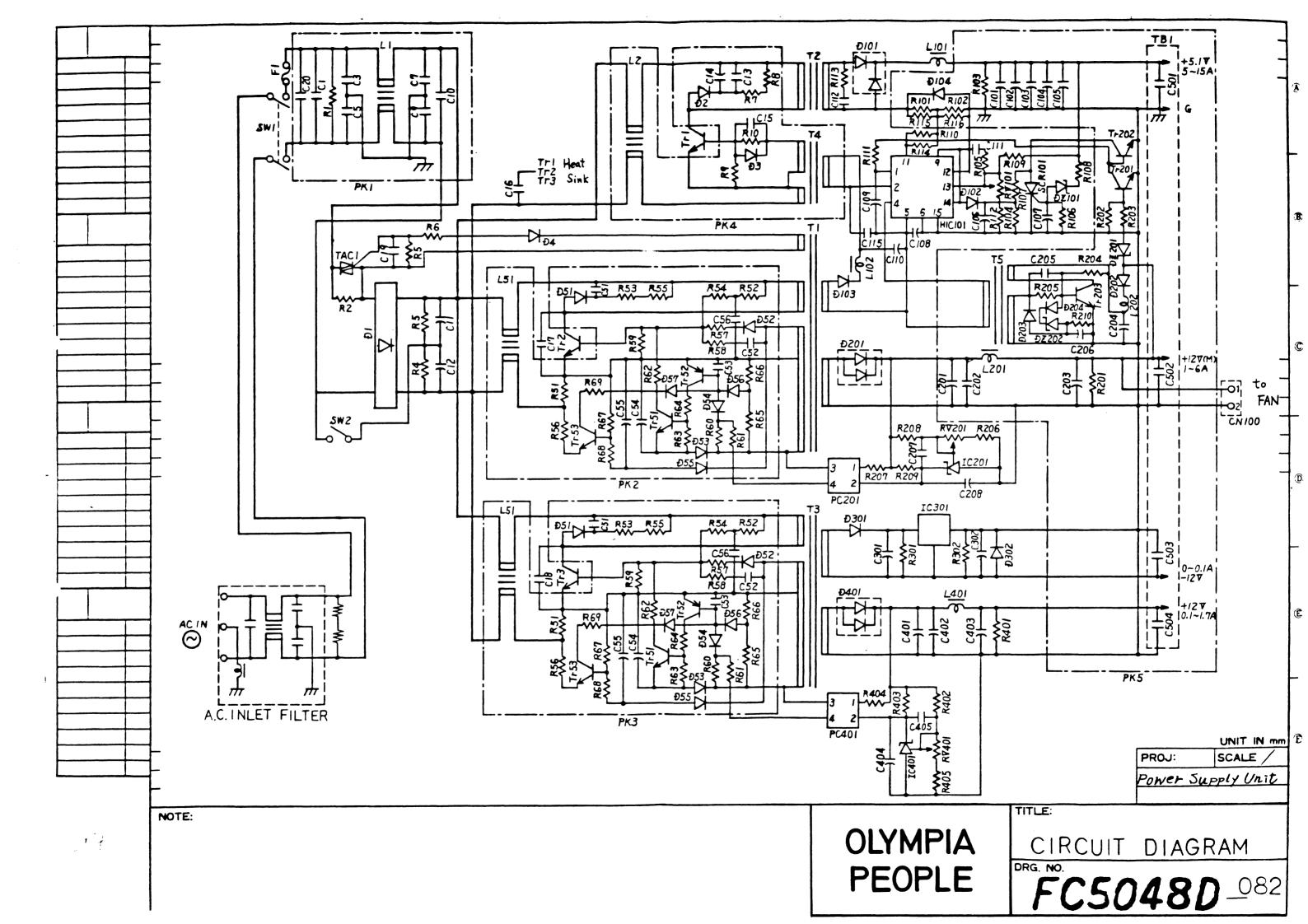

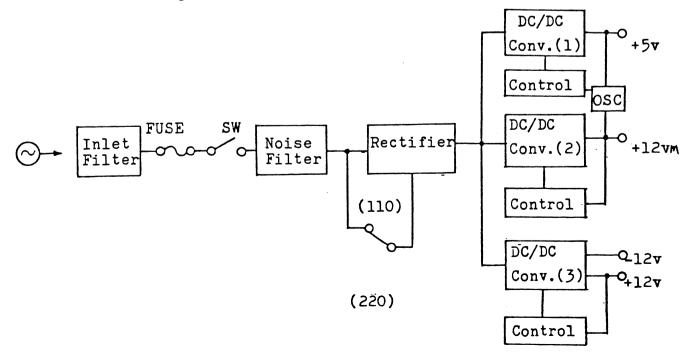

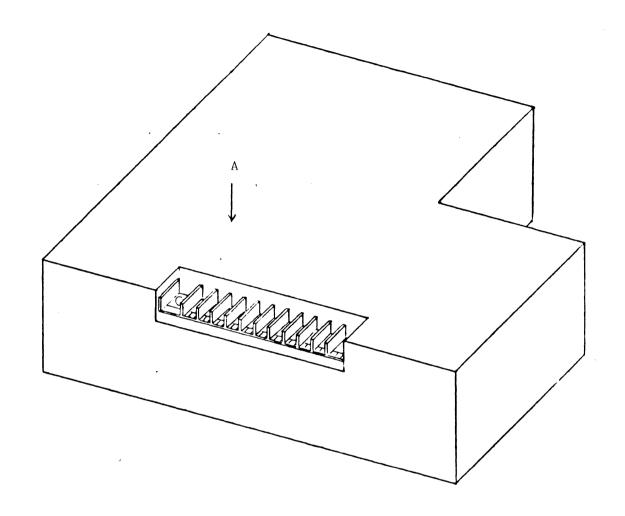

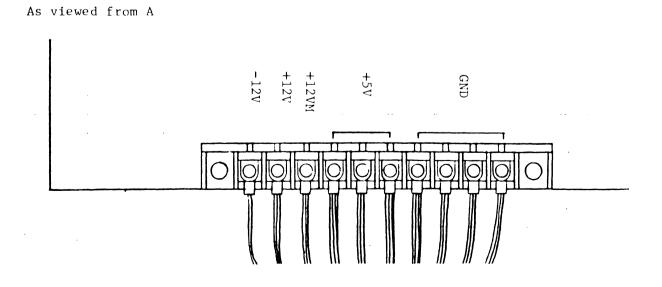

10. Power Supply Unit

10. Power Supply Unit

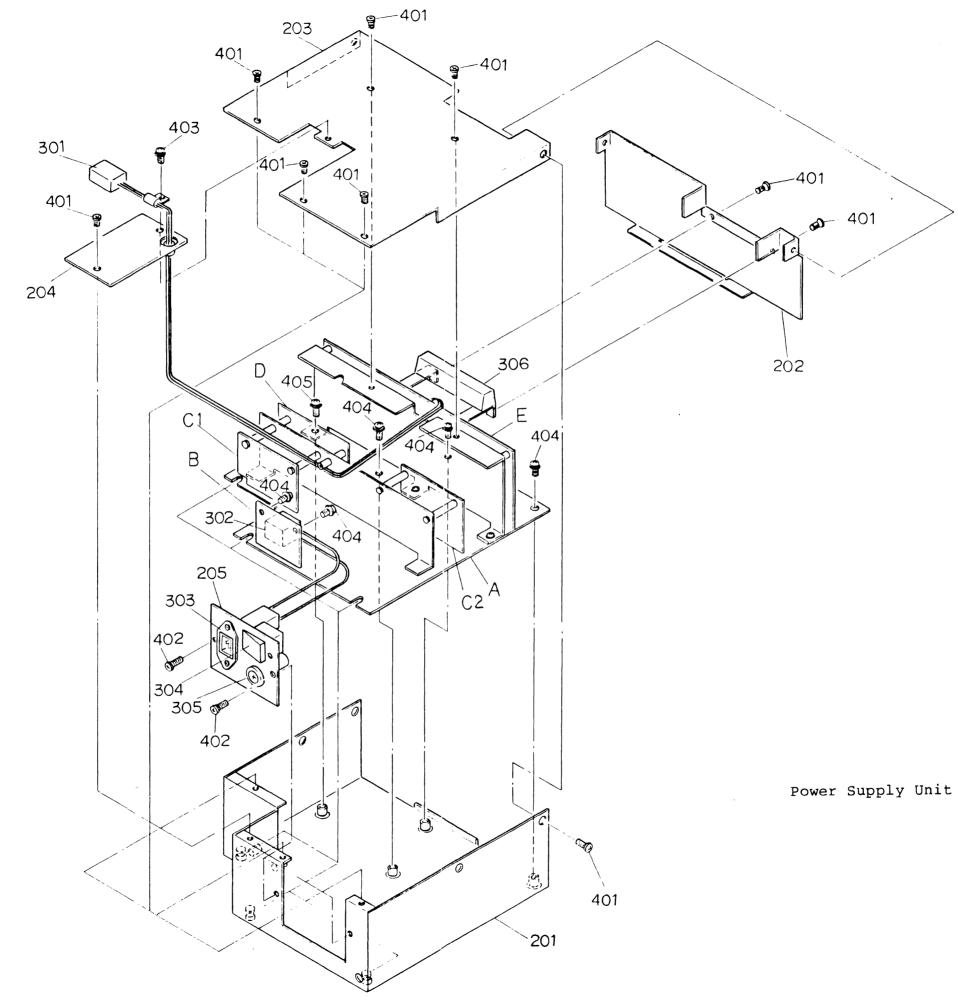

10-1 Power Supply Unit

This unit was composed for obtaining stabilized D.C. output from the commercial A.C. voltage. The conditions of input and output are stated in Para. 2.

10-2 Input - Output

Input. AC 110V 50/60 Hz AC 220V/240V 50/60 Hz

Output. +5V 15A max +12V M 3A (6A Peak) +12V 1.7A max -12V 0.1A max

Range selection is manually performed by the use of an input voltage selector in this unit.

10-3 Block Diagram

### 10-4 Filter

This block is composed of inlet type filter and L, C that are installed in PKl unit. This block protects the main unit from the noise that is transmitted from outside via AC input cable. And also, this filter prevents the outgoing noise generated in the main unit.

# 10-5 Switch and Fuse

The input after passing the inlet-type filter is connected to the on-board filter through the fuse and both line ON/OFF switch.

10-6 Rectifier

When the input voltage selector in this power supply unit is at AC 220V, the rectifier circuit is operating as normal full wave rectifier.

The primary DC voltage, which is obtaining by wave filtering, is approximately 300V DC at both AC 110V and AC 220V.

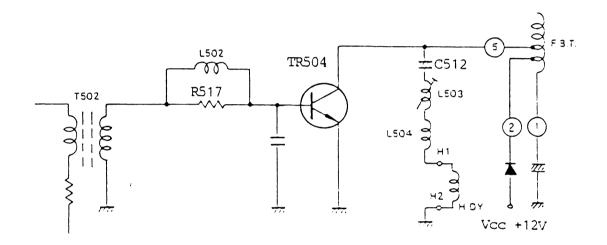

### 10-7 Fly-back converter circuit(12VM, 12V)

The DC/DC convertors (2) and (3) are a circuit formed to obtain the outputs by the blocking oscillator.

The separation of the primary and secondary is done by the Photo-Coupler.

+12V M output is controlling the On-Pulse width of DC/DC convertor (2) to detect the output voltage.

In the same form, +12V output is controlling the On-Pulse width of DC/DC convertor (3) to detect the output voltage.

-12V output is stabilized by the series regulator IC to be taken out from output transformer of the DC/DC convertor (3).

+5V output is coming to stabilized voltage output by the DC/DC convertor (1), pulse width modulated forward convertor. 10-8 Over voltage protection

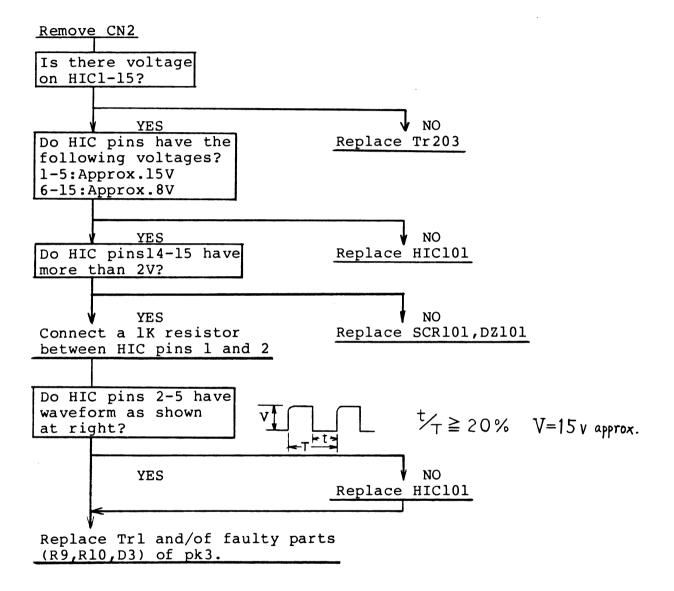

Over voltage detection level is set up at 6 - 7V by zener diode(DZ101). If output voltage exceed the level, SCR101 becomes ON state, and the terminal 14 (9) of control IC is forced to grand level, stopping oscillation. 1. Application

This manual is applicable only for the maintenance and repair of the PSS166-1801 power supply Units.

- 2. Troubleshooting and Repair Procedure

- 2-1. Disassembly

- a) Unplug the AC input cord.

Unscrew 10 flat head screws and remove both top and rear covers

- b) Unscrew 3 screws shown marked with a dot symbol (.) and the 2 screws marked with arrows (←) (5 screws in all). Then pull the plate in the direction of the large arrow (⇒).

#### 2-2. No+5V generated

Confirm the presence of +5V on the load side. If OK, mechanically disassemble the power supply, unit by unit. Check for the presence of cracks, rubbish, or obviously faulty parts. Then perform the following tests in sequence.

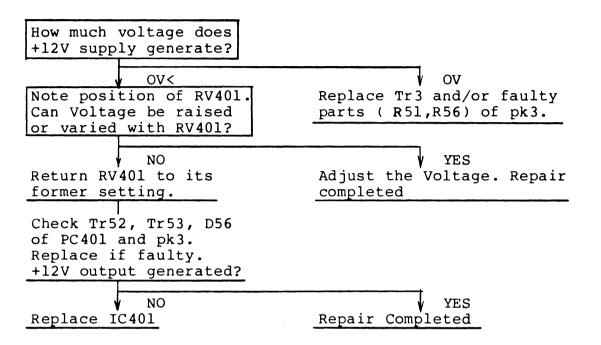

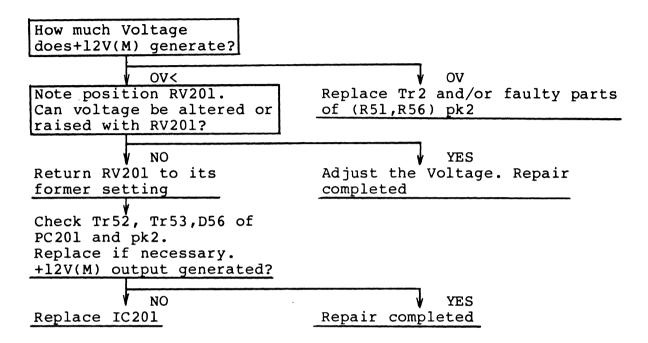

### 2-3. No+12V, -12V generated

Confirm the presence of 12V on the load side. If OK, mechanically disassemble the power supply, unit by unit. Check for the presence of cracks, rubbish, or obviously faulty parts. Then perform the following tests in sequence.

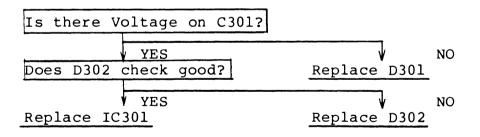

### 2-4. No-12Vgenerated

Confirm the presence of -12V on the load side. If OK, mechanically disassemble the power supply, unit by unit. Check for the presence of cracks, rubbish, or obviously faulty parts. Then perform the following tests in sequence.

### 2-5. No+12V(M), +5Vgenerated

Confirm the presence of +12V(M) If OK, mechanically disassemble the power supply, unit by unit. Check for the presence of cracks, rubbish, or obviously faulty parts. Then perform the following tests in sequence.

## 2-6. When a fuse is blown

.

Mechanically disassemble the power supply, unit by unit. Check for the presence of cracks, rubbish, or obviausly faulty parts. Then perform the following tests in sequence.

| Remove CN2.<br>Remove the correct | or line of Tr2.                                       |                                                              |

|-----------------------------------|-------------------------------------------------------|--------------------------------------------------------------|

| ¥                                 |                                                       |                                                              |

| Replace the fuse an               | nd                                                    |                                                              |

| check power supply                | operation                                             |                                                              |

| Fuse blows.                       | Supply works w                                        |                                                              |

| Replace Tr3 or<br>refer to Item   |                                                       |                                                              |

| 2-3                               | Fuse blows.<br>Replace Tr2 or<br>refer to Item<br>2-5 | Supply works well.<br>Replace Trl or<br>refer to Item<br>2-2 |

2-7. No output generated, but fuse is OK

Mechanically disassemble the power supply, unit by unit. Check for the presence of cracks, rubbish, or obviously faulty parts. Then perform the following tests in sequence.

| Check values of R2<br>Values are normal? |                                                                                                                  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| YES<br>Replace D                         | Replace R2                                                                                                       |

|                                          | After <b>replacement</b> ,<br>check voltage across both<br>resistors. If voltage is more<br>than 2Vac, continue. |

|                                          | Does D4<br>check good?<br>VYES NO<br>Replace TAC1 Replace D4                                                     |

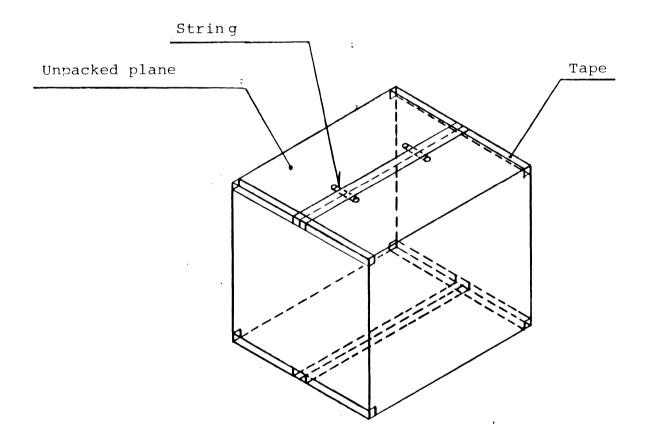

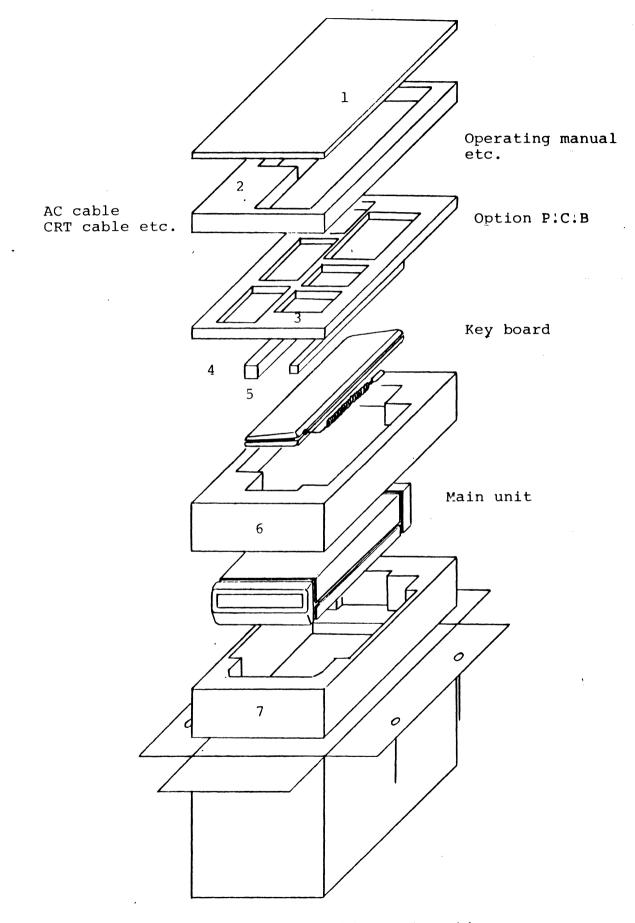

- 1-1 Unpacking

- 1-1-1 Unpacking procedures

(See Figs. 1-1-1 and 1-1-2.)

- (1) Remove the tapes attached to three packed planes.

- (2) Loosen, two strings fastend at the rivets.

- (3) Unwrap the packed planes.

- (4) Take out styrofoam (1) from the box.

- (5) Take out the AC cable, CRT Cable, Operating manual etc. from the box.

- (6) Take out styrofoam (2) from the box.

- (7) Take out the P.C.B option from the box.

- (8) Take out styrofoam (3) from the box.

- (9) Take out styrofoam (4) and (5) from the box.

- (10) Take out Key Board from the box.

- (11) Take out styrofoam (6) from the box.

- (12) Take out Main Unit from the box.

- (13) Take out styrofoam (7) from the box.

- (14) Take out each component from the unwrapped packages.

1-1-2 Notes on unpacking

- (1) Handle the parts according to the notes written on the corrugated cardboard box.

- (2) Check whether there is a damaged part or not.

- (3) Check whether there is a flaw in the rust or not.

- (4) Check whether there are such parts unnecessary for constructing as wire scobs, screws, etc. or not.

## 1-2 Packing

# 1-2-1 Packing procedures

Pack the corrugated cardboard box in the reverse order of the unpacking procedures.

- 1-2-2 Notes on packing

- Check whether the set of components to be packed is complete or not, before packing.

Fig. 1-1-1 Unpacking and packing

Fig. 1-1-2 Unpacking and packing

## 2. CRITERIA FOR MAINTENANCE

This maintenance standard prescribes the rules on PEOPLE maintenance.

# 2-1 Installation Criteria

These criteria explains on procedures or notes when users unpack the box, construct and adjust the components packed depending on the packing specification by manufacturers.

## 2-1-1 Installation conditions

- (1) Standard layout

The standard layout on PEOPLE is shown in Fig.

2-1-1.

The cord for power source is connected to the back of PEOPLE.

- (2) Maintenance area

For the maintenance work, the area within one meter around PEOPLE is required as a maintenance area. However, if there is another space for maintenance work, the maintenance area is not required.

2-2 Disassembly, Assembly, and Adjustment

2-2-1 Disassembly and Assembly

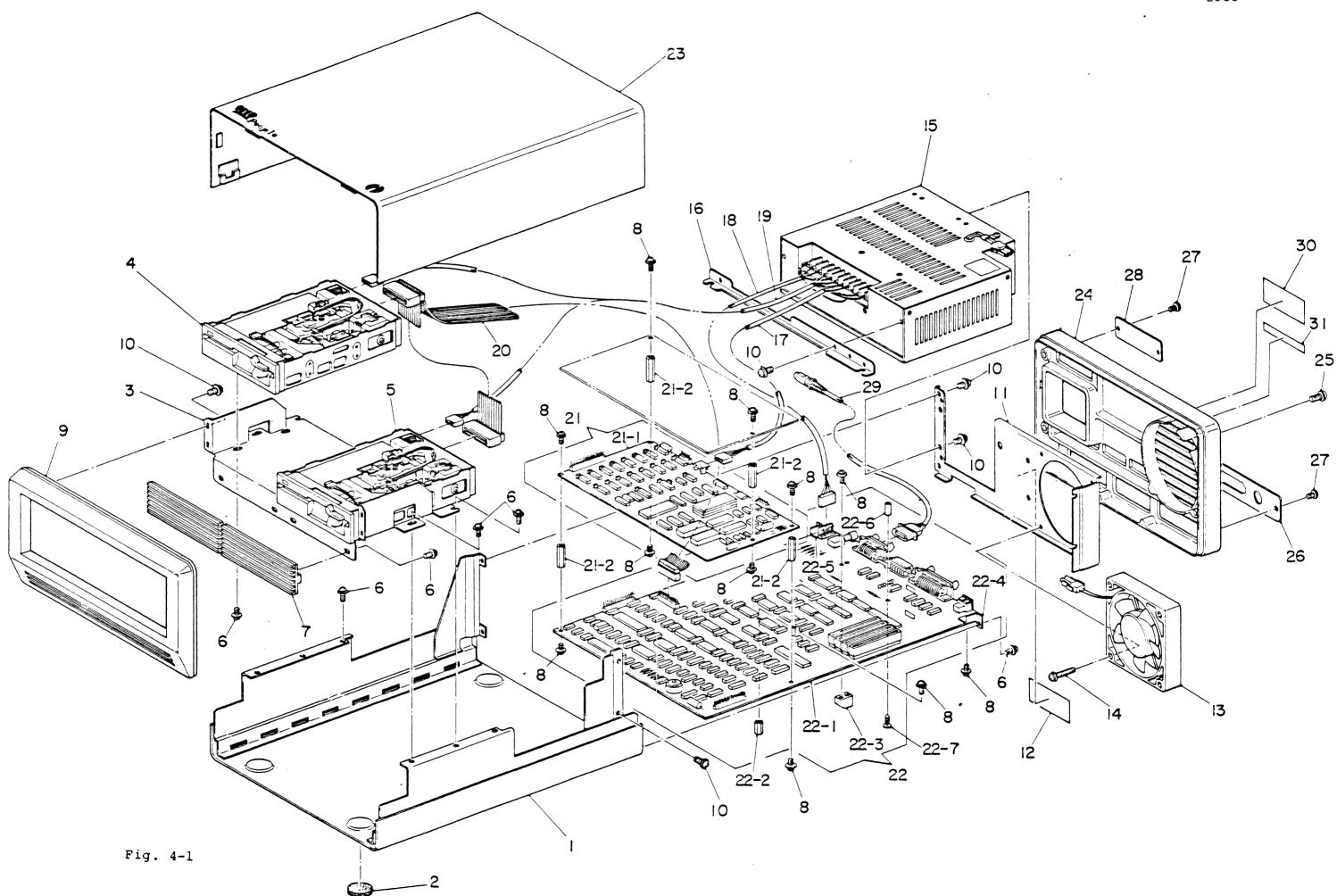

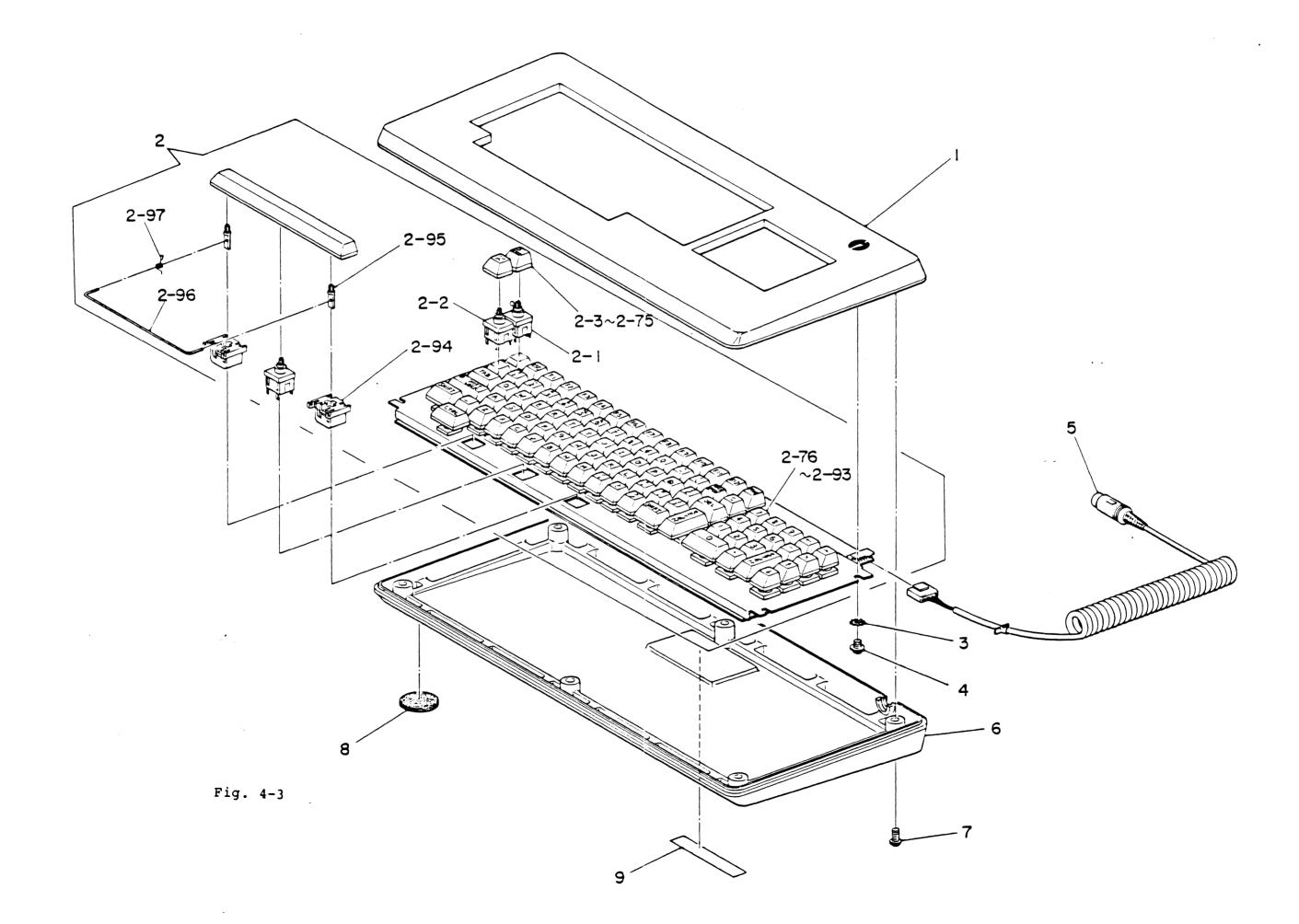

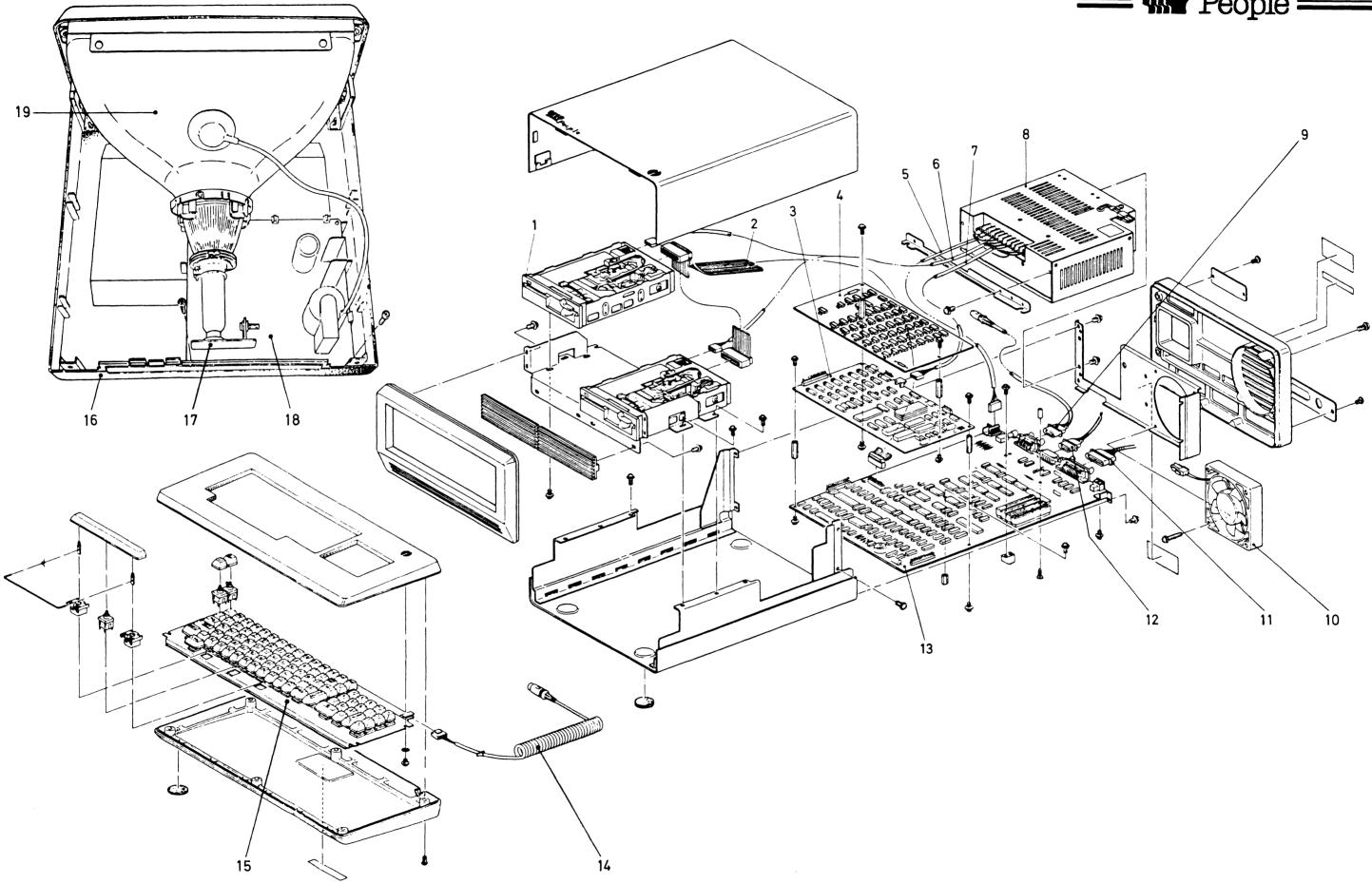

An explanation is given here as to the parts whose handling requires a specific knowledge and technique. Please refer to Fig. 4-1 page-2035 and Fig. 4-3 page-2036, which show the disassembled parts stereoscopically, with regard to the handling of other parts.

- (1) Cover (See Fig. 4-1 page-2035) Remove the cover (No. 23) as follows:

- (a) Dismount the Panel R (No. 24).

- (b) Pull the cover slightly backward, then lift it out of its place, and set it aside.

- Note: Install the cover by reversing the procedure mentioned above.

- (2) Power Supply (See Fig. 4-1 page-2035) Remove the power supply (No. 15) according to the following procedure:

- (a) Dismount the panel R (No.24).

- (b) Remove the cover (N0.23).

- (c) Remove the two screws on the rear side and loosen the two screws on the lateral sides on the screw and washer assembly (N0.10) which fastens the back panel (No.11).

- (d) Loosen all the screws on the screw and washer assembly (N0.6) which fastens the bracket P (N0.16).

- - March 2000 Constraints

March 2000 Constr

- ner a ser la companya de la companya

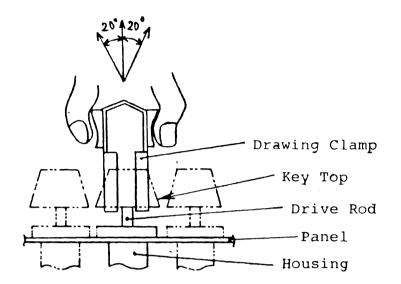

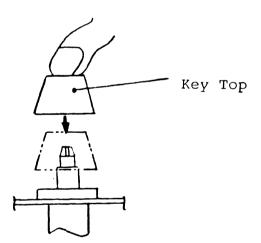

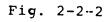

(3) Key Top (See Fig. 2-2-1)

Removal of the key top (No.2-4 to 2-46, No.2-48 to 2-93) is effected by drawing it out with the use of a drawing clamp A. Drawing should be carried out by keeping the drawing clamp A in the range of angles shown in Fig. 2-2-1.

Note: Caution should be exercised in inserting the key top not to tilt it.

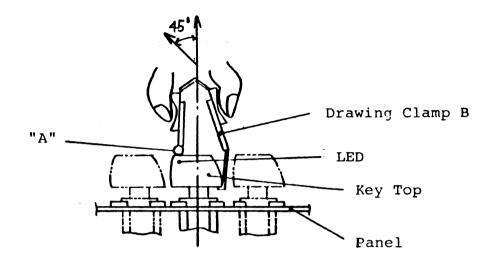

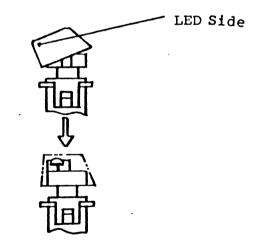

(4) Key Top with LED (See Fig. 2-2-2)

Remove the key top with LED (NO. 2-3, No.2-47) by drawing it out with the use of a drawing clamp B. In drawing it out, utilize the principles of the lever and fulcrum at the point "A". In assembling, insert the key top first from LED Side.

Fig. 2-2-1

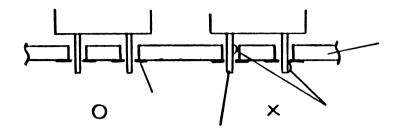

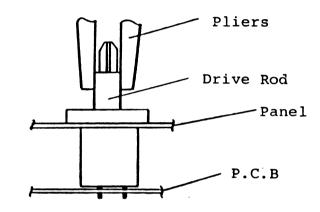

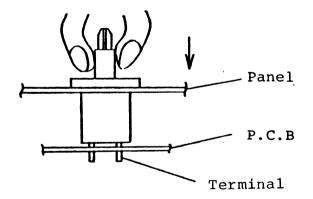

(5) Switch (See Fig. 2-2-3)

Replacement of the switches is conducted as follows.

(a) Suck up the solder of the terminals of the switch to be replaced from the land of the P.C.B. with the use of a suction solder disposer. Since the terminals are bent, the terminals must be straightened before the solder is sucked up.

The solder must be removed thoroughly, because the land is apt to be damaged if the removal of solder is not satisfactory.

- (b) Hold the switch firmly by the drive rod with pliers and pull out the switch from the panel.

- (c) After smoothing the soldered parts on the land of the P.C.B., insert a new switch into the holes on the land of the P.C.B. securely, paying close attention to the position of the switch on the panel and bend of the terminals.

- (d) Check and confirm that the terminals are surely put out through the P.C.B. and solder the terminals with a soldering iron and solder. Soldering should be completed in the shortest possible time.

- (e) Finalize the soldering work by wiping off the flux from the soldered parts with a piece of cloth soaked with alcohol.

2009

Fig. 2-2-3

- (6) Space Key Top (See Fig. 4-3) Removal of the space key top (No.2-75) is carried out as follows:

- (a) Pull out the key top holding it both side S.

- (b) Remove the link from the link holder.

- (c) Remove the link from the drive rod.

- (d) Remove the drive rods from the key top.

Assembly of the space key top is carried out as follows:

- (f) Insert the two drive rods into the key top. The rear side and front side of the drive rod can be known by the size of the holes. The hole of smaller size should be on your side.

- (g) Fix the link holder to the panel.

- (h) Insert the spring into the link. One end of the spring has a U-bend and the other end has an L-bend and insertion should be made from the L-bend. The spring should be fixed to the left side.

- (k) Hook on the U-bend of the spring to the bottom of the link.

- Insert the link into the hole on the drive rod of the space key top, exercising caution not to let the spring fall out of the link.

(m) Insert the space key top fitted with the link

into the link holder. At this time, put the

L-bend of the spring into the spring hole of the

link holder.

## 2-2-2 Adjustment

Adjustment is made by running a test program after loading the test program chosen from the floppy disks for testing use.

As for the procedure of the operation, please refer to the Test Program Operating Manual.

.

# 2-3-1 Criteria for cleaning

The following parts must be clean when the maintenance for PEOPLE is served, or when PEOPLE is checked regularly.

| Item | Part to be<br>cleaned | Contents of cleaning                                                                                                                                                                                                                | Time necessary<br>for cleaning |

|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1    | Outer<br>surfaces     | Wipe the dust etc, with the<br>soft cloth. For the parts<br>much stained, wipe them softly<br>using the soft cloth soaked<br>with alcohol. Thinner,<br>benzine, etc, must not be used                                               | For five to<br>ten minutes     |

| 2    | CRT ,                 | Wipe the dust or the stain on<br>the Braun tube. When it is<br>much stained, wipe it softly<br>with the soft cloth soaked<br>with alcohol.                                                                                          | For one<br>minute              |

| 3    | FDD                   | The magnetic head must not be<br>cleaned with an applicator,<br>etc. directly. Clean the<br>magnetic head using a double<br>sided cleaning disk. In this<br>case, the test program only<br>for cleaning is operated in<br>the unit. | For five<br>minutes            |

# 2-3-2 Notes on others

Check the following parts when PEOPLE is checked regularly.

| Item | Part to be<br>Checked                                           | Contents of checking                                                                                                                                                                                                                                   | Time necessary<br>for checking   |

|------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1    | Looseness<br>of the<br>screw<br>in each<br>section of<br>PEOPLE | Check whether the power-source-<br>fixed, OLP2-unit-fixed, fan-<br>fixed, and floppy-disk-fixed<br>screws are loosened or not.                                                                                                                         | - Fow two to<br>three<br>minutes |

| 2    | Looseness<br>of the<br>connectors<br>(Inside<br>PEOPLE)         | <ul> <li>OLP1 unit power cable<br/>connector</li> <li>OLP2 unit power cable<br/>connector</li> <li>Floppy unit power cable<br/>connector</li> <li>Floppy unit to OLP2 unit<br/>connection cable connector</li> <li>Fan connection connector</li> </ul> | For two to<br>three<br>minutes   |

| Item | Part to be<br>cleaned                                    | Contents of cleaning                                                                                | Time necessary<br>for cleaning  |

|------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|

| 3    | Looseness<br>of the<br>connectors<br>(Outside<br>PEOPLE) | o KB unit connection connector<br>o CRT unit connection connector<br>o Printer connection connector | For two to<br>three<br>minutes  |

| 4    | Check of<br>the<br>function                              | All functions are checked by operating the test program.                                            | The maximum<br>forty<br>minutes |

# 2-3-3 Changing the parts for maintenance

(1) Floppy disk

Some of the sub-assemblies in the floppy disk must be Changed depending on the operating time and the number of operation. The part-names and the changing cycle are shown as below.

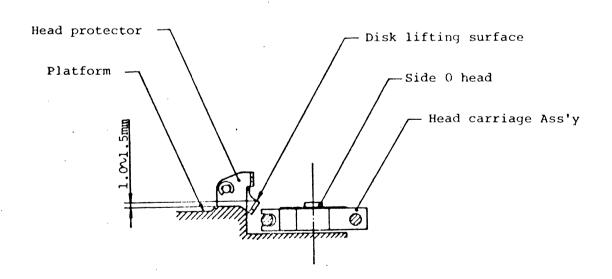

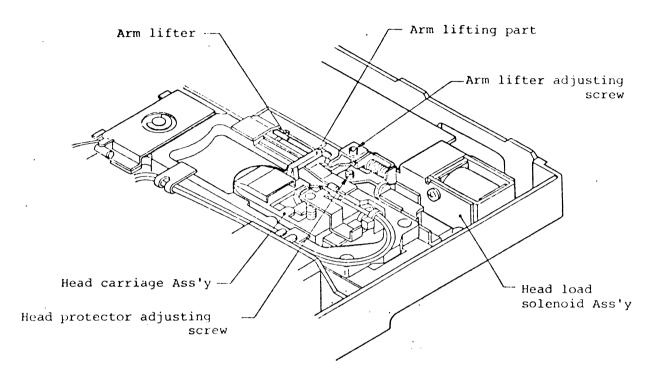

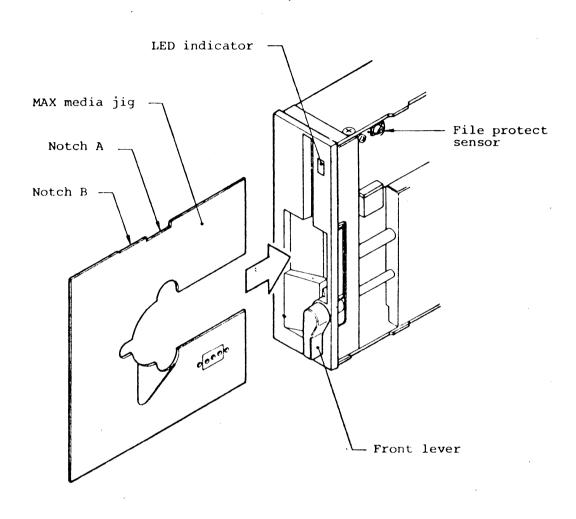

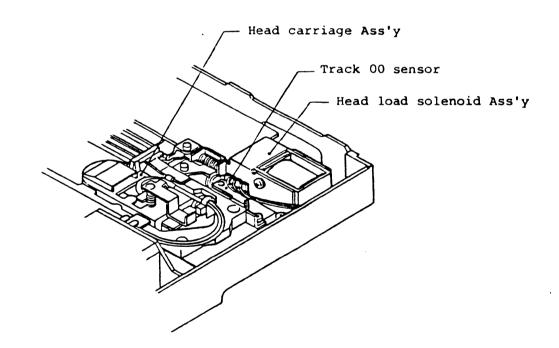

- (a) Head carriage ass'y 7000 head load & motor on hrs. or 1 x 107 seeks

- (b) Guide shaft Replace with head

carriage ass'y

- (c) Stepping motor ass'y 1 x 107 seeks

- (d) Steel belt Replace with stepping

Belt spring motor ass'y

- (e) DD motor ass'y 30000 motor on hrs.

- (f) Collet ass'y 3 x 10<sup>5</sup> clamps

- (g) Head load solenoid l x 107 head loads

ass'y

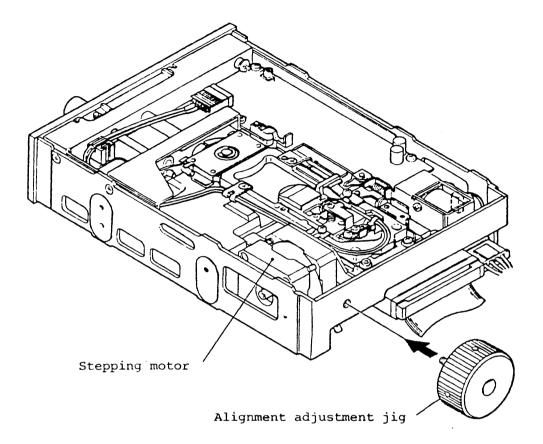

For details, refer to MINI FLEXIBLE DISK DRIVE MAINTENANCE MANUAL.

### 2-4-1 Criteria for preparing the maintenance parts.

The number and the level of the maintenance parts to be prepared are prescribed as follows, depending on the reliability of parts, the number of used parts etc. Q'TY ..... Number of the parts used in a unit \* Number to be prepared ..... Number of the maintenance parts necessary for a unit (for a year) Level to be prepared ..... Level A: Must be stored in the agencies at any time. Level B: Must be stored in the service centers at any time.

\* The rate of damages is referred to for calculating the number of maintenance, parts to be prepared.

However, the operating time is assumed to be 8 hours a day, or 300 days a year. (2,400 hours a year.)

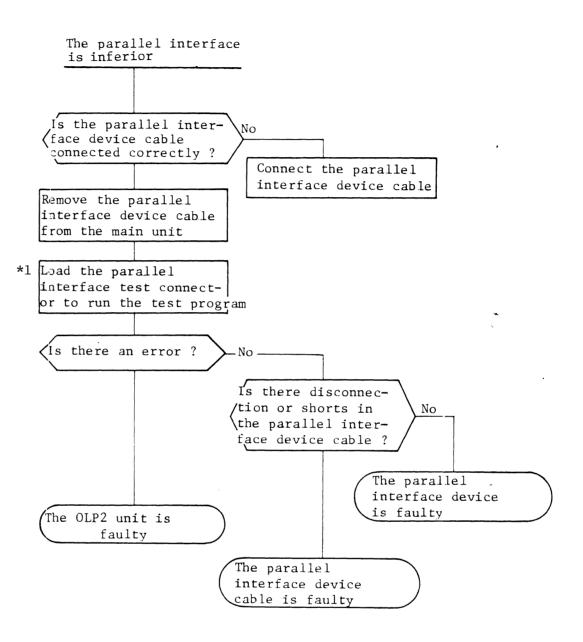

### 3. TROUBLESHOOTING

# 3.1 Introduction

When a trouble occurs in a user's house, in order to reduce systemdown time, the system is basically recovered with unit replacement and failing units carried and repaired at the service center.

The troubleshooting in this section is a manual for maintenance personnel to identify failing units. (Refer to the repair manual for repairing failing units.)

Furthermore, refer to 2.2 breakdown, assembly, and adjustment for breakdown and assembly.

## 3.2 Failing Units

This section identifies troubles of the following units.

| - OLPl unit         | - OLP2 unit     |

|---------------------|-----------------|

| - Power supply unit | - FDD unit      |

| - Fan               | - Keyboard unit |

| - Cables            | - CRT unit      |

## 3.3 Identifying Troubles

There are two methods of identifying troubles: (1) according to conditions at bootstrap time and (2) by running the test program.

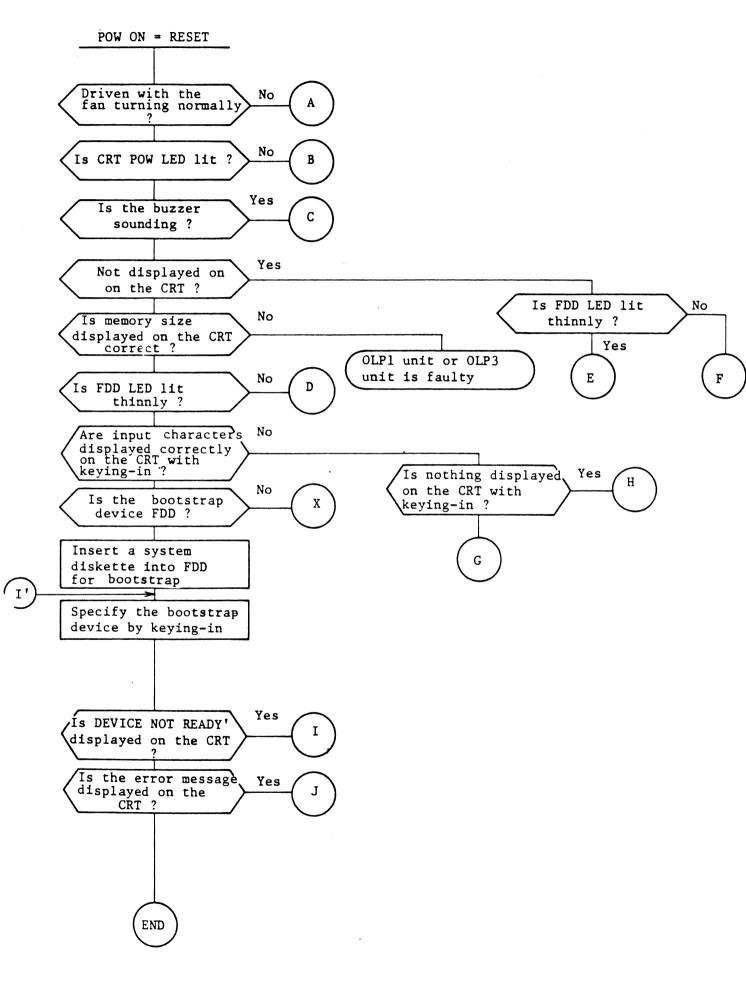

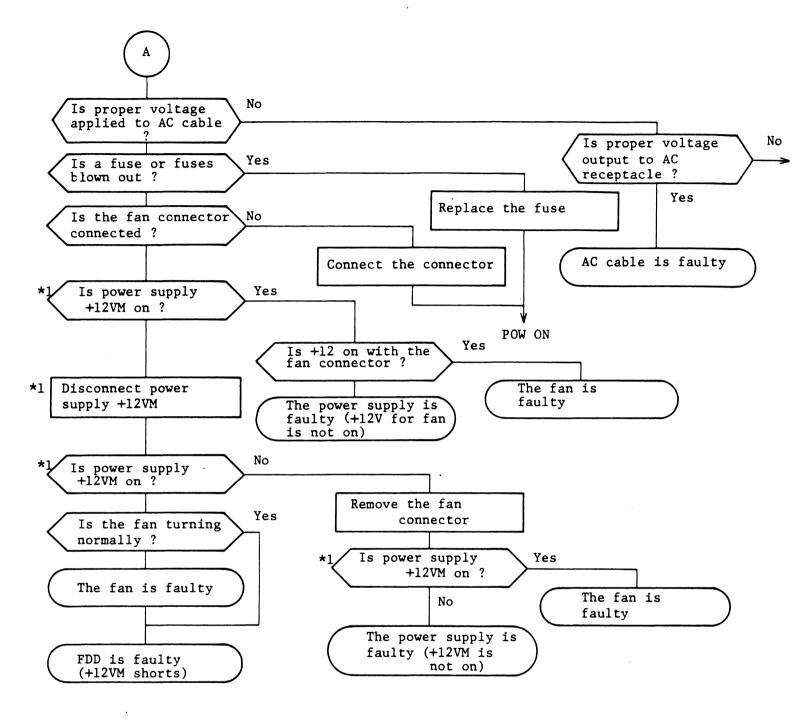

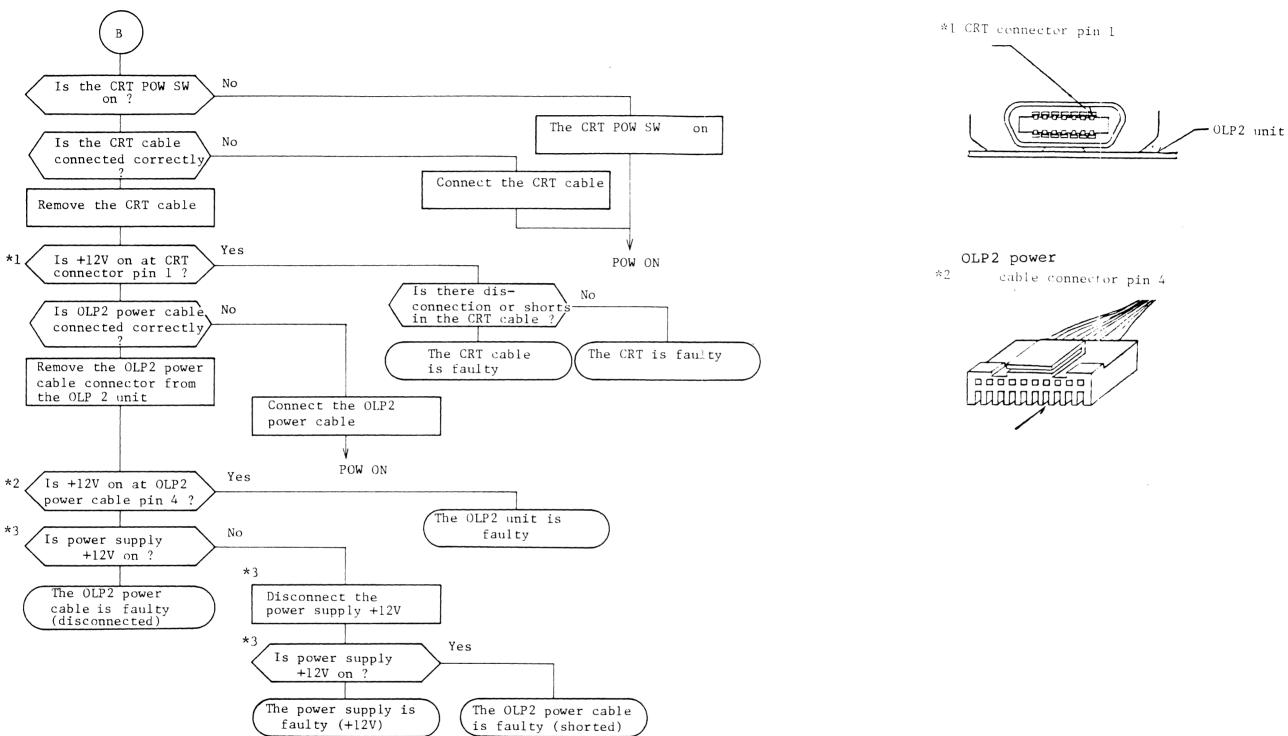

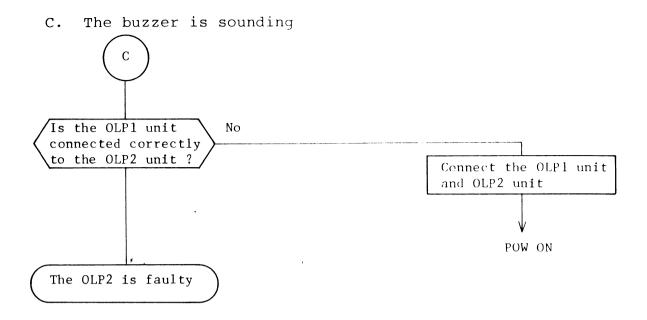

### 3.3.1 Bootstrap

Troubles are identified according to the condition of each unit in bootstrap actions when the PEOPLE system is powered on or when the reset key is pressed.

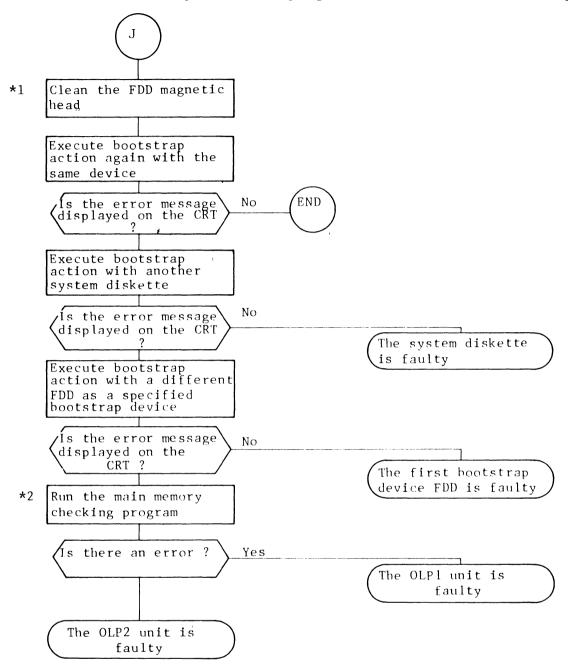

See the flowcharts. Refer to the operating manual for bootstrap procedures.

# 3.3.2 Test program

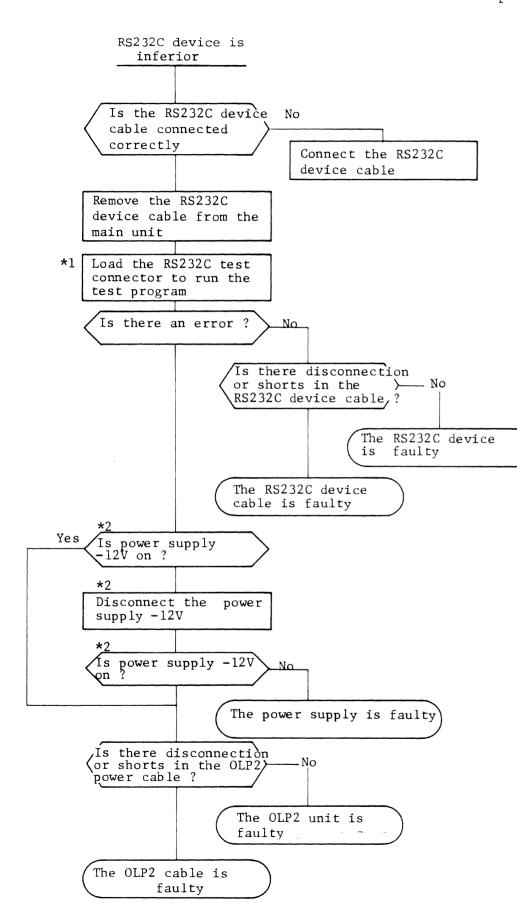

The test program refers to the RAM Resident Test Program and is used to identify troubles of RS232C, parallel interfaces, and optional units. Since these units become operational after bootstrap is completed, it is prerequisite that the CPU's peripheral (OLP1 unit), CRT, CRT controller (part of OLP 2 unit), FDD, and its controller (OPL2 unit) should operate normally. Refer to the test program operating manual for the test program running procedures.

### 3.3.1 Trouble indentification at bootstrap time

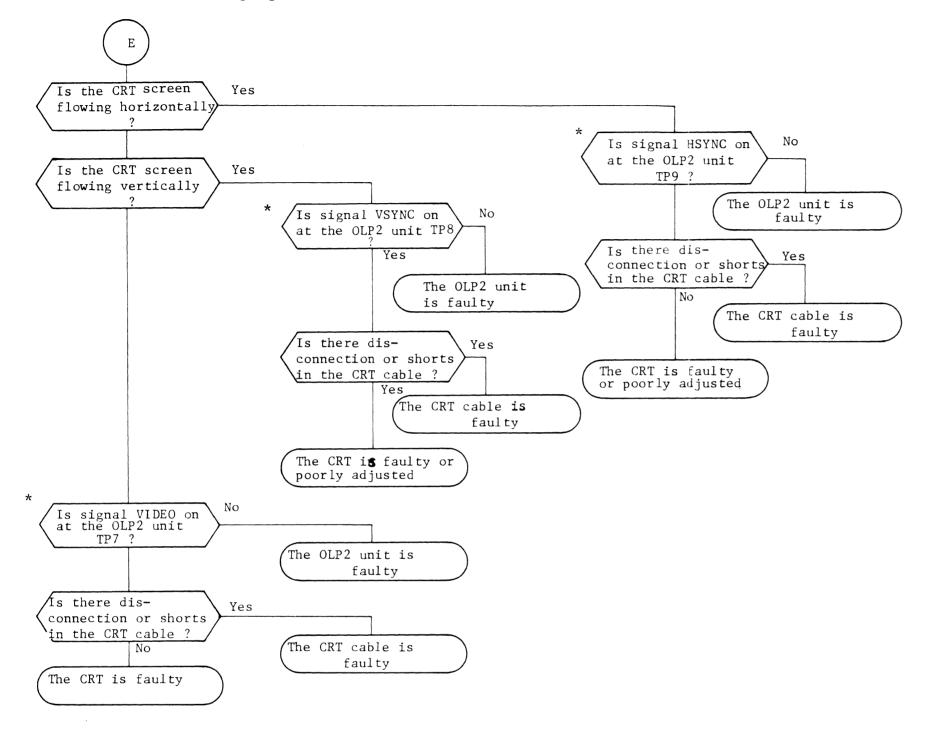

\*1 See Fig. 3.3.1 Power supply for power supply +12VM.

\*3 See Fig. 3.3.1 power supply for power supply +12V.

2021

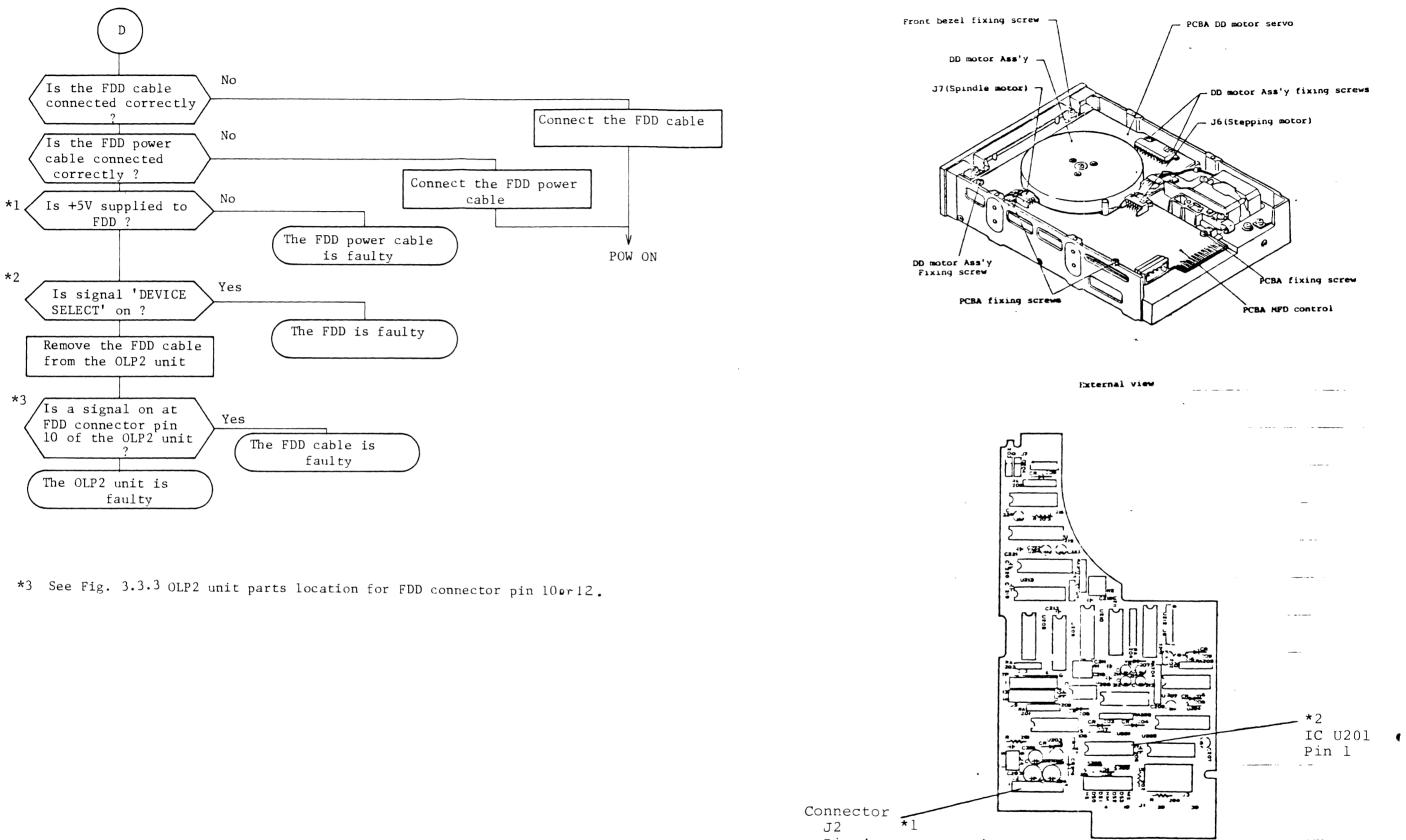

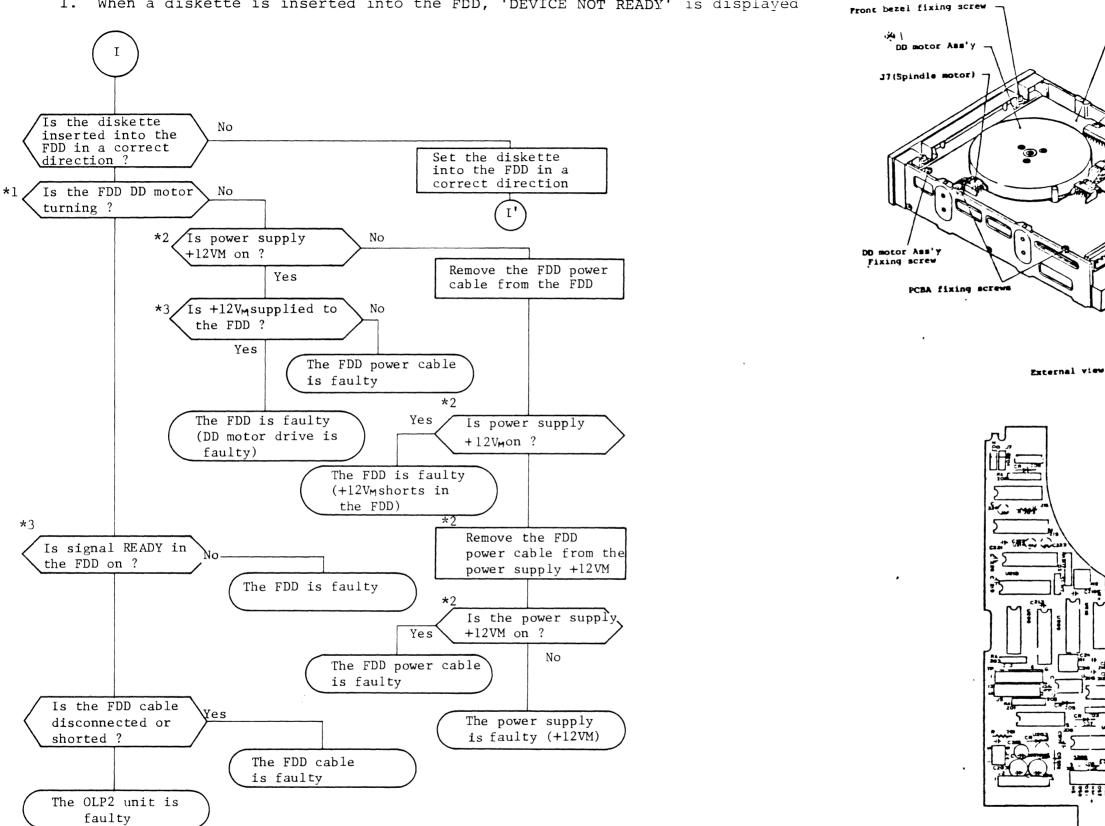

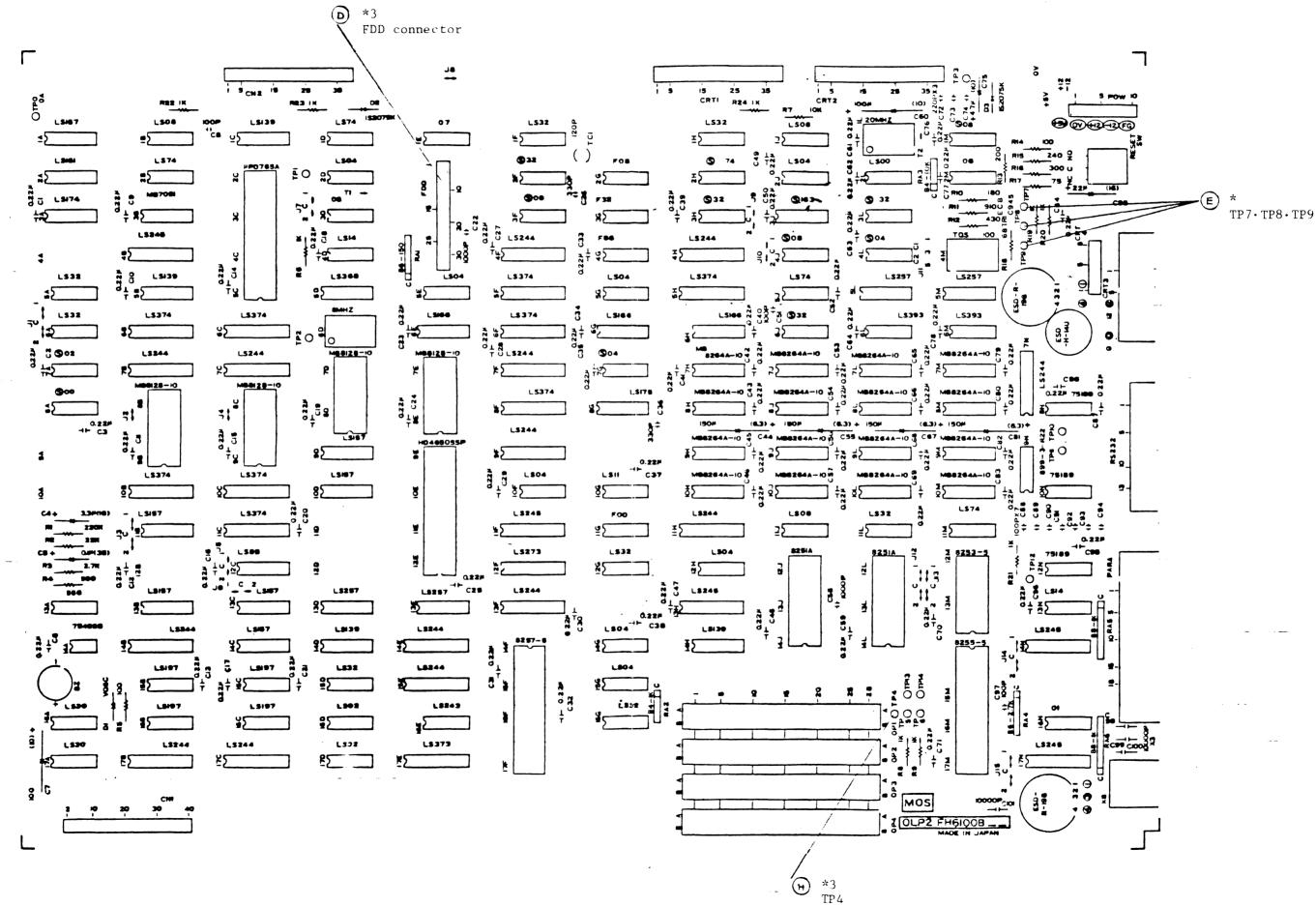

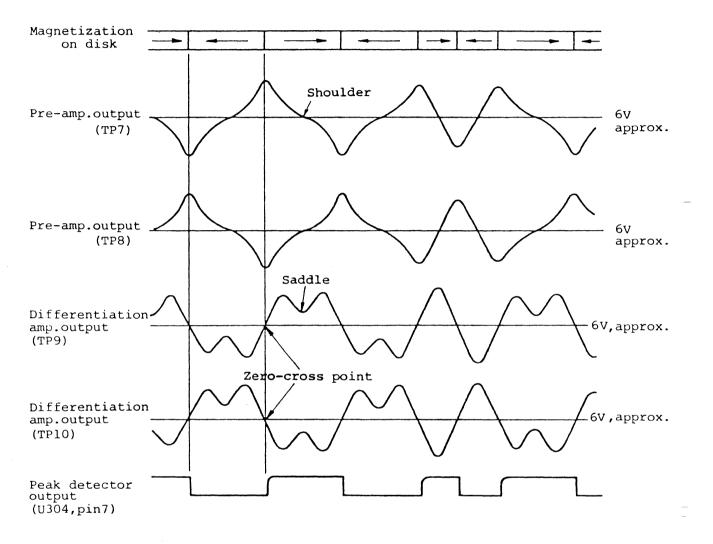

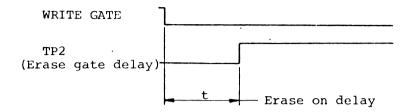

D. FDD is not driven (CRT displays correctly)

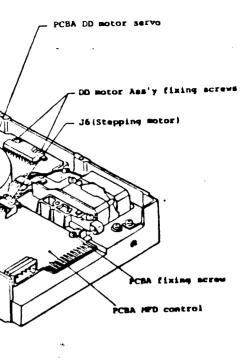

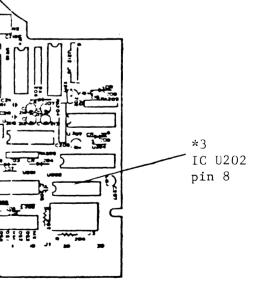

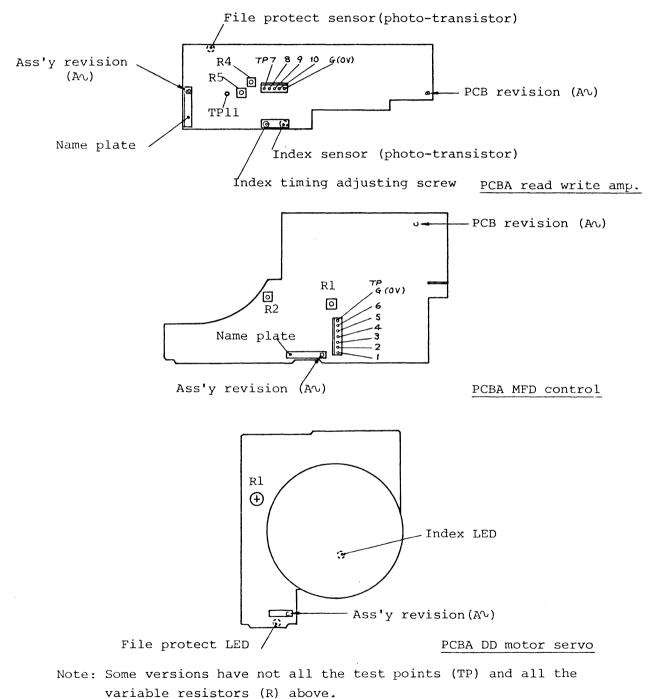

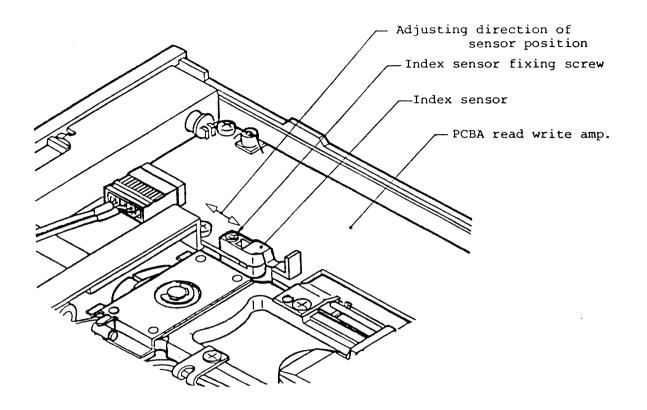

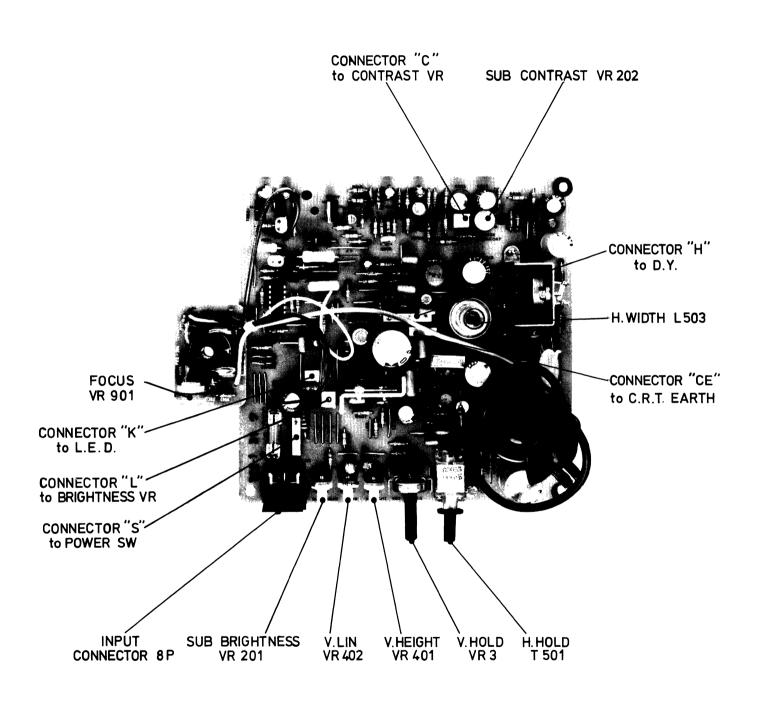

PCBA MPD CONTROL, PARTS LOCATION

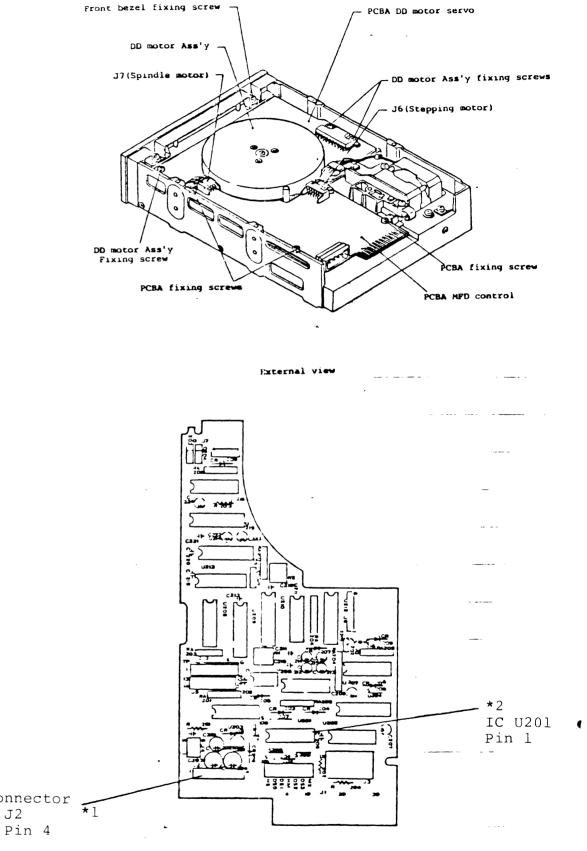

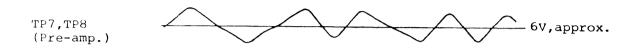

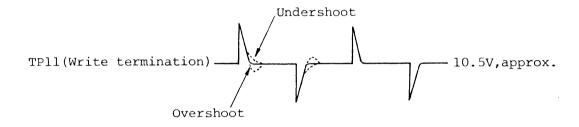

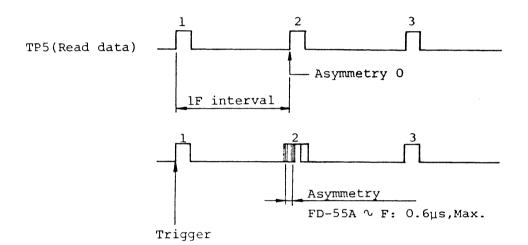

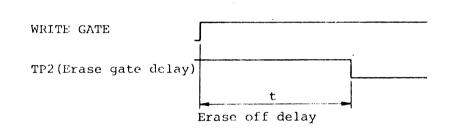

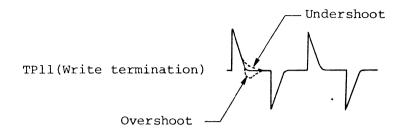

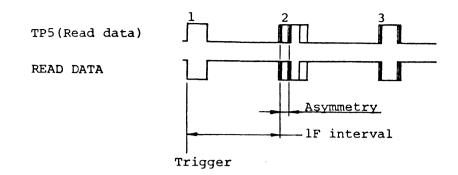

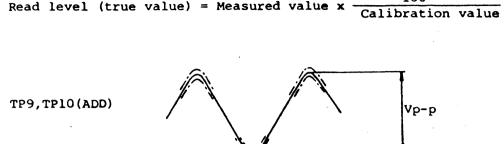

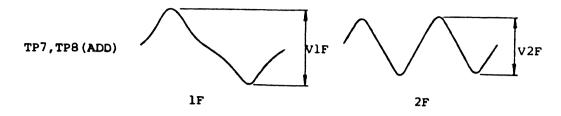

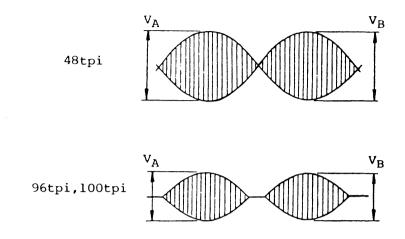

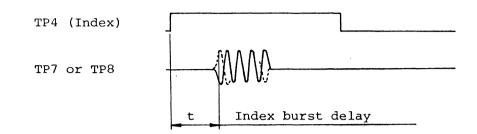

\* See Fig. 3.3.3 OLP2 unit parts location for TP7, TP8, and TP9.

# 2024

is faulty

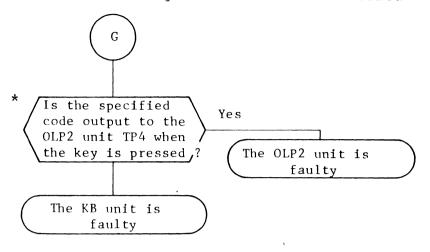

G. Erroneous key codes have been entered

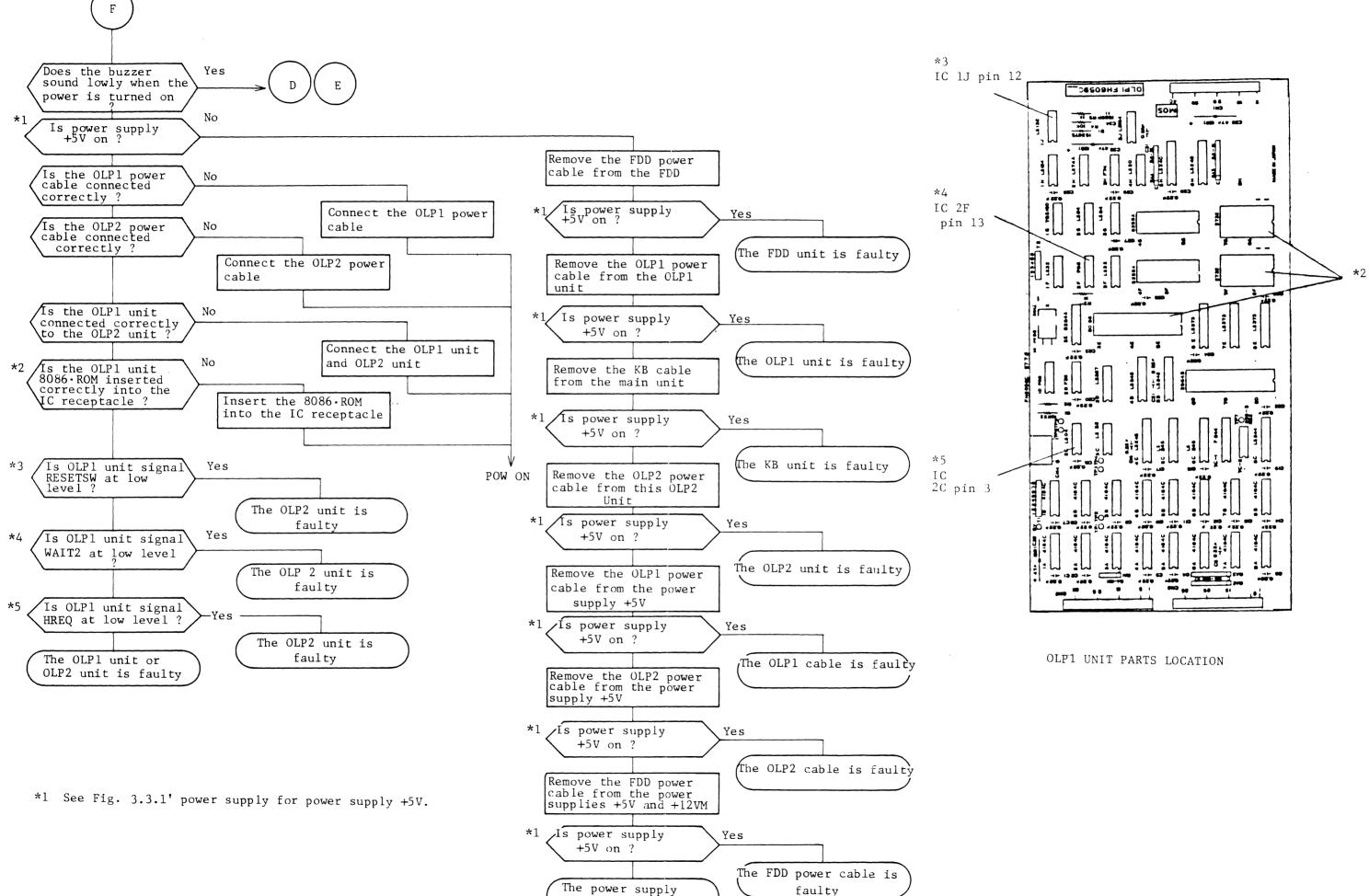

\* See Fig. 3.3.3 OLP2 unit parts location for TP4.

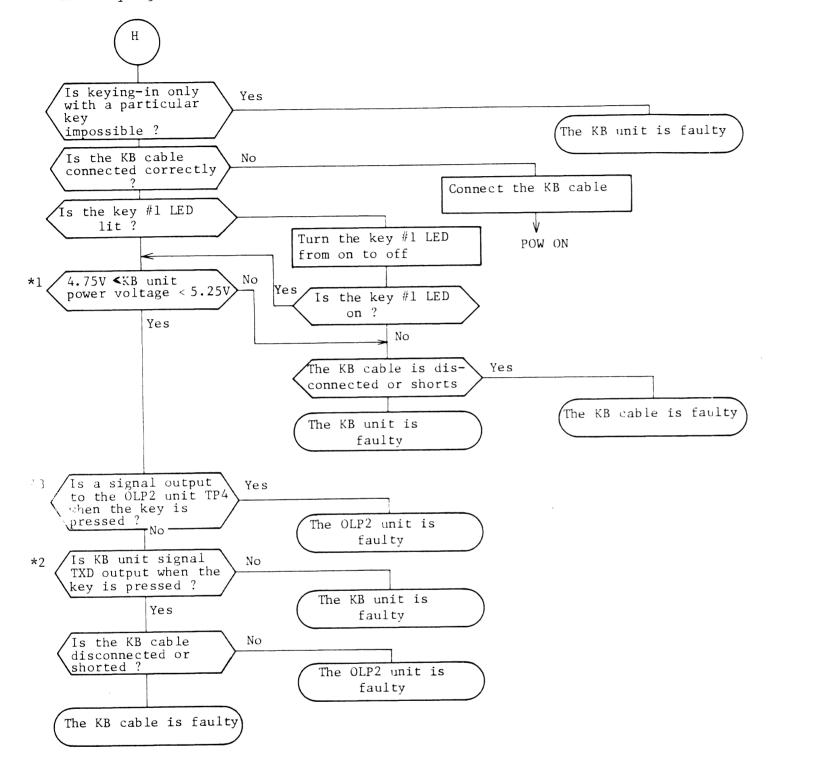

H. Keying-in is not possible

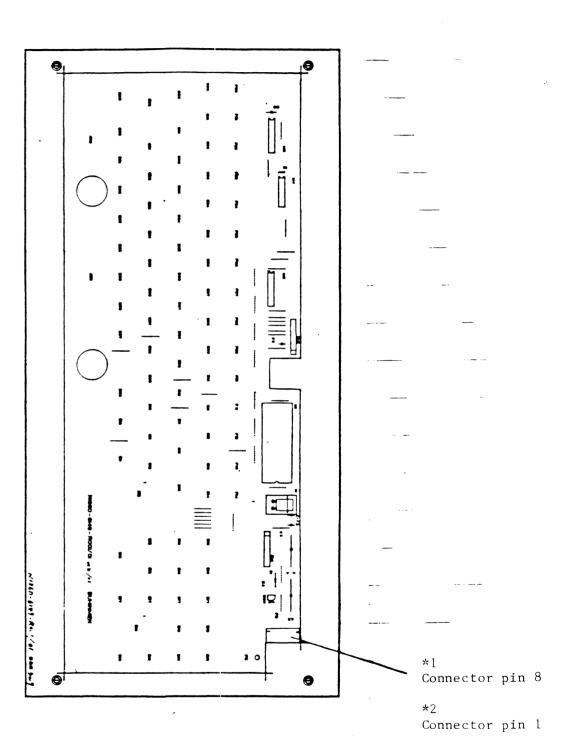

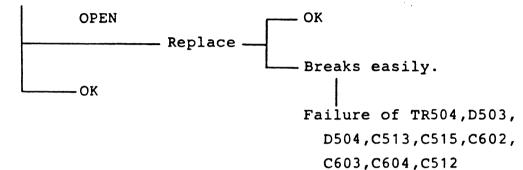

KB PARTS LOCATION