Ver-16-fachung des Sonder-ROM Bereichs

und Nutzung durch das Betriebssystem

Helmut Bernhardt (Hardware); Arnulf Sopp (Software)Die übliche Technik, das Betriebssystem zu tunen, führt in der Regel dazu, daß durch Herunter-rutschen des HIMEM der Anwender-Speicher immer kümmerlicher wird, wobei anspruchsvollere Programme zwar eine Fülle zusätzlicher Featutes des Betriebssystems zur Verfügung haben (ob sie wollen oder nicht) und dafür eventuell zu wenig Speicherplatz für sich und ihre Daten/ Variablen haben.

Zwei Möglichkeiten, wie zusätzlicher Speicherplatz geschaffen werden kann, der nicht auf Kosten des Anwenders geht, sind in 1) und 2) beschrieben. Während die 1) beschriebene Methode (vollständige Decodierung der Tastatur 3800H-3BFFH und Bereitstellen von RAM im Bereich 3900H-3BFFH) mit allen Hard- und Software- Produkten zusammen funktioniert, ist die in 2) beschriebene Erweiterung an das Vorhandensein eines herkömmlichen Expansion-Interface EG 3024 mit Sockeln für 2 x 8 dynamische RAMs gebunden und die Vervielfachung des Sonder-ROM Bereichs ist in das ganze Projekt nur als Abfallprodukt mit eingebunden.

Hier soll nun beschrieben werden, wie man die Vervielfältigung des Sonder-ROM Bereichs und gleichzeitig dessen vollständige Decodierung, so daß auch der PUNCH Befehl des GENIE-Monitors (Maschinen-Programme auf Cassette schreiben) aus 3) funktioniert, durchführen kann, ohne das aufwendige Banking-Board zur Verwaltung zusätzlicher dynamischer RAMs aufbauen zu müssen.

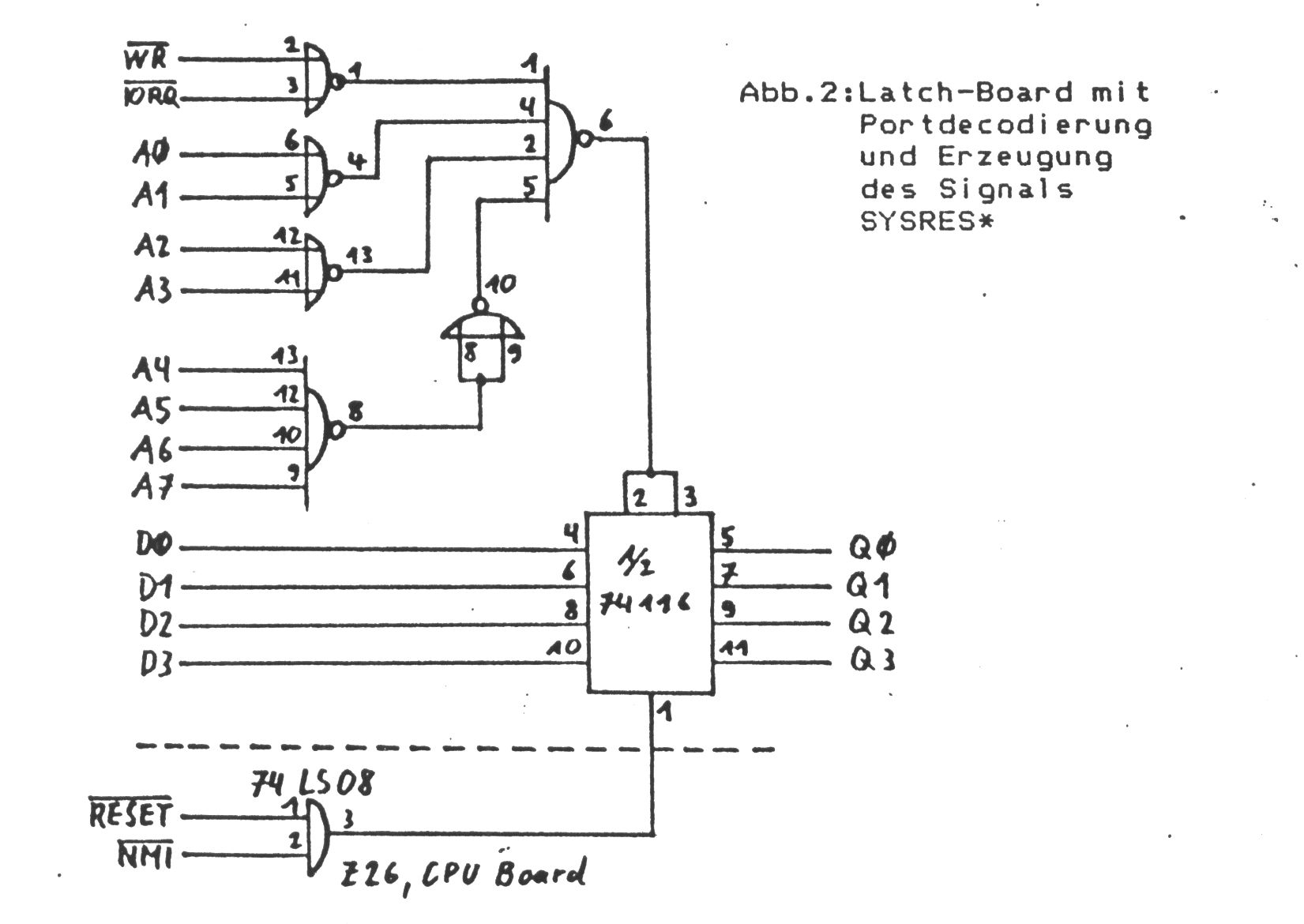

Zunächst grob qualitativ das Prinzip der Schaltung:In ein Portdecodiertes Latch (74116) wird ein 4-Bit-Wort als Nummer der einzuschaltenden Speicherbank eingetragen. Dieses 4-Bit-Wort liegt anschließend am Ausgang des Latch ständig an, bis ein anderes Wort eingetragen wird. Die Latch-Ausgänge werden an einen 1-aus-16-Decoder (74154) gelegt, der dann je nach Bitmuster an seinen 4 Eingangs-Pins den entsprechenden Ausgangs-Pin low-aktiv werden läßt, wenn seine beiden E*-Eingänge low aktiv sind. Wenn man an die E*-Eingänge das volldecodierte Freigabesignal 3000H-37DFH* für das Sonder-ROM legt, können die 16 Ausgänge des 74154 als Freigabesignale für insgesamt 16 Stück 2716-EPROMs benutzt werden.

Will man anstelle von EPROMs auch RAMS benutzen, kann man nicht einfach die Signale vom Sockel des Sonder-ROM an die 16 Speicherbausteine (2716-EPROMs oder 6116-RAMs) führen.

- werden die am Sonder-ROM Sockel anliegenden Datenleitungen über unidirektionale Treiber nur in Leserichtung mit dem Systemdatenbus verbunden, weshalb ein Schreiben in RAMs so nicht möglich ist und

- liegt an Pin 21 nicht das für RAMs nötige Signal WR* bzw. MWR* an. Dieser Pin ist einfach an +5V angeschlossen.

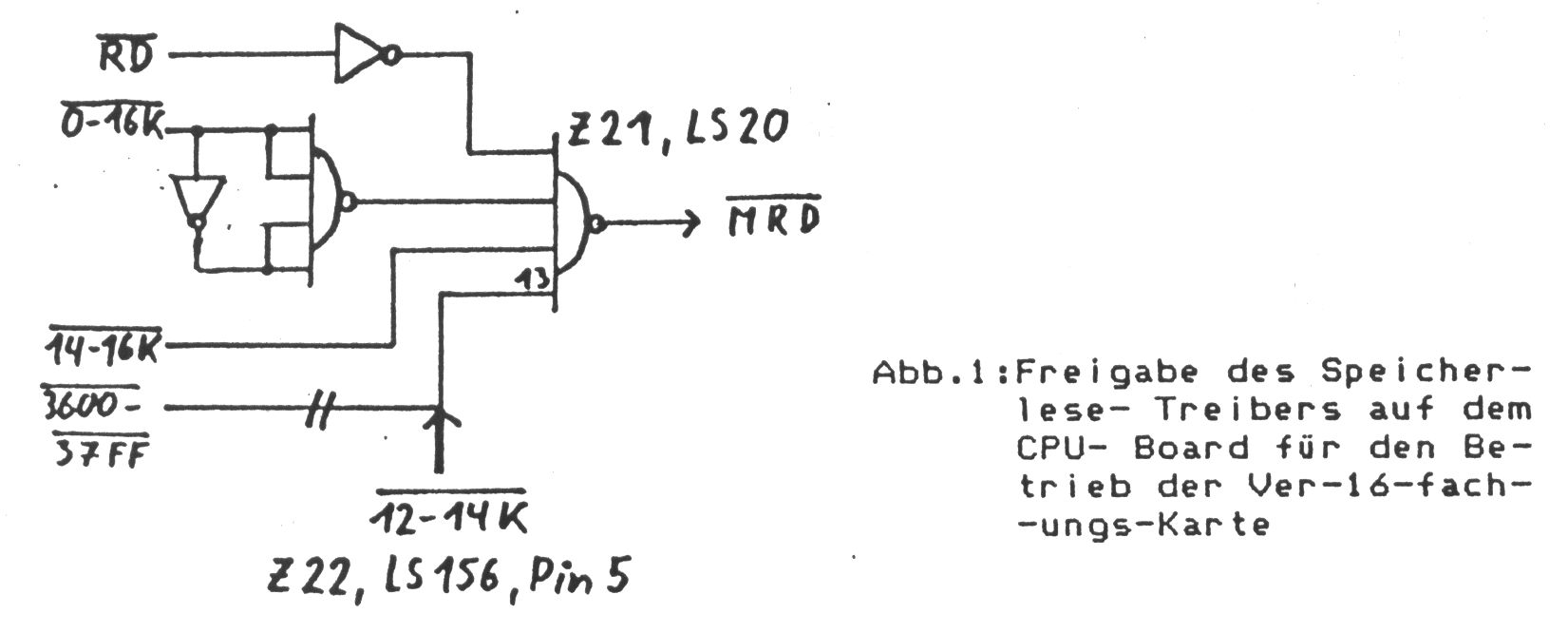

- ist an den CE*-Pin 18 Masse angelegt, und ein nicht vollständig decodiertes Freigabesignal 12-14K* (=3000-E7FFH*) ist an den Pin 20 OE* geführt, der eigentlich ein RD* oder MDR*-Signal verdient hätte. Kollisionen mit den I/O-Adressen 37E0H-37FFH werden dadurch verhindert, daß durch das Signal 3600-37FF* an Pin 13 von Z21 (74LS20) die Freigabe des Speicherlesetreibers gesperrt ist. In diesem großzügigen Abwürgen des Sonder-ROM liegt auch die Ursache des nicht funktionierenden PUNCH-Befehls.

- Die Datenleitungen zum Sockel des Sonder-ROM müssen durchtrennt werden. Die Datenpins des Sonder-ROM werden direkt mit den Ausgängen der Datenbustransceiver der CPU verbunden.

- Die Datenleitung D7 die über den Sonder-ROM Sockel an den RAM-Baustein Z34 führt, muß zwischen RAM und Sonder-ROM durchtrennt werden. D7 für Z34 muß stattdessen vom ROM Z12 an das RAM geführt werden.

- Die Leitungen zu den Pins 18 und 19 des Sonder-ROM Sockels (GND und +5V) werden durchtrennt.

- An Pin 18 des Sockels wird MRD* und an Pin 21 MWR* gelegt.

- Das Signal 3600H-37FFH wird von der Steuerung des Speicherlesetreibers abgetrennt. Stattdessen wird dort 12-14K* angelegt, sodaß der Speicherlesetreiber für den gesamten Bereich 3000H-37FFH gesperrt wird.

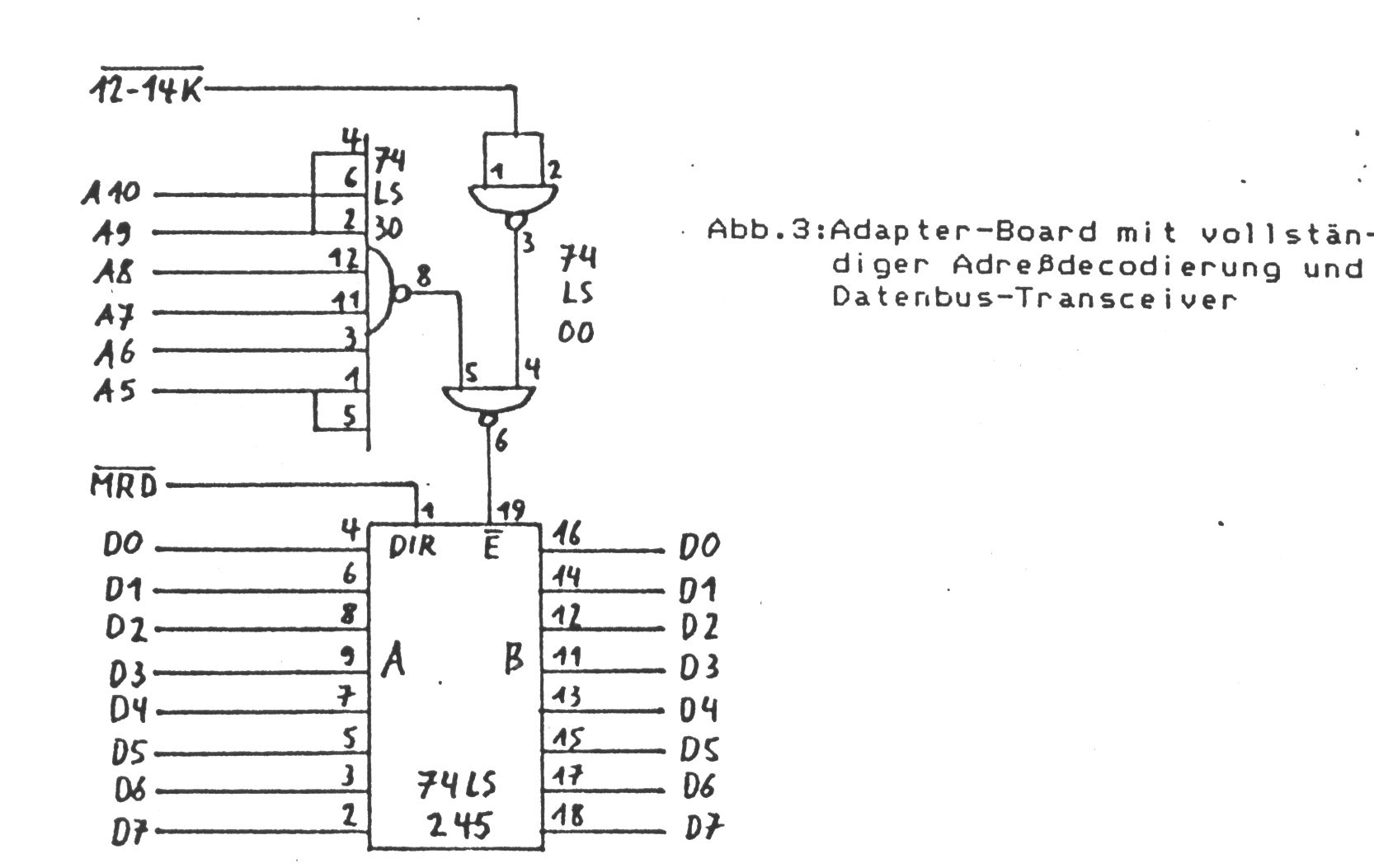

- Durch ein Flachkabel und 2 24-polige Quetschstecker und ein in dieses Kabel eingefügtes Adapter-Board wird die 16-fach-Sonder-ROM Karte mit dem wie oben beschriebenen geänderten Sonder-ROM Sockel verbunden. Das Adapter-Board bringt nicht nur die Signale CE* und MRD* auf die richtigen Pins, sondern leistet auch die volle Decodierung auf den Bereich 3000H-37DFH und stellt einen bidirektionalen Datenbus-Treiber bereit, so daß auch RAMs benutzt werden können. (Abb.3).

Die Wahl eines 74116 Latches bietet den Vorteil, daß durch AND-Verknüpfung der Signale RESET* und NMI* (ergibt das beim TRS-80 bereits vorhandene Signal SYSRES*) und anlegen an den CLEAR-Eingang des Latch nach dem Einschalten oder Drücken des RESET-Knopfes immer die Bank 0 eingestellt ist. Wenn der bisherige Sonder-ROM auf der Ver-16-fachungs Karte durch den Ausgang 0 des 1-aus-16 Decoders 74154 freigegeben wird, verhält sich der Computer wie vorher auch. Wenn keine andere Bank eingeschaltet wird, liegt im Adreßbereich 3000H-37DFH immer der Sonder-ROM vor.

Arbeitsanleitung

1) Änderungen am Sonder-ROM Sockel auf dem CPU-Board- Auf der Lötseite werden die Leitungen zu den Pins 18 und 21 des Sonder-ROM durchtrennt. An Pin 18 wird das Signal MRD* von Z15 (74LS32), Pin 11 und an Pin 21 das Signal MWR* von Z15 (74LS32), Pin 3 gelegt.

- Die Verbindung von Pin 14 des RAM Z34 mit Pin 17 des Sonder-ROM wird durchtrennt. Der Pin 14 des RAM wird stattdessen mit dem Pin 17 des ROM 3003 verbunden.

- Auf der Bestückungsseite werden (von der Mitte des CPU-Boards gezählt) die ersten 7 Leitungen zwischn ROM 3 (3003) und dem Sonder-ROM Sockel durchtrennt. Die 8. Leitung bleibt bestehen und die 9. Leitung wird ebenfalls durchtrennt. Dann werden mit isolierten Dähten auf der Lötseite folgende Verbindungen hergestellt.

| Signal | Pin des | Verbindung zu | ||

| Sockels | Pin | IC | Typ | |

| D0 | 9 | 7 | Z18 | 74LS367 |

| D1 | 10 | 9 | " | " |

| D2 | 11 | 5 | " | " |

| D3 | 13 | 13 | Z19 | " |

| D4 | 14 | 11 | " | " |

| D5 | 15 | 3 | Z18 | " |

| D6 | 16 | 13 | " | " |

| D7 | 17 | 11 | " | " |

- Die Leitung zu Pin 13 von Z21 (74LD32) wird durchtrennt. Der Pin 13 von Z21 wird mit Pin 5 von Z22 (74LS156) verbunden (Abb.1).

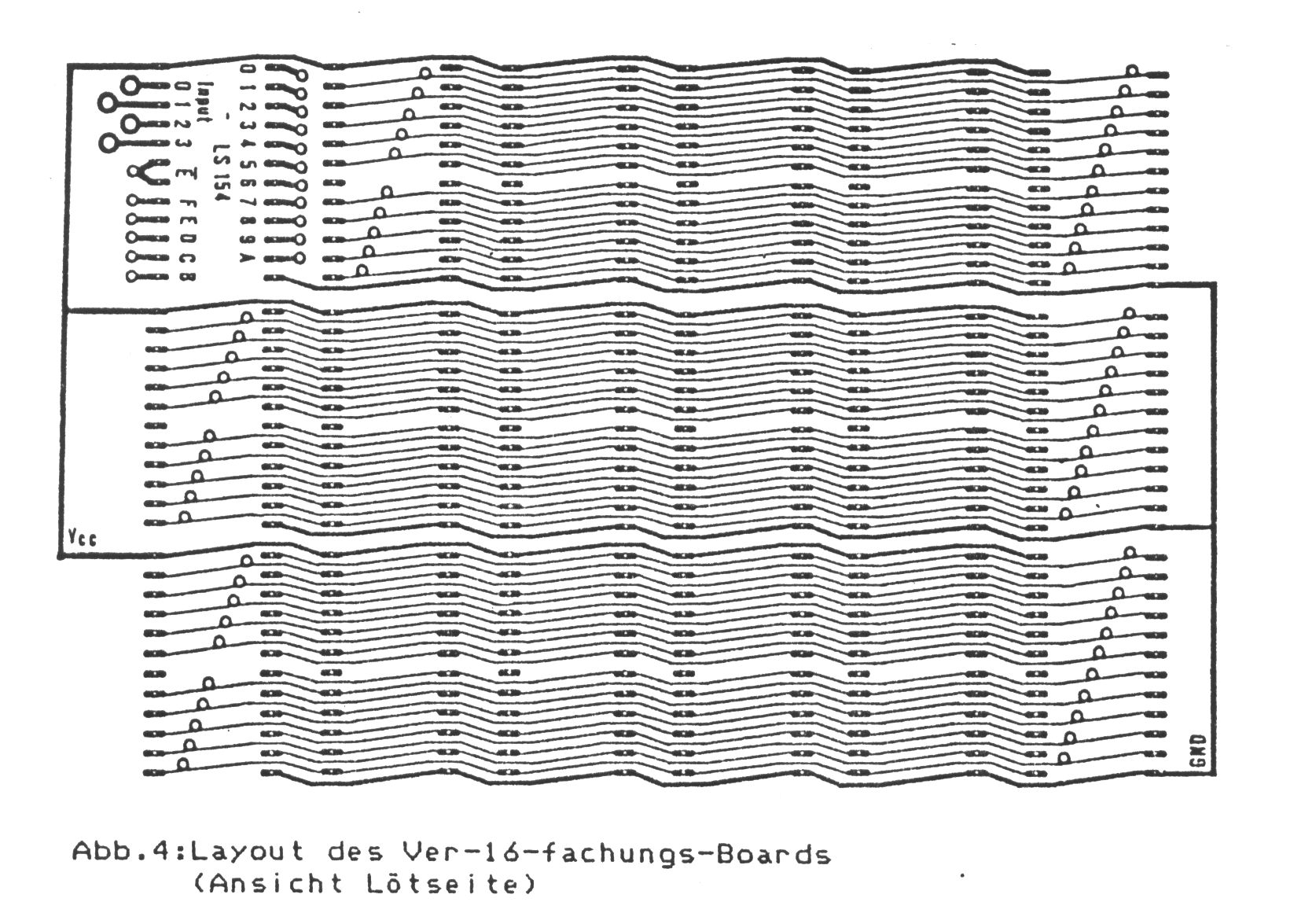

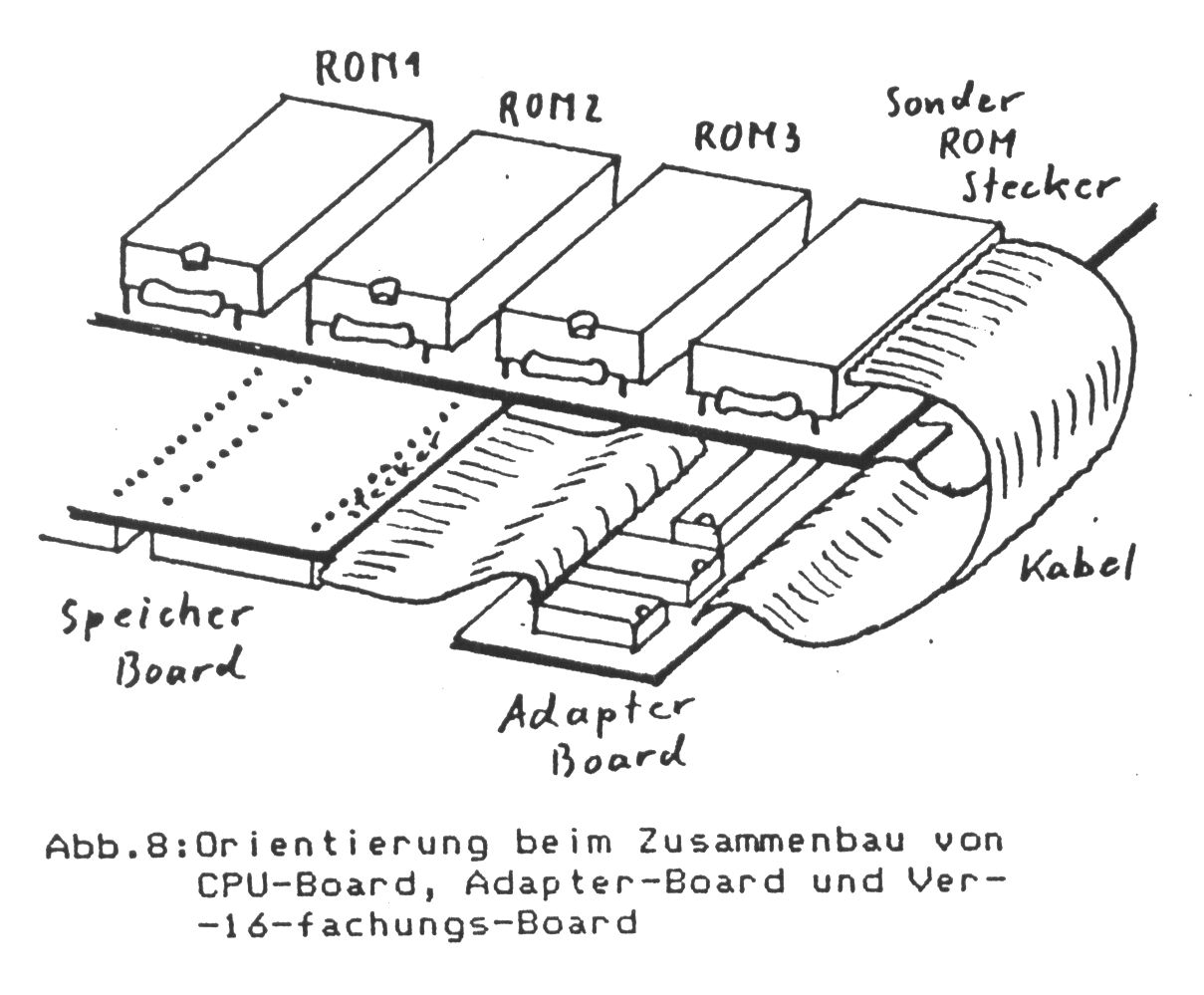

- Auf dieser Karte werden ausschließlich 24-Pin IC-Sockel eingesetzt. An der im Layout beschrifteten Position wird der 1-aus-16-Decoder74154 eingesetzt. An eine der beiden Positionen daneben wird der Stecker des Flachkabels vom Sonder-ROM Sockel auf dem CPU-Board eingesetzt. Dieser Stecker muß (außer Pin 18) mit allen seinen Pins mit den entsprechenden Pins aller Speicher-Sockel verbunden werden.

- Da innerhalb einer Reihe diese Verbindungen per Layout schon bestehen, muß muß durch Drahtbrücken bzw. freie Verdrahtungen auf der Lötseite nur noch eine Querverbindung zwischen den entsprechenden Pins der 3 Reihen hergestellt werden.

- Die nicht angeschlossenen Pins 18 aller Sockel werden mit je einem der Ausgänge 0-9, A-F des 1-aus-16-Decoders durch freie Verdrahtung auf der Lötseite verbunden. Der Pin 18 des Sockels, an den das Flachkabel führt, wird an den E*-Eingang des Decoders gelegt. Die Eingänge 10-13 des Decoders werden mit den Ausgängen Q0-Q3 des Latch 74116 verbunden.

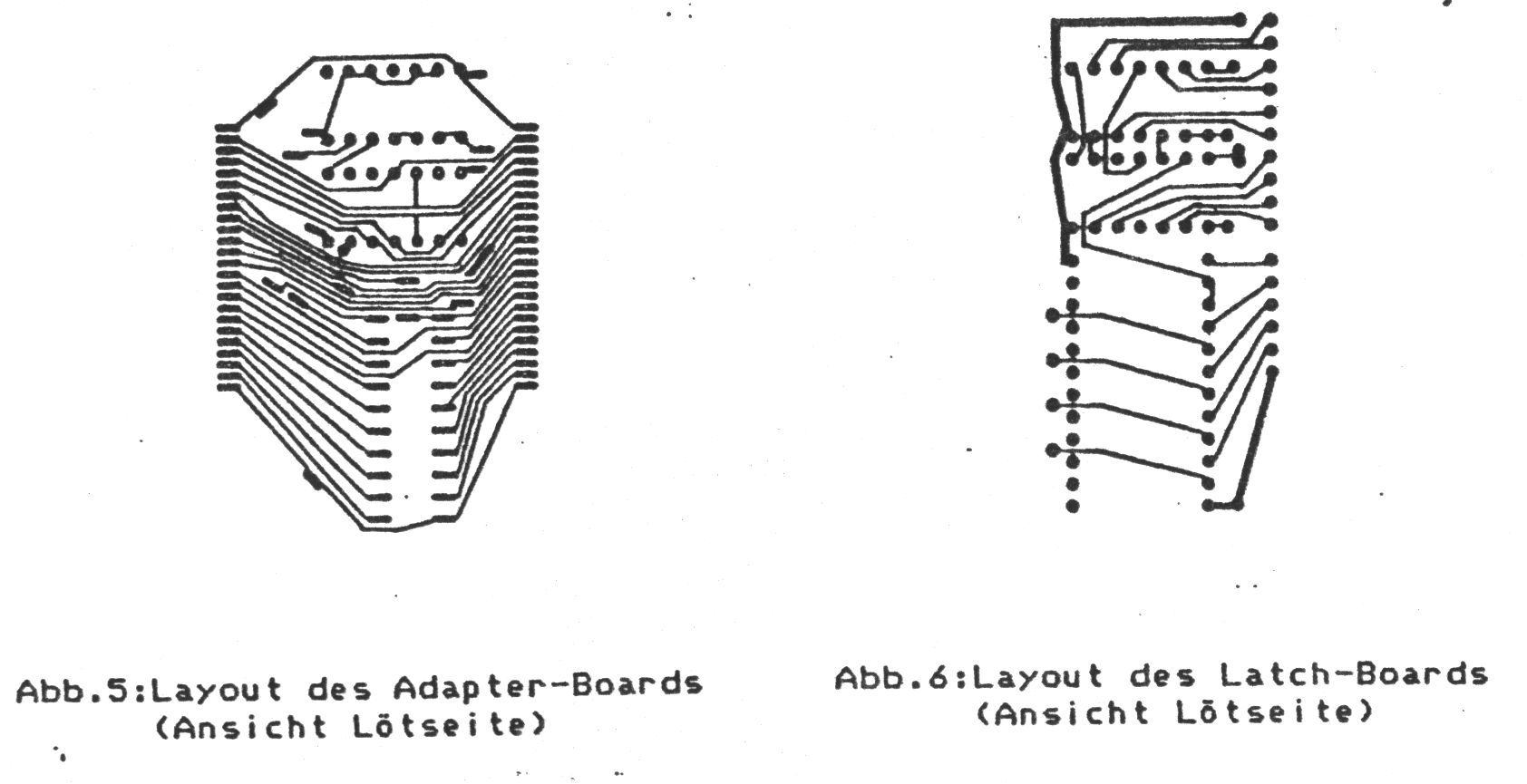

- Das Adapter-Board wird entsprechend Abb.7 u. 8 in das Flachkabel eingefügt. Dafür wird das Flachkabel an geeigneter Stelle durchgeschnitten, die Leitungen auf eine Länge von 2 cm voneinander getrennt und dann die Enden auf eine Länge von ca 3 mm abisoliert und die Enden schlank verdrillt und dünn eingezinnt.

- Wenn die Ver-16-fachungs Karte unter dem CPU-Board liegen soll und deshalb das Flachkabel nach einstecken in den Sonder-ROM Sockel vom CPU-Board wegführen soll, muß das Adapter-Board so orientiert werden, daß die Bestückungsseite zur gleichen Seite weist, wie die Stecker des Kabels. Die beiden in Kabelrichtung liegenden ICs (74LS00 und 74LS30) liegen dann links außen im Computer.

- Im Gehäuse des Computers muß ein entsprechender Pfosten der Bodenwanne abgesägt werden, damit das Board in das Gerät paßt.

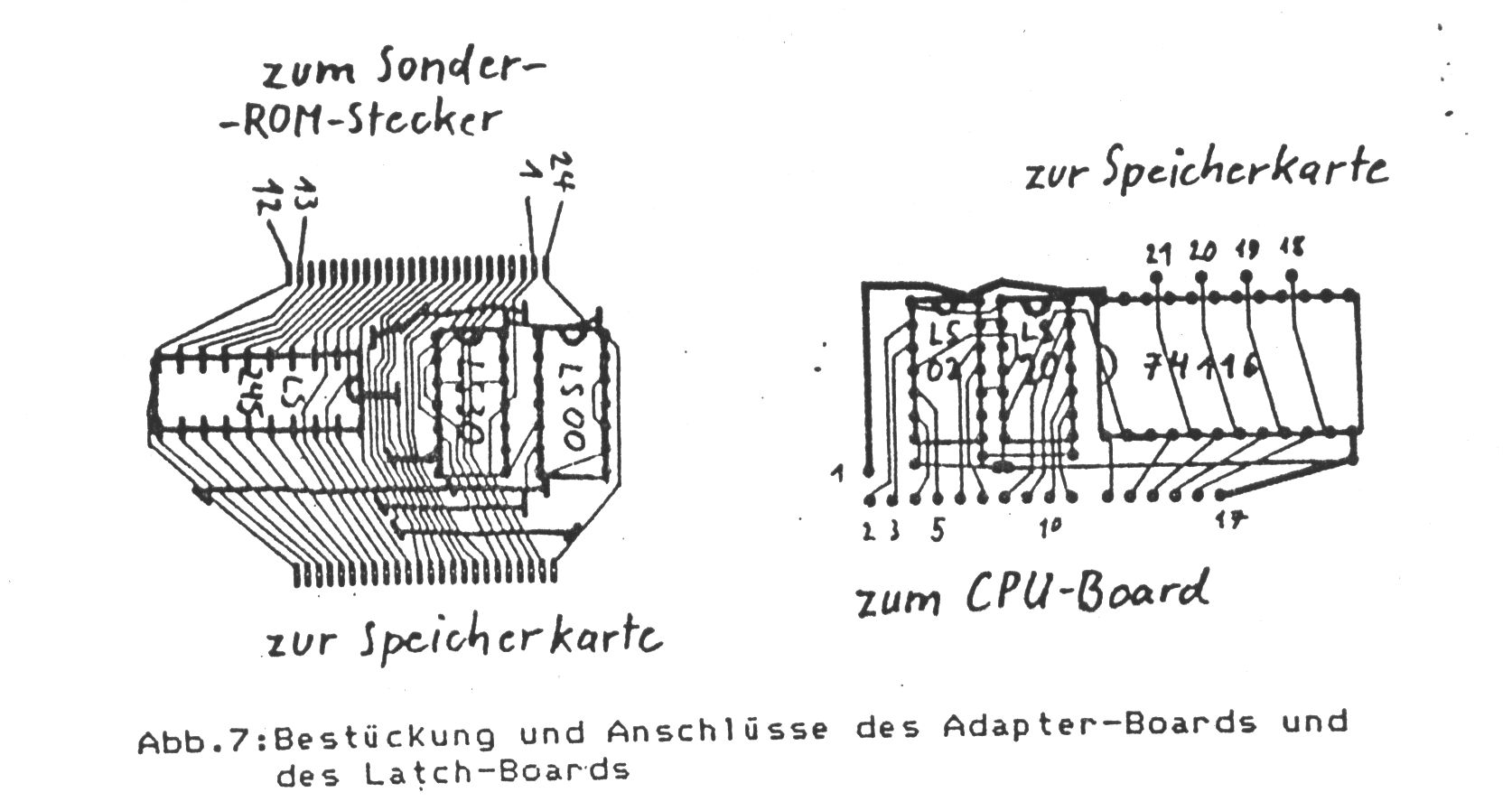

- Fast alle Signale für dieses kleine Board können vom Sockel des Sonder-ROM (nicht von der darüber angeschlossenen Speicherkarte) abgenommen werden:

-

Signal Anschlußpunkt Pin Nr. am Latch-Board Sonder-ROM +5V 1 24 WR* 2 # IORQ* 3 # A0 4 8 A1 5 7 A2 6 6 A3 7 5 A4 8 4 A5 9 3 A6 10 2 A7 11 1 SYSRES* 12 # D0 13 9 D1 14 10 D2 15 11 D3 16 13 GND 17 12 # siehe Text - Die Signale WR* und IORQ* werden an den Pins 11 und 9 von Z16 (74LS367) abgenommen und an die Latch-Board Anschlüsse 2 und 3 gelegt.

- Das Signal SYSRES* für den Anschluß 12 des Latch-Boards muß auf dem CPU-Board noch gebildet werden. Dafür muß in die Position Z26 (neben Z25, 74LS139) noch ein 74LS08 eingesetzt werden. Da diese Position für ein DIL16-IC vorbereitet ist, muß je nach Einbau noch eine Verbindung mit +5V oder GND (am Lötauge außerhalb des ICs hergestellt werden. Selbstverständlich muß das 74LS08 in gleicher Orientierung (Kerbe nach links) wie alle anderen ICs eingebaut werden.

- Nun wird Pin 1 des 74LS86 mit Pin 26 der Z80-CPU und Pin 2 mit Pin 17 der Z80-CPU verbunden. Der Pin 3 des 74LS08 wird an den Anschluß 12 des Latch-Boards geführt.

- Von den Anschlüssen 18 bis 21 des Latch-Boards werden Verbindungen zu den Pins 20 bis 23 des 1-aus-16-Decoders auf der Ver-16-fachungs Karte hergestellt.

-

Latch-Board Ver-16-fachungs Karte Anschluß Signal Pin des 74154 Signal 18 Q3 23 13 19 Q2 22 12 20 Q1 21 11 21 Q0 20 10 - Für eventuelle spätere Service-Arbeiten ist es sinnvoll, wenn einzelne Boards nicht über Drähte direkt miteinander verlötet werden. Deshalb sollten an den vom Layout neben dem Decoder vorgesehenen Stellen Lötnägel eingesetzt werden.