CP/M Hardware für TRS 8O, GENIE und Komtek 1

H. Bernhardt, C. UeberschaarUm den Betrieb unter CP/M zu ermöglichen, sind folgende Anforderungen an die Hardware zu stellen. Nach dem Booten durch die Level II ROMs müssen die ROMs per Software abgeschaltet und durch RAM ersetzt werden können. Der Zugriff auf Bildwiederholspeicher, Tastatur, FDC und Drucker muß auf den oberen Adreßraum (direkt unter FFFFH) verlegt werden. Der gesamte übrige Adressraum muß als RAM zur Verfügung stehen.

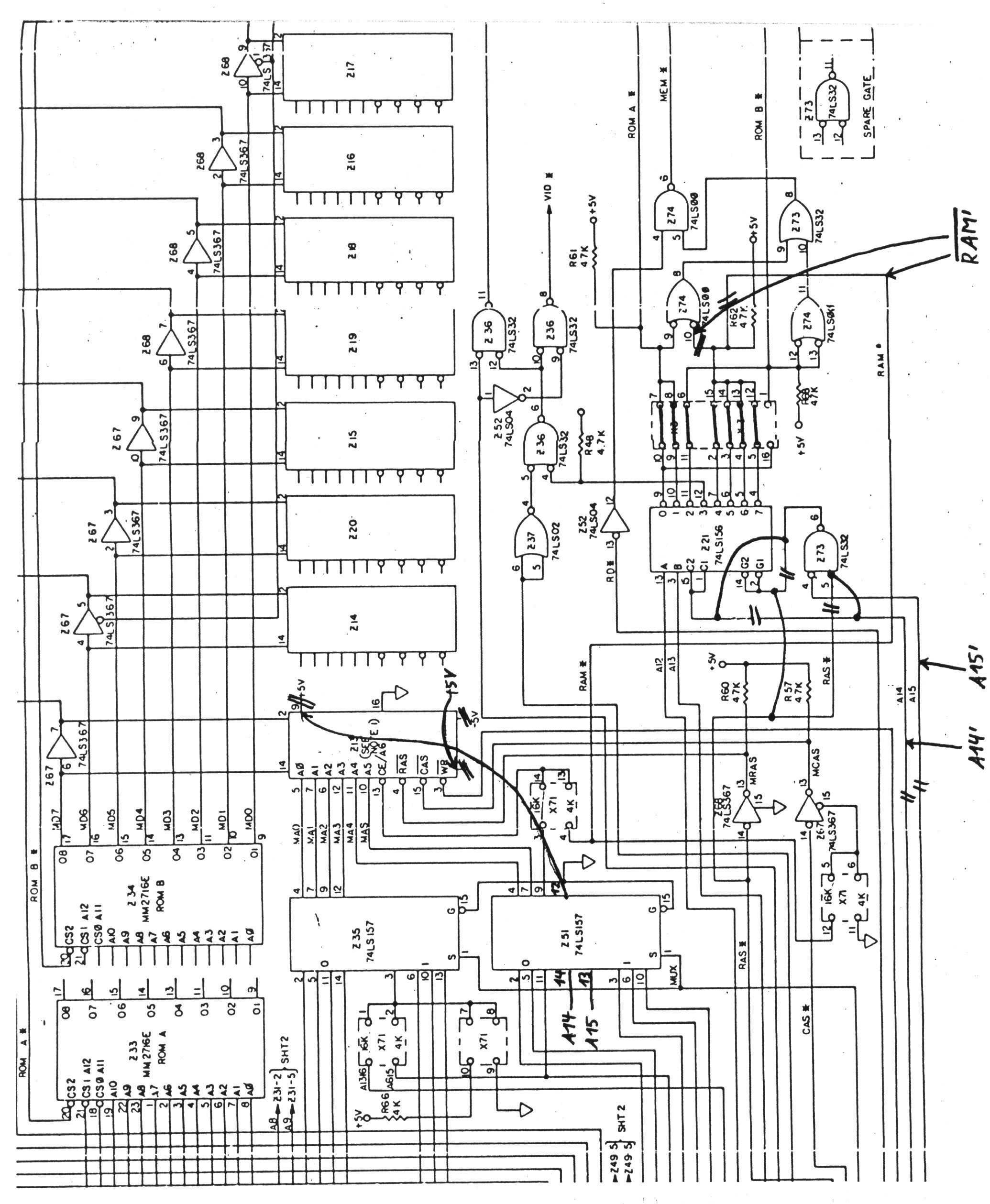

Dieses Problem ist re1ativ einfach zu lösen, vorausgesetzt daß die 4116 RAMs auf dem CPU-Board durch 4164 RAMs ersetzt sind und die dafür nötigen Änderungen vorgenommen wurden (wie dies beim GENIE ab Modell 1983 schon der Fall war oder durch Speichererweiterung auf "64K RAM" für ältere Modelle nachrüstbar war). Um diese Erweiterung auch bei TRS 80 machen zu können, ist zusätzlich auf dem CPU-Board die Änderung gemäß Abb. 7 durchzuführen. Bei allen Geräten müssen die eventuell im Expansion Interface vorhandenen 4116 RAMs entfernt werden.

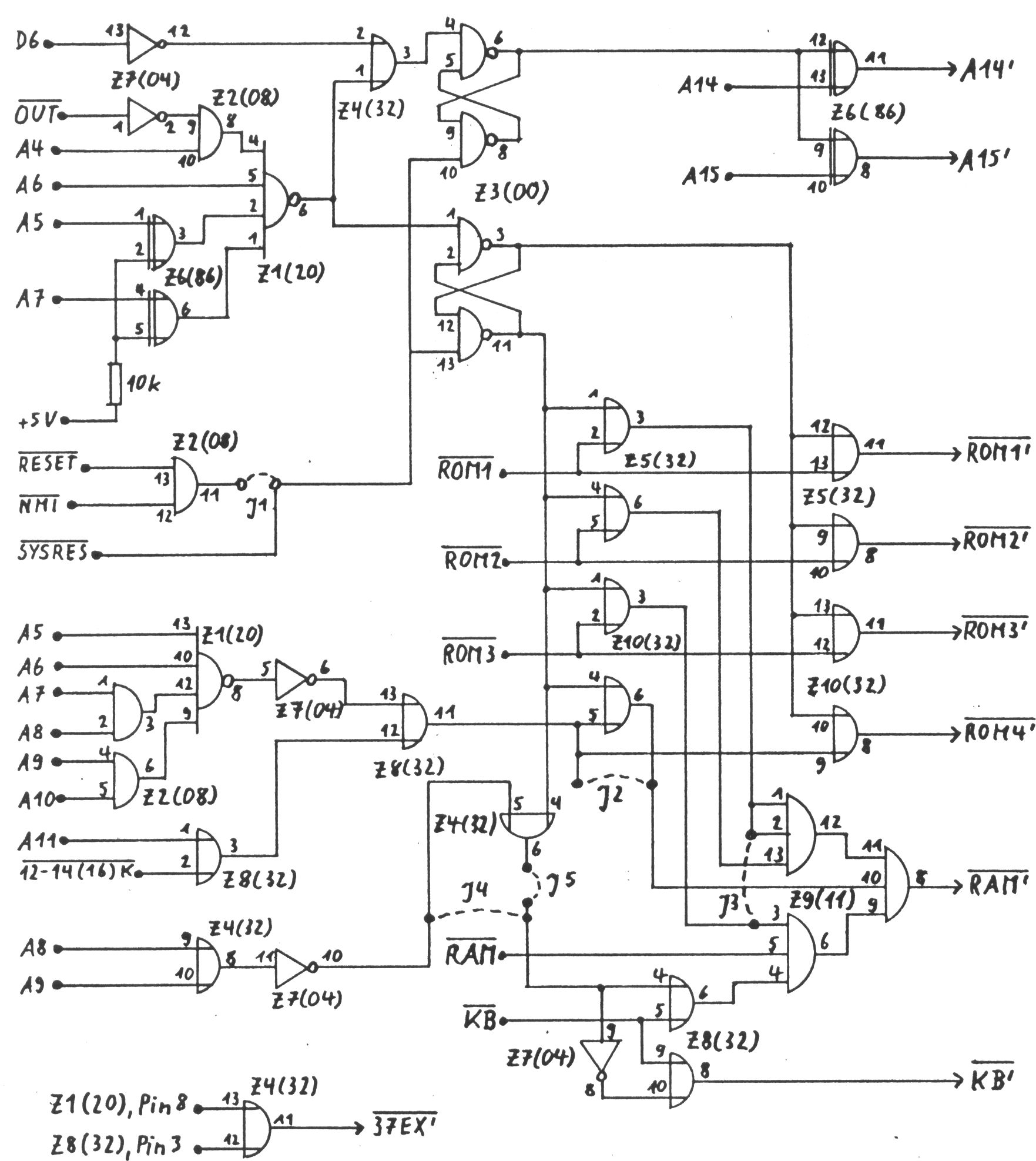

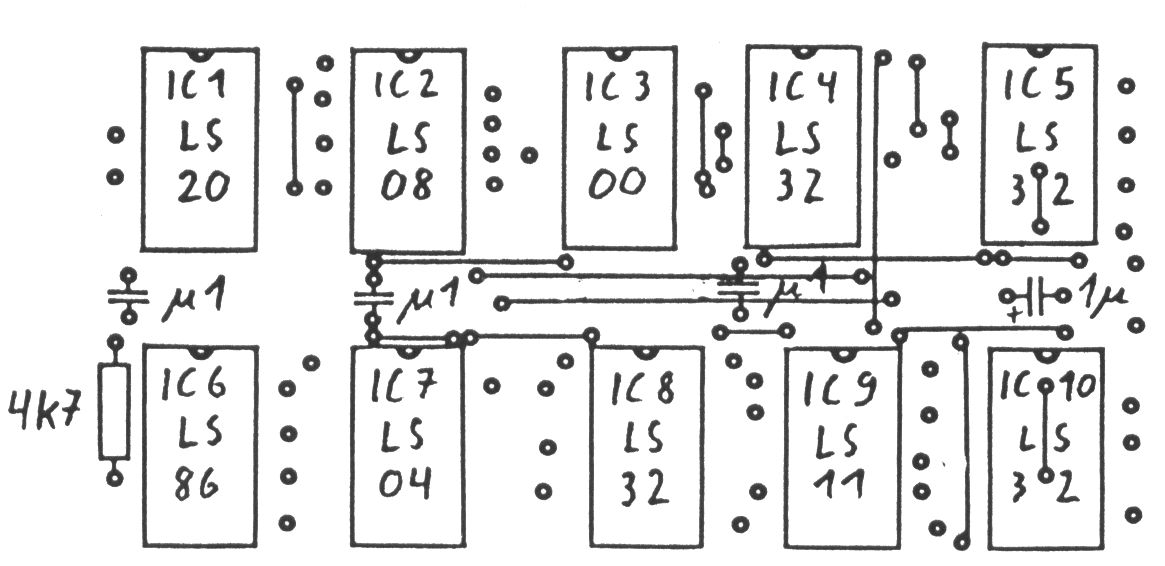

Durch Invertieren der Adressen A14 und A15 für die Decoderschaltung kann erreicht werden, daß ROMs und I/O von 0-16K nach 48-64K verlegt werden. Durch Umschalten der ROM-Freigabesignale an die RAM-Freigabe läßt sich dann zusätzlich noch der Adreßbereich C000H bis F7DFH als RAM gewinnen. Diese Aufgabe übernimmt die in Abb. 1 dargestellte Schaltung.

Abb. 1: Schaltung des CP/M-Boards

Kernstück dieser Schaltung sind zwei aus NAND-Gattern gebildete D Flip Flops, die bei Einschalten (RESET*) oder Drücken der "RESET"-Taste (NMI*) immer so eingestellt werden, daß die ROMs freigegeben werden und zusammen mit dem meomry-mapped I/O im Adressbereich 0-16K* liegen (TRS 80 Modus).

Durch Ausgabe einer Portadresse von 50H bis 5FH wird über die Decoderschaltung (IC1, 74LS20, Pin 6) immer das obere Flip Flop umgekippt, so daß die ROMs abgeschaltet werden und in ihren Adreßbereich dann RAM Speicher vorliegt. Wenn gleichzeitig das Datenbit 0 high ist, wird auch das andere Flipp Flop umgekippt und dadurch per Invertieren von A14 und A15 für die Decoderschaltung des CPU-Boards der I/O-Bereich an das obere Speicherende gelegt.

In dieser für CP/M nötigen Konfiguration liegt außerdem noch der im TRS 80 nicht verfügbare Adreßbereich zwischen ROM und I/O, der im GENIE als Sonder-ROM genutzt wird, als RAM vor. Um beim TRS 80 diesen Bereich (3000H-37DFH) im TRS 80 Modus auch als RAM nutzen zu können, darf IC10 (74LS32) nicht bestückt werden und stattdessen müssen die Jumper J2 und J3 gelegt werden (IC10 kann beim TRS 80 deswegen entfallen, weil nur zwei ROMs vorhanden sind.)

Beim GENIE ist der Bereich 3700H-37DFH (bzw. F700H-F7DFH im CP/M-Modus) wegen der unvollständigen Decodierung der Freigabe der Speicherlesetreiber auf dem CPU-Board nicht verfügbar. Das läßt sich dadurch beheben, daß das Signal 37EXH von Pin 11, IC4 (74LS32) auf dem CP/M-Board an Pin 12 von Z21 (74L20) auf dem CPU-Board angeschlossen wird und die bisher an diesen Pin führende Leitung durchtrennt wird. Durch freie Verdrahtung auf der Lötseite des CP/M-Boards müssen außerdem noch folgende Verbindungen hergestellt werden:

| IC1 (74LS20), Pin 8 | mit | IC4 (74LS32), Pin 13 |

| IC8 (74LS32), Pin 12 | mit | IC4 (74LS32), Pin 12 |

Das dadurch an Pin 11 von IC4 (74LS32) gewonnene Signal 37EX* kann außerdem auch für die Freigabe des 74LS155 Decoders auf dem Expansions Interface benutzt werden, wenn anstelle der beiden Leitungen A14' und A15' nur eine Leitung dorthin geführt werden soll. Der bisherige Anschluß an die Pins 2 und 15 des 74LS155 muß dann natürlich abgetrennt werden.

Die invertierten Adreßleitungen A14' und A15' dürfen dann nicht an das Expansion Interface gelegt werden, wenn dort zuätzliche Hardware Erweiterungen angeschlossen werden, die mit den richtigen Signalen von A14 und A15 versorgt werden müssen.

Im CP/M Modus sind außerdem noch 3/4 des Adreßbereichs von 1K der Tastatur, der im TRS 80 und GENIE durch unvollständige Decodierung verschenkt wird, als RAM verfügbar. Es sind dies die Speicheradressen F900H-FBFFH. Für den TRS 80 Modus wurde die Möglichkeit gelassen, durch die Juper J4 und J5 entweder im Bereich 3900H-3BFFH RAM zur Verfügung zu haben oder die unvollstãndige Tastatur Decodierung beizubehalten. Es ist nicht auszuschließen, daß Programme die Tastatur auch im Bereich 3900 bis 3BFFH auslesen. Beim Komtek 1 ist die Tastatur bereits voll decodiert.

Mit einem Doppelumschalter kann (bei grundsätzlicher Einstellung von Speicher) im Bedarfsfall auf Tastatur von 3800H-3BFFH zurückgeschaltet werden, wenn man sich diese Rückzugsmöglichkeit offen halten möchte.

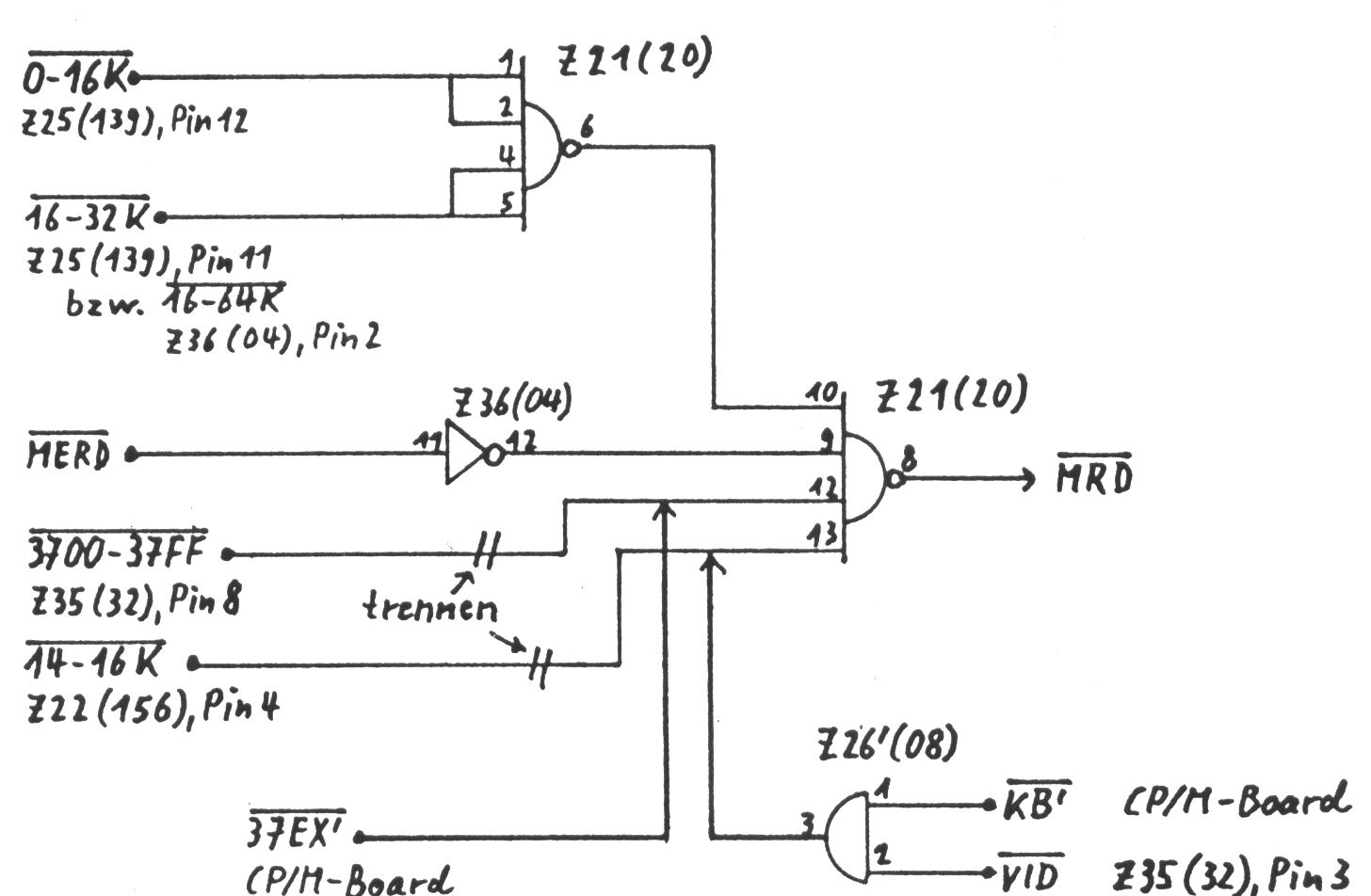

Abb. 2: Freigabesignal des Speicherlesetreibers im GENIE,

Änderungen beim Einbau des CPM-Boards

Abb. 2: Freigabesignal des Speicherlesetreibers im GENIE,

Änderungen beim Einbau des CPM-BoardsUm beim GENIE diesen Speicherbereich nutzen zu können muß durch AND-Verknüpfung der Signale KB'* des CP/M-Boards und VID*, Pin 3 von Z35 (74LS32) auf dem CPU-Board und Anlegen des dadurch gebildeten Signals an Pin 13 von Z21 (74LS20) auf dem CPU-Board (Abb.2) der Speicherlesetreiber freigegeben werden. Das dafür nötige IC 74LS08 kann auf den freien Platz neben Z25 (74LS139) eingesetzt werden.

Im TRS 80-Modus ist durch die getrennte Umschaltung der Flip Flops auch noch die Möglichkeit gegeben die ROMs abzuschalten und durch RAMs zu überblenden. Das läßt sich dazu nutzen, um den ROM-Inhalt durch ein kleines Maschinenprogramm zunächst in den oberen Speicherbereich zu kopieren, dann durch Ausgabe von 00H an eine der Portadressen 50H-5FH von ROM auf RAM umzuschalten und den ROM-Inhalt dann wieder in seinen ursprünglichen Bereich zurückzuschreiben. Der dann unter gleichen Adressen im RAM vorliegende ROM-Inhalt kann dann beliebig geändert werden. Um Schwachstellen der ROM-Treiberroutinen (z.B. Unterdrücken bestimmter Steuercodes für die Druckerausgabe) zu umgehen, können dann diese Routinen direkt gepatched werden und müssen nicht durch zusätzliche Maschinenprogramme im oberen Speicherbereich ersetzt werden.

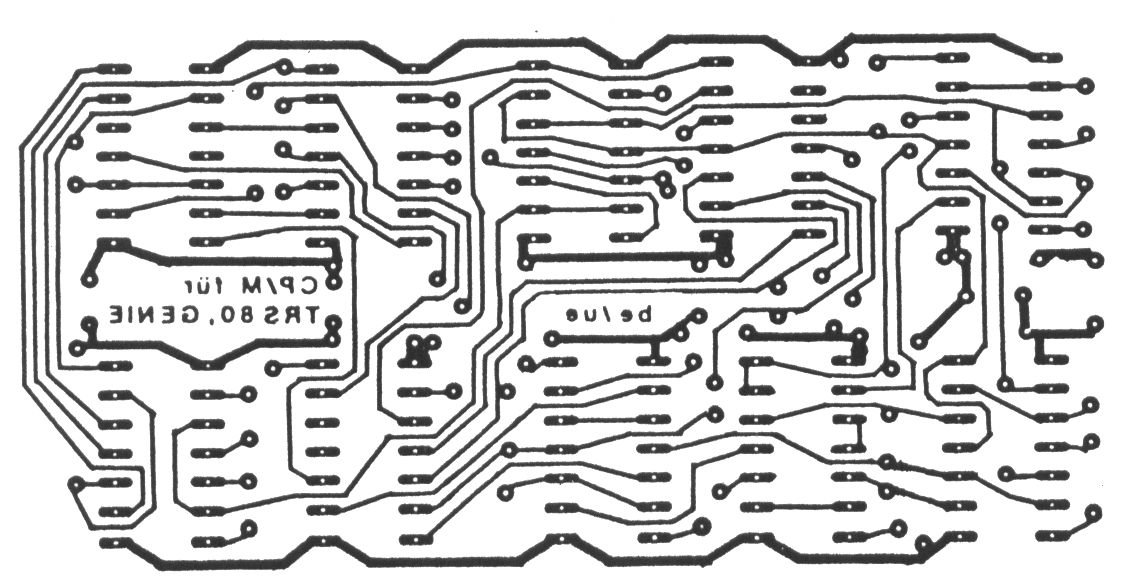

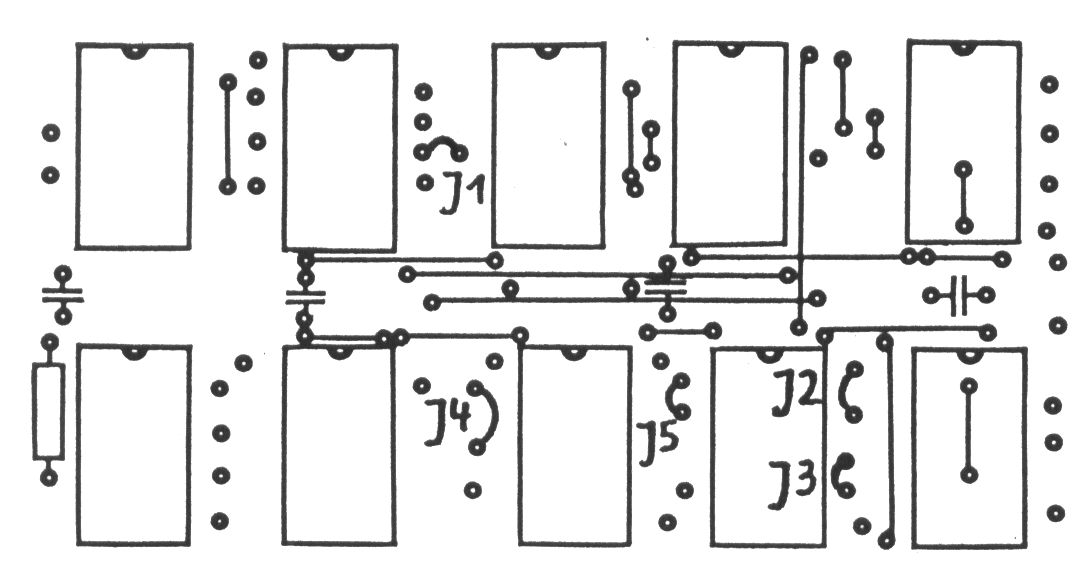

Abb. 3: Layout, Ansicht Bestückungsseite

|

Abb. 4: Bestückung, Drahtbrücken

|

Das in Abb.3 vorgeschlagene Layout sowie der Bestückungsplan und die externe Beschaltung (Abb.4 und 6) bauen auf eine leicht selbst herzustellende einseitig gedruckte Schaltung mit relativ wenigen Drahtbrücken auf. Der Jumper J1 zwischen IC2 und IC3 ist nur bei Anschluß an den GENIE zu setzen wo anstelle des nicht vorhandenen SYSRES* Signals die Signale RESET* und NMI* herangezogen werden müssen.

Funktion der Jumper| TRS 80 | GENIE und Komtek 1 | |

| J1 |

bleibt offen, wenn SYSRES* benutzt wird und nicht RESET* und NMI* |

muß gelegt werden, weil SYSRES* nicht verfügbar ist |

| J2, J3 |

müssen gelegt werden, IC 10 darf nicht bestückt werden |

bleiben offen, IC 10 muß bestückt werden |

| J4, J5 | gilt für alle Geräte | |

| J4 gelegt und J5 offen: 3900H-3BFFH ist auch im TRS 80 Modus als RAM verfügbar | ||

| J4 offen und J5 gelegt: Im TRS 80-Modus belegt die Tastatur den Bereich 3800H-3BFFH (außer bei Komtek 1) | ||

| Mit einem Doppel Umschalter anstelle einer festen Einstellung mit Jumpern kann zwischen beiden Varianten umgeschaltet werden | ||

Abb. 6: Anschluß an das CPU-Board

| Signal auf dem | TRS 80 | GENIE | Komtek 1 | #4 | ||||||||

| CP/M-Board | IC | Typ | Pin | IC | Typ | Pin | IC | Typ | Pin | |||

| A4 | Z39 | 367 | 7 | Z4 | 367 | 9 | 42 | 2732 | 4 | |||

| A5 | " | " | 9 | " | " | 7 | " | " | 3 | |||

| A6 | " | " | 5 | " | " | 11 | " | " | 2 | |||

| A7 | " | " | 11 | " | " | 5 | " | " | 1 | |||

| A8 | " | " | 3 | " | " | 13 | " | " | 23 | |||

| A9 | " | " | 13 | " | " | 3 | " | " | 22 | |||

| A10 | Z38 | " | 3 | Z6 | " | 3 | " | " | 19 | |||

| A11 | " | " | 13 | " | " | 13 | " | " | 21 | |||

| A14 | " | " | 11 | " | " | 7 | 33 | Z80 | 4 | |||

| A15 | " | " | 9 | " | " | 9 | " | " | 5 | |||

| A14' | Z73 | 32 | 5 | #3 | Z25 | 139 | 14 | #1 | 53 | 139 | 2 | #1 |

| A15' | " | " | 4 | #1 | " | " | 13 | #1 | " | " | 3 | #1 |

| D6 | Z75 | 367 | 9 | Z18 | 367 | 13 | 42 | 2732 | 16 | |||

| 12-14(16)K* | Z21 | 156 | 12 | Z22 | 156 | 5 | 49 | 139 | 1 | |||

| OUT* | Z23 | 32 | 3 | Z15 | 32 | 8 | 38 | 32 | 6 | |||

| SYSRES* | Z37 | 02 | 1 | -------------------- | -------------------- | |||||||

| RESET* | -------------------- | Z2 | 05 | 6 | 33 | Z80 | 26 | |||||

| NMI* | -------------------- | " | " | 8 | " | " | 17 | |||||

| ROM1* | Z21 | 156 | 9 | Z22 | 156 | 9,10 | #1 | 48 | 32 | 11 | ||

| ROM2* | " | " | 11 | " | " | 11,12 | #1 | " | " | 3 | ||

| ROM3* | -------------------- | " | " | 6,7 | #1 | " | " | 6 | ||||

| ROM1'* | Z33 | ROMA | 20 | #1 | Z10 | 3001 | 20,21 | #1 | 42 | 2732 | 18 | #1 |

| ROM2'* | Z34 | ROMB | 20 | #1 | Z11 | 3002 | 20,21 | #1 | 47 | " | " | #1 |

| ROM3'* | -------------------- | Z12 | 3003 | 20,21 | #1 | 52 | " | " | #1 | |||

| ROM4'* | -------------------- | Z13 | 2716 | 18 | #2 | 57 | " | " | #1 | |||

| RAM* | Z21 | 156 | 5 | #3 | Z36 | 04 | 2 | #1 | (siehe Text) | |||

| RAM'* | Z37 | 367 | 15 | #1 | Z37 | 367 | 15 | #1 | 54 | 32 | 1 | #1 | Z74 | 00 | 10 | #1 | 59 | 245 | 19 | #1 |

| KB* | Z36 | 32 | 11 | #1 | Z35 | 32 | 11 | #1 | 49 | 139 | 6 | |

| KB'* | Z3 | 368 | 1 | Z8 | 368 | 1 | -------------------- | |||||

Anschluß des CP/M-Boards an das Expansion Interface

| Signal | TRS 80 | GENIE | EXP1 von RB Eletronik |

| Exp.Intfc. Kabel | Exp.Intfc. Kabel | keine | |

| A14' | Leitung 10 #1 | Leitung 23 #1 | Änderung |

| A15' | Leitung 7#1 | Leitung 21 #1 | nötig |

| oder stattdessen: | |||

| 37EX' | Z39(74LS155)2,14 #1 | Z29(74LS155)2,14 #1 | Z18(74LS155)2,14 #1 |

#1 bisherige Leitungen abtrennen

#2 beide Leitungen abtrennen und miteinander verbinden, ohne daß Pin 38 mit daran liegt

#3 die bei der Erweiterung auf 64K mit 4164 ICs gelegte Verbindung muß wieder entfernt werden

#4 die Nummerierung der ICs des CPU-Boards erfolgt gemȧß dem Bestückungsplan aus; Info des TRS 80 / GENIE User Club, Hardware Sonderheft; 'Wie aus dem Komtek 1 ein Computer wird

Herleitung eines richtigen Freigabesignals für GENIE und Komtek 1

Das zur RAM-Freigabe beim Umrüsten auf 64K RAM auf dem CPU-Board in den mitgelieferten Anleitungen vorgeschlagene invertierte Signal 0-16K kann bei bestimmten I/0-Befehlen eventuell Schwierigeiten machen. Deshalb sei hier eine Möglicheit beschrieben, wie mit nicht benutzten Gattern auf dem CPM-Board dieser Fehler behoben werden kann.

1) GENIE- Das Signal 12-16K* wird nicht an Pin 2 sondern an Pin 12 von IC 8 (LS32) gelegt.

- Die Verbindung zwischen Pins 3 und 12 von IC 8 (LS32) wird durchtrennt.

- Das Signal 0-16K* (CPU-Board, Z25, LS139, Pin 12) wird n Pin 3 von IC 7 (LS04) gelegt.

- Pin 4 von IC 7 (LS04) wird mit Pin 2 von IC 8 (LS32) verbunden.

- Anstelle von A11 wird MERQ* (CPU-Board, Z25, LS139 Pin 15) an Pin 1 von IC 8 (LS32) angeschlossen.

- Pin 3 von IC 8 (LS32) wird mit Pin 5 von IC 9 (LS11) verbunden (das bisherige Signal RAM* vom CPU-Board wird abgetrennt).

- Die Verbindung zwischen Pins 5 und 9 von IC 8 (LS32) wird durchtrennt.

- Die Leiterbahn zu Pin 9 von IC 7 (LS04) wird durchtrennt.

- Das SignaJ 0-16*K (CPU-Board, Z53, LS139 Pin 4) wird an Pin 9 von IC 7 (LS04) gelegt.

- Das Signal MERQ* (CPU-Board, Z53, LS139 Pin 1) wird an Pin 9 von IC 8 (LS32) angesch1ossen.

- Pin 8 von IC 8 (LS32) wird it Pin 5 van IC 9 (LS11) verbunden (das Signal KB' ist auf dem CPU-Board nicht nötig, da die Tastatur voll decodiert ist).

- Die Pins 1, 8, und 9 aller RAM5 (Z14 - Z20) gemeinsam von den Versorgungsspannungen +12V, -5V und +5V abtrennen

- +5V an die Pins 8 aller RAMs legen

- Alle Kondensatoren die an einer der die Pins 1 oder die Pins 9 verbindenden Leitungen liegen, auslȯten

- A14 (Z38, 74LS367, Pin 11) an Pin 14 von Z51, 74LS157 legen

- A15 (Z38, 74LS367, Pin 9) an Pin 13 von Z51, 74LS157 legen

- Pin 12 von Z51, 74LS157 mit den Pins 9 der RAMs verbinden

- Die Leiterbahn von/zu folgenden Pins durchtrennen

Z21, 74LS155, Pins 2 und 14 sowie 1 und 15

Z73, 74LS32, Pin 5 - folgende Pins miteinander verbinden

Pin 5 von Z73, 74LS32 mit Pin 11 von Z38, 74LS367: A15

Pin 6 von Z73, 74LS32 mit Pins 1 und 15 von Z21, 74LS156: 0-16K*

Pin 14 von Z68, 74LS367 mit Pins 2 und 14 von Z21, 74LS156: RAS* - Im Jumperfeld X3 müssen folgende Positionen miteinander verbunden sein, 2-15, 3-14, 4-13, 5-12, 6-11, 7-10, 8-9

- Im Jumperfeld X71 müssen nur die Brücken 1-16, 3-14 und 5-12 gesetzt sein

- Im TRS 80 Expansion Interface muß die Verbindung zwischen Pin 6 von Z28, 74LS00 und Pin 19 von Z31, 74LS244 durchtrennt werden.