# CS82310 CHIPSet

PEAK/DM

Data Book

February 1991

RELIMINARY

#### Copyright Notice

Software Copyright © 1991, CHIPS and Technologies, Inc.

Manual Copyright € 1991, CHIPS and Technologies, Inc.

All Rights Reserved.

Printed in U.S.A.

#### Trademarks

PEAKTM, PEAK/DMTM and PEAK/SXTM are trademarks of CHIPS and Technologies, Incorporated.

IBM®, IBM PC®, and IBM PC/AT® are registered trademarks of International Business Machines Corporation.

PS2<sup>TM</sup>, Microchannel<sup>TM</sup>, and Personal System/2<sup>TM</sup> are trademarks of International Business Machines Corporation.

Intel® is a registered trademark of Intel Corporation.

386DX<sup>TM</sup> and 387DX<sup>TM</sup> are trademarks of Intel Corporation.

Lotus® is a registered trademark of Lotus Development Corporation.

MS-DOS® is a registered trademark of Microsoft Corporation. Motorola® is a registered trademark of Motorola.

#### Discisimer

This manual is copyrighted by CHIPS and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of CHIPS and Technologies, Inc.

Every possible effort was made to ensure the accuracy of this manual. However, CHIPS Systems Logic Division cannot accept responsibility for any errors in the manual or consequences resulting therefrom.

The information contained in this document is being issued in advance of the production cycle for the device(s). The parameters for the device(s) may change before final production.

CHIPS and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or change.

The information contained in this manual is provided for general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of CHIPS and Technologies, Luc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

#### Restricted Rights and Limitations

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at 252.277-7013.

CHIPS and Technologies, Inc. 3050 Zanker Road San Jose, California 95134 Phone: 408-434-0600

# Contents

### Volume I: PEAK/DM Overview

|         | •                                                                           |          |  |

|---------|-----------------------------------------------------------------------------|----------|--|

| Section | n 1: Introduction                                                           | .1       |  |

| 1.1     | Features                                                                    | . 1      |  |

| 1.2     | 82C351 CPU/Cache/DRAM Controller                                            | . 2      |  |

| 1.3     | 82C355 Data Buffer                                                          | . 2      |  |

| 1.4     | 82C356 Peripheral Controller                                                | . 2      |  |

| Section | n 2: Manual Conventions                                                     | .5       |  |

| 2.1     | What You Need to Know                                                       | . 5      |  |

| 2.2     | About This Manual                                                           | . 5      |  |

| 2.3     | Typographical Conventions                                                   | . 6      |  |

| Volun   | Volume II: 82C351 CPU/Cache/DRAM Controller                                 |          |  |

| Sectio  | n 1: 351 Functional Description                                             | .9       |  |

| 1.1     | Features                                                                    | . 9      |  |

| 1.2     | Functional Subsystem                                                        |          |  |

| 1.3     | Clock Logic                                                                 | 12       |  |

| 1.4     | Action Code Generation and Data Conversion Logic                            | 14       |  |

| 1.5     | CPU, Local Memory, AT Bus Control and<br>Arbitration Logic                  | 14       |  |

| 1.6     | CPU Control Logic  Local Memory Control  AT Bus Control  Bus Arbitration    | 16<br>16 |  |

| 1.7     | Bus Timeout Logic                                                           | 18       |  |

| 1.8     | Memory Control Logic  First Megabyte of Memory  Cache Access  Refresh Cycle | 20<br>21 |  |

| 1.9    | EPROM Control Logic                                  | . 22       |

|--------|------------------------------------------------------|------------|

|        | Shadow RAM                                           |            |

|        | OS/2 Optimization                                    |            |

|        | Coprocessor Handling                                 | 24<br>25   |

|        | Logic Equations                                      | . 27       |

| 1.10   | Cache Concepis                                       |            |

| 2.20   | Cache Size                                           |            |

|        | Cache Organization                                   | 28         |

|        | Direct-mapped Cache                                  | . 28       |

|        | Cache Updating                                       | 29<br>20   |

|        |                                                      |            |

| 1.11   | Cache Functional Overview                            |            |

|        | Tag RAM Testing                                      | 31         |

|        | Cache Data RAM Testing                               | 32         |

|        | Physical Address Field Assignment                    | 32         |

| 1.12   | Cache Operation                                      | 33         |

|        | Read Hit Operation                                   | 33         |

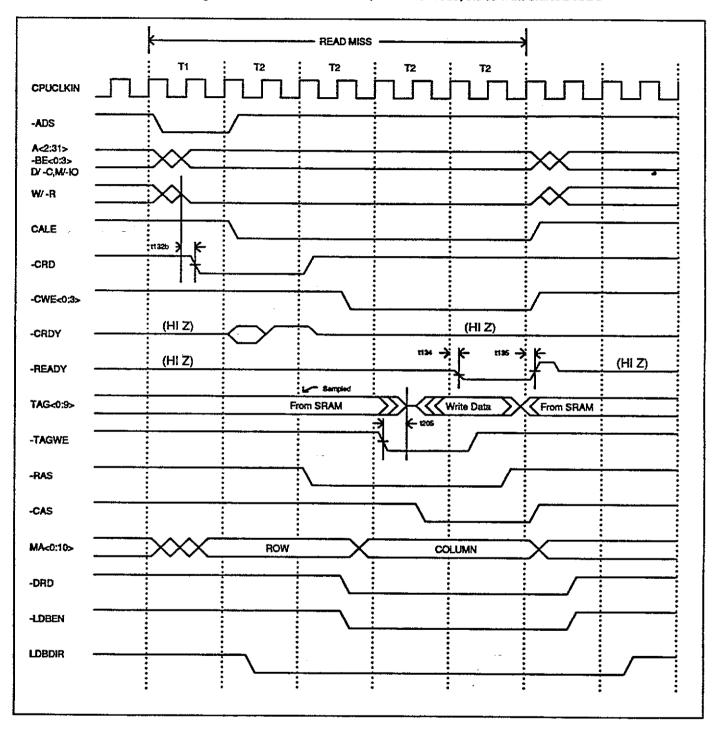

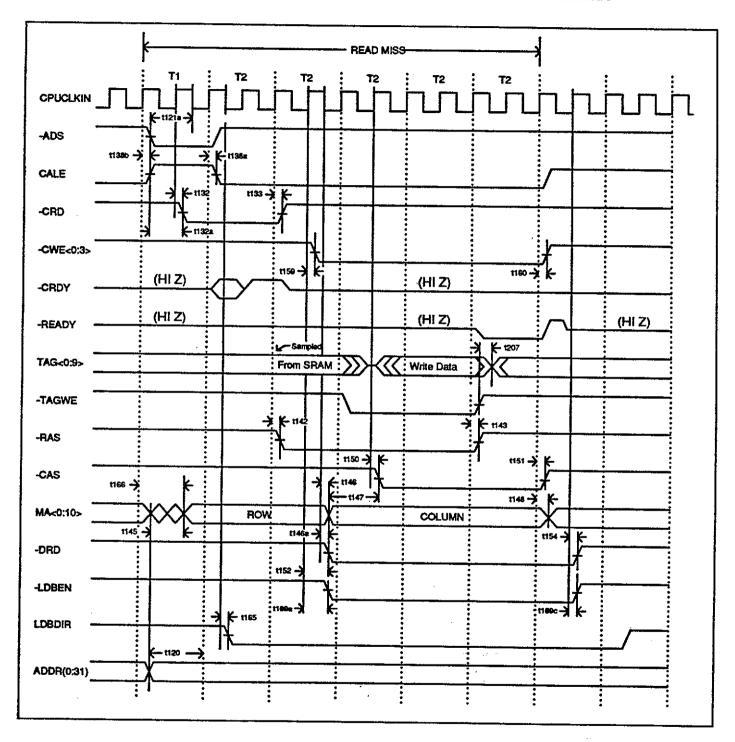

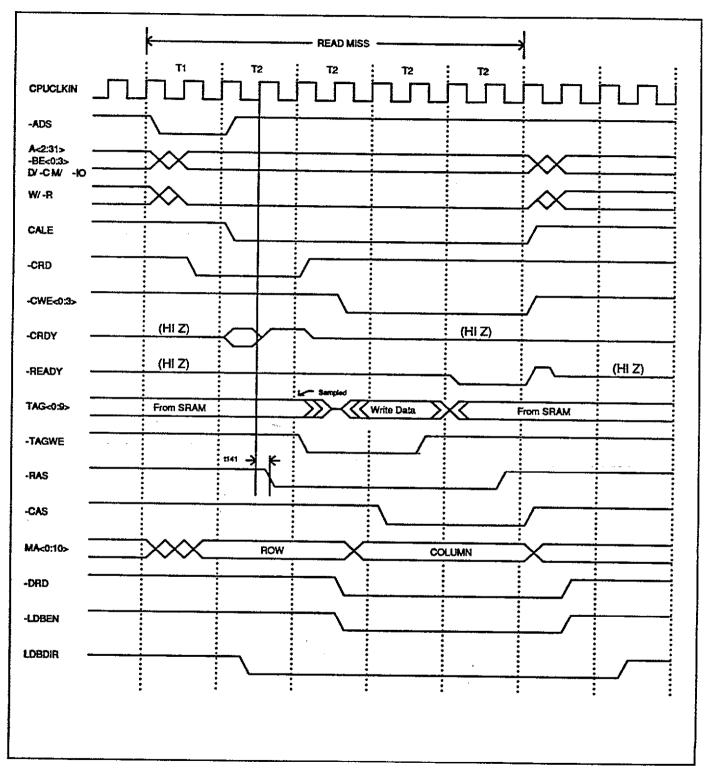

|        | Read Miss Operation                                  | 34         |

|        | Write Hit Operation                                  |            |

| 1.13   | DMA Operation                                        |            |

|        | Non-Cacheable Regions                                |            |

| 1.14   | Index Registers                                      | 36         |

| Contin | on 2. 251 Configuration Desistant                    | 27         |

|        | on 2: 351 Configuration Registers                    |            |

| 2.1    | Index Registers                                      |            |

| 2.2    | I/O Port Registers                                   | 37         |

| Contin | on 2. 251 Din Decementions                           | £1         |

| 3.1    | on 3: 351 Pin Descriptions                           |            |

|        |                                                      |            |

| 3.2    | Numerical Listing of Pin Assignments                 |            |

| 3.3    | Alphabetical Listing of Pin Assignments              | 59         |

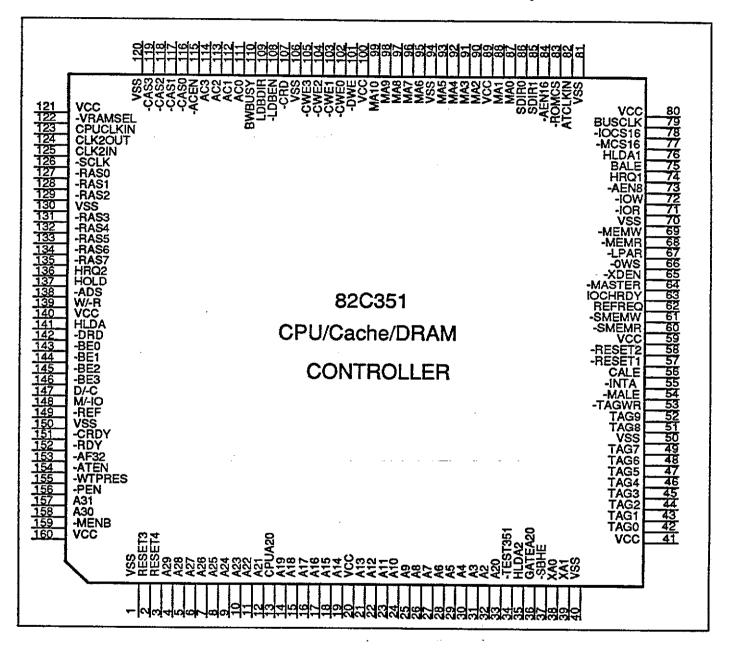

| 3.4    | Pin Diagram                                          | 60         |

|        |                                                      |            |

|        | on 4: 351 Physical Characteristics                   |            |

| 4.1    | Absolute Maximum Ratings                             |            |

| 4.2    | Operating Conditions                                 | 61         |

| Carti  | on 5: DC/AC Characteristics                          | <i>L</i> 2 |

| 5.1    | 351 DC Characteristics                               |            |

|        |                                                      |            |

| 5.2    | 351 AC Characteristics                               | 64         |

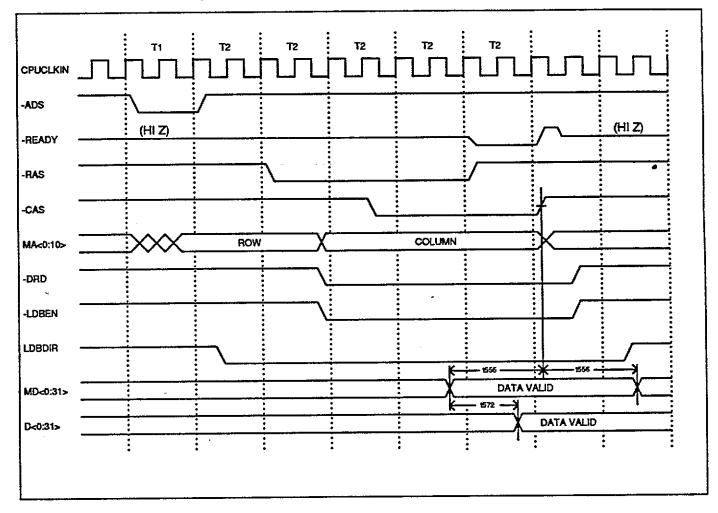

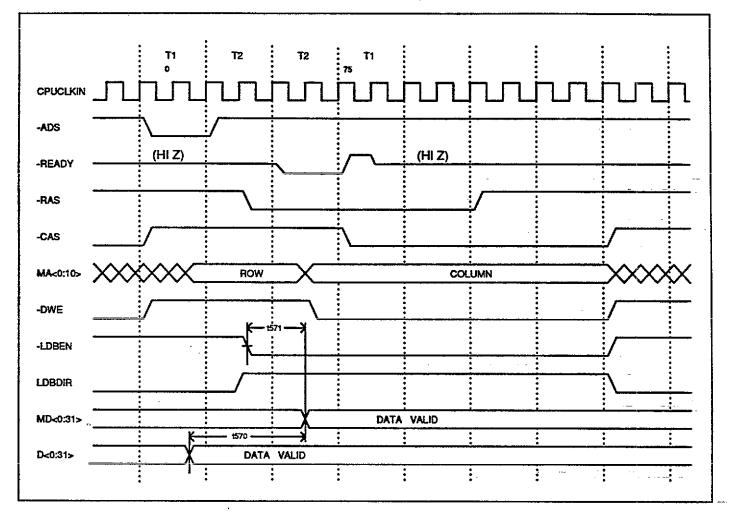

| Sootie | on 6: 351 Timing Diagrams                            | 75         |

| 260.00 | ## \$16 .3.21   P#####   ########################### |            |

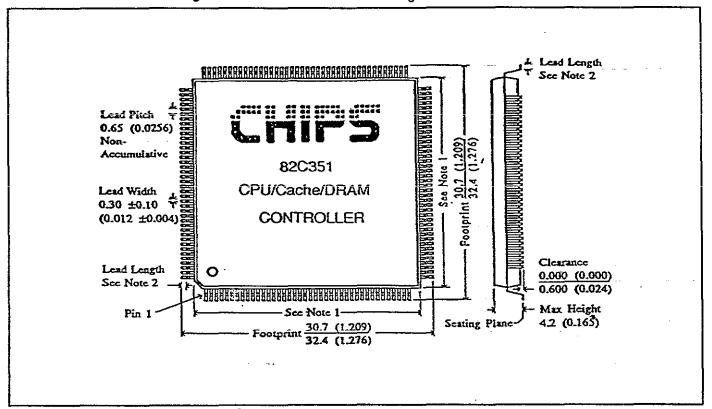

| Section 7: 351 Physical Dimensions95    |                                                 |  |

|-----------------------------------------|-------------------------------------------------|--|

| 7.1                                     | 82C351 CPU/Cache/DRAM Controller95              |  |

| Volur                                   | ne III: 82C355 Data Buffer                      |  |

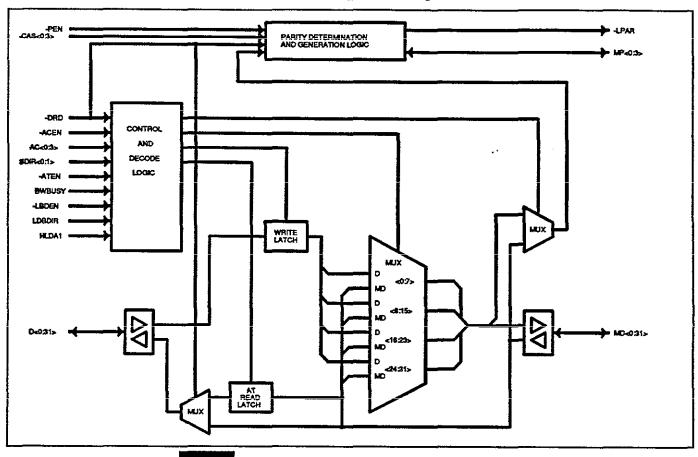

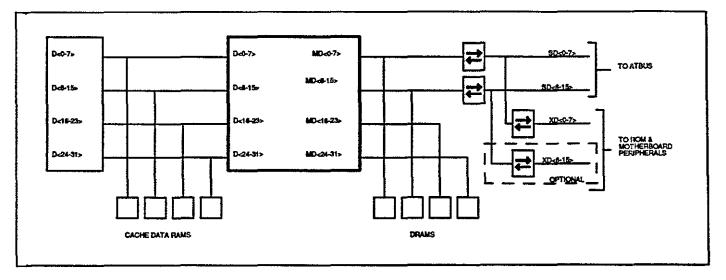

| Sectio                                  | n 1: 355 Functional Description                 |  |

| 1.1                                     | Features                                        |  |

| 1.2                                     | Functional Subsystem97                          |  |

| 1.3                                     | Bus Interface                                   |  |

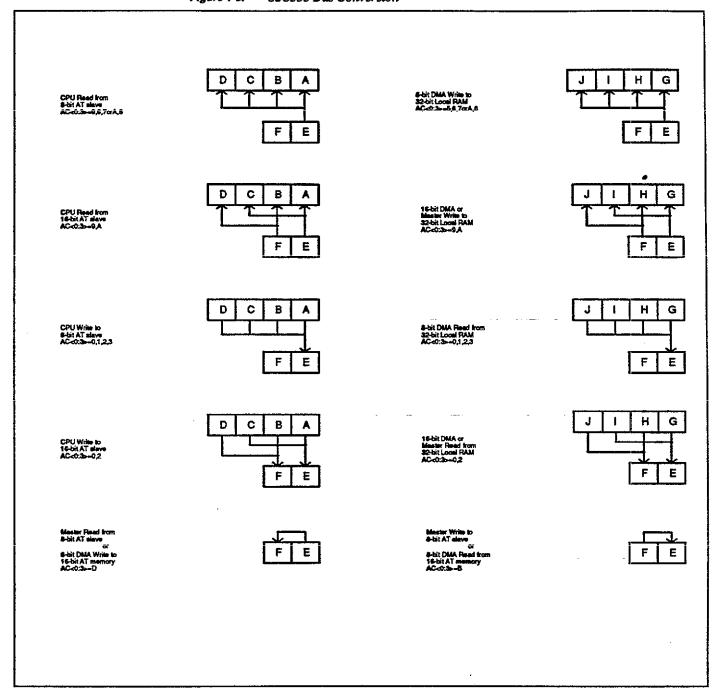

| 1.4                                     | Data Conversion                                 |  |

| 1.5                                     | Parity                                          |  |

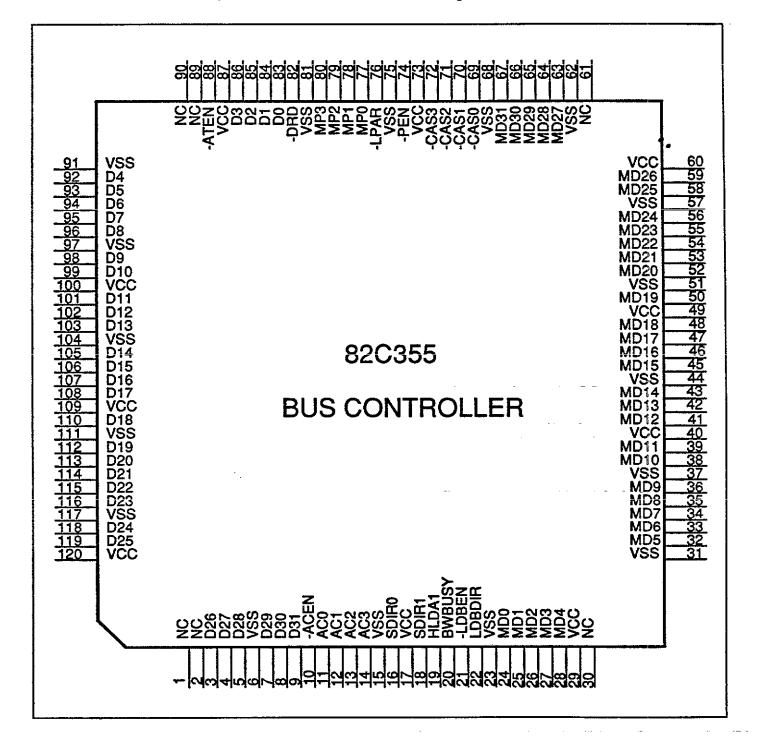

| Sectio                                  | n 2: 355 Pin Description                        |  |

| 2.1                                     | Pin Assignments                                 |  |

| 2.2                                     | Numerical Listing of Pin Assignments            |  |

| 2.3                                     | Alphabetical Listing of Pin Assignments         |  |

| 2.4                                     | Pin Diagram                                     |  |

| Sectio                                  | n 3: 355 Physical Characteristics109            |  |

| 3.1                                     | Absolute Maximum Ratings                        |  |

| 3.2                                     | Operating Conditions                            |  |

| Sectio                                  | n 4: 355 DC/AC Characteristics111               |  |

| 4.1                                     | DC Characteristics                              |  |

| 4.2                                     | AC Characteristics                              |  |

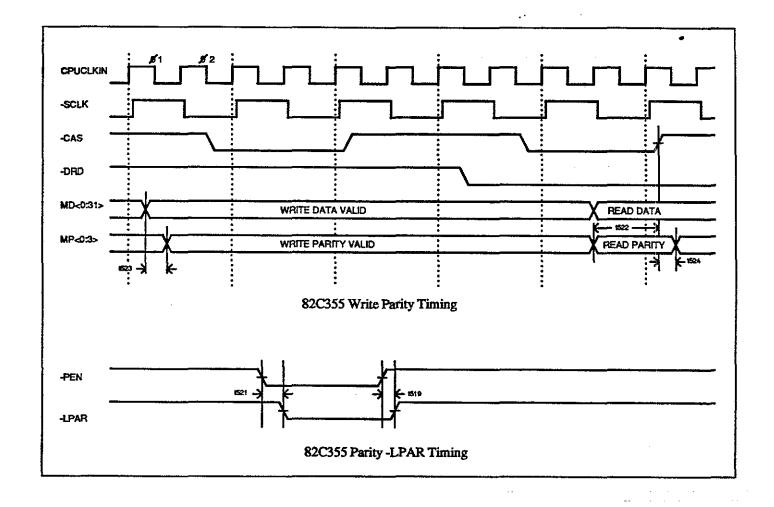

| Sectio                                  | n 5: 355 Timing Diagrams113                     |  |

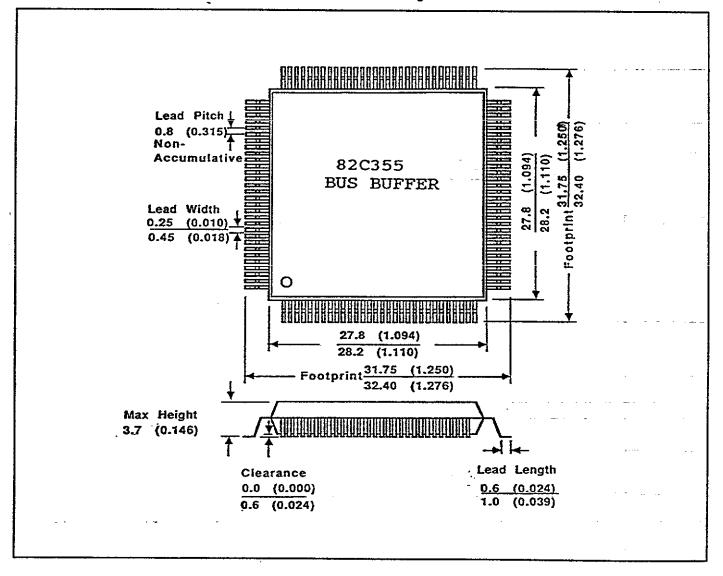

| Sectio                                  | n 6: 355 Physical Dimensions                    |  |

| 6.1                                     | 82C355 Data Buffer                              |  |

| Volume IV: 82C356 Peripheral Controller |                                                 |  |

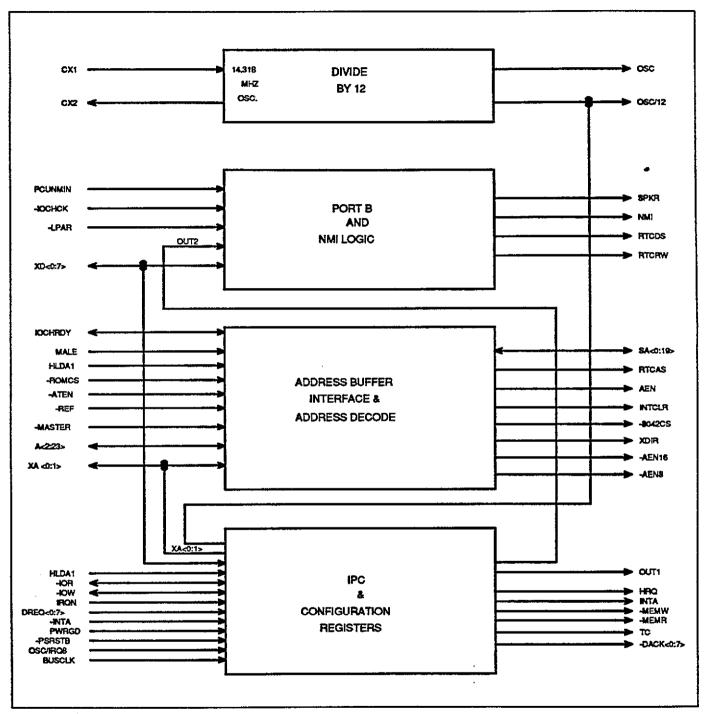

| Sectio                                  | n 1: 356 Functional Description                 |  |

| 1.1                                     | Features                                        |  |

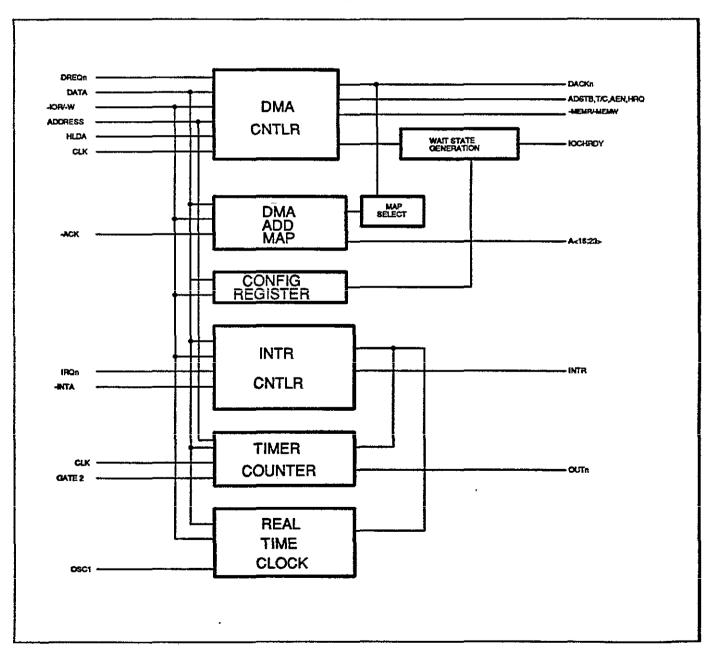

| 1.2                                     | Functional Subsystem                            |  |

|                                         | Address Bus Interface Between A and SA Buses119 |  |

| 1.3                                     | Address Decode                                  |  |

| 1.4                                     | Port B and NMI logic                            |  |

| 1.5  | Integrated Peripheral Controller                                                                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.6  | Multilevel Decode Subsystem                                                                                                                                                                                                                                                                                                      |

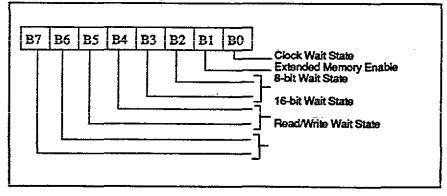

| 1.7  | Clock and Wait State Control                                                                                                                                                                                                                                                                                                     |

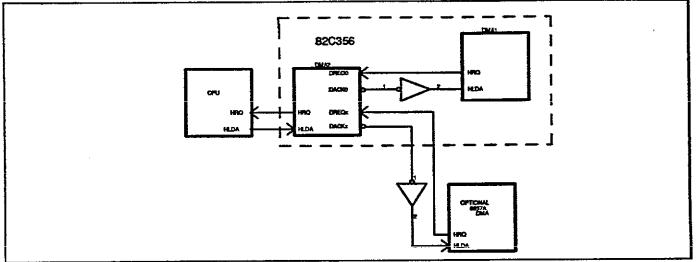

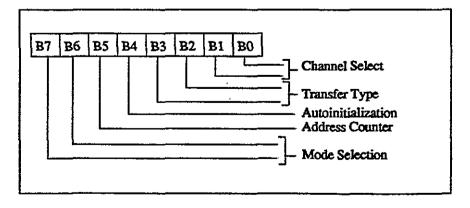

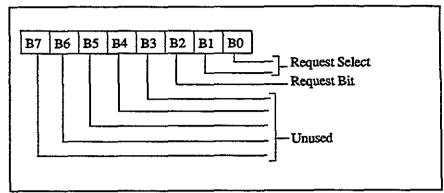

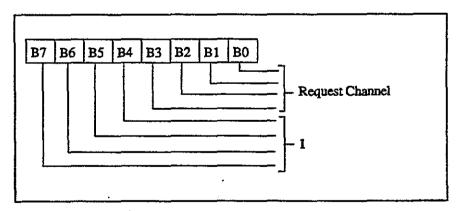

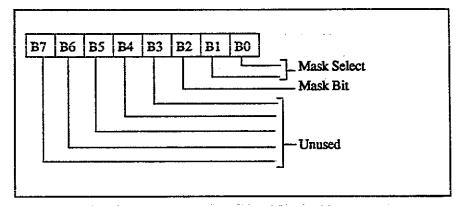

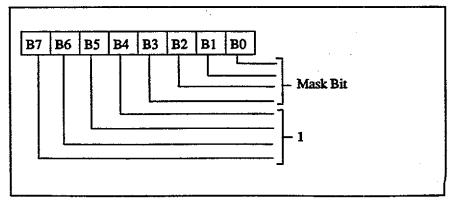

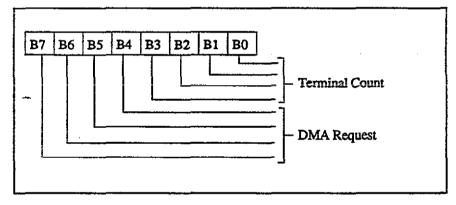

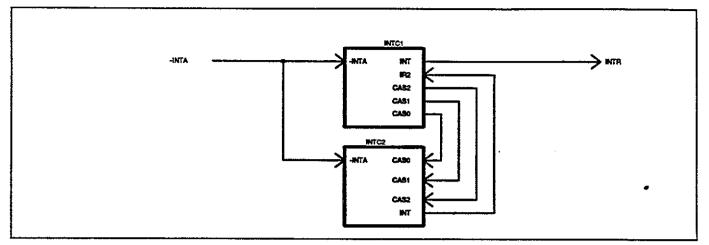

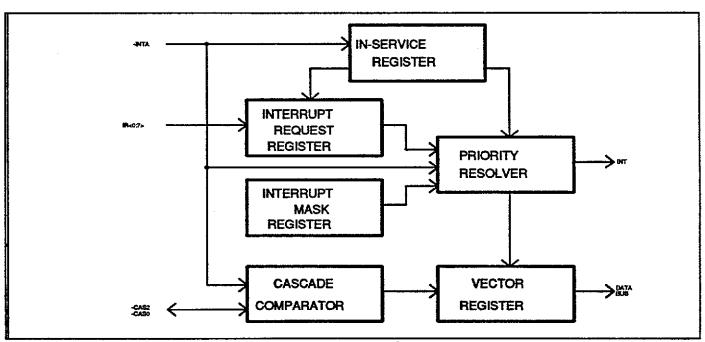

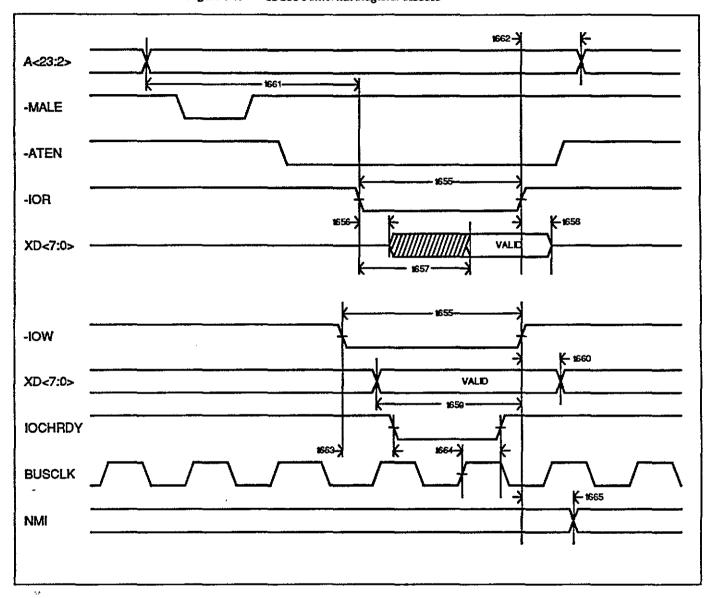

| 1.8  | DMA Functional Description       126         DMA Operations       126         Idle Condition       127         Program Condition       128         Active Condition       128         Single Transfer Mode       128         Block Transfer Mode       129         Demand Transfer Mode       129         Cascade Mode       129 |

| 1.9  | DMA Transfers                                                                                                                                                                                                                                                                                                                    |

| 1.10 | Autoinitialization                                                                                                                                                                                                                                                                                                               |

| 1.11 | DREQ Priority                                                                                                                                                                                                                                                                                                                    |

| 1.12 | Address Generation                                                                                                                                                                                                                                                                                                               |

| 1.13 | Compressed Timing                                                                                                                                                                                                                                                                                                                |

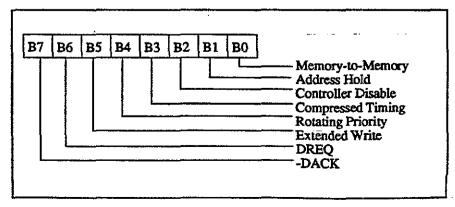

| 1.14 | Register Descriptions       133         Mode Register       134         Request Register       135         Request Mask Register       137         Status Register       138         Temporary Register       138                                                                                                                |

| 1.15 | Special Commands                                                                                                                                                                                                                                                                                                                 |

| 1.16 | Controller Operation                                                                                                                                                                                                                                                                                                             |

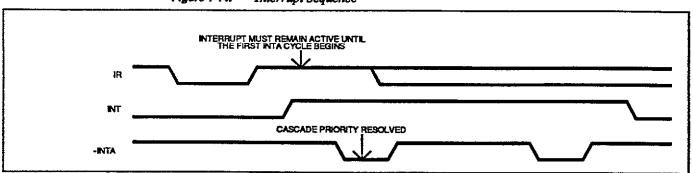

| 1.17 | Interrupt Sequence                                                                                                                                                                                                                                                                                                               |

| 1.18 | End of Interrupt                                                                                                                                                                                                                                                                                                                 |

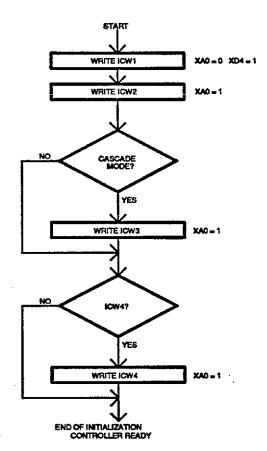

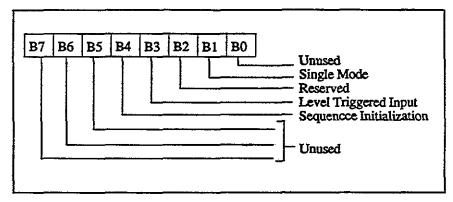

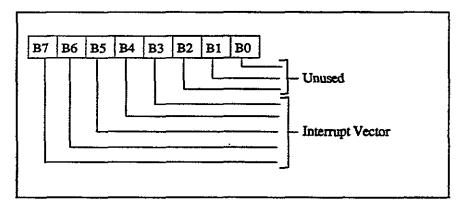

| 1.19 | Programming the Interrupt Controller                                                                                                                                                                                                                                                                                             |

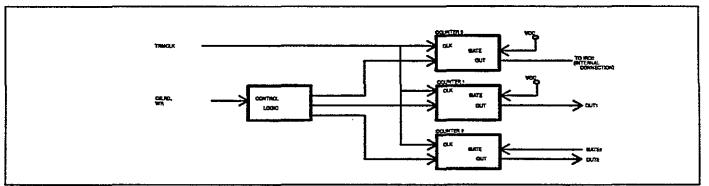

| 1.20 | Counter/Timer Functional Description                                                                                                                                                                                                                                                                                             |

| 1.21 | Counter Description                                                                                                                                                                                                                                                                                                              |

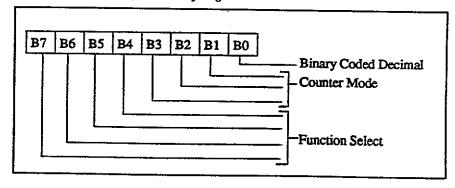

| 1.22 | Programming the CTC                                                                                                                                                                                                                                                                                                              |

| 1.23 | Real Time Clock Functional Description                                                                                                                                                                                                                                                                                           |

|      | Static RAM                              | 160         |

|------|-----------------------------------------|-------------|

|      | Control and Status Registers            |             |

|      | Update Cycle                            |             |

|      | Power-Up/Down                           | 165         |

| Sect | ion 2: 356 Configuration Registers      | 167         |

| 2,1  | Index Registers                         | 167         |

| 2.2  | I/O Port Registers                      |             |

| 2.3  | I/O Map                                 | *********   |

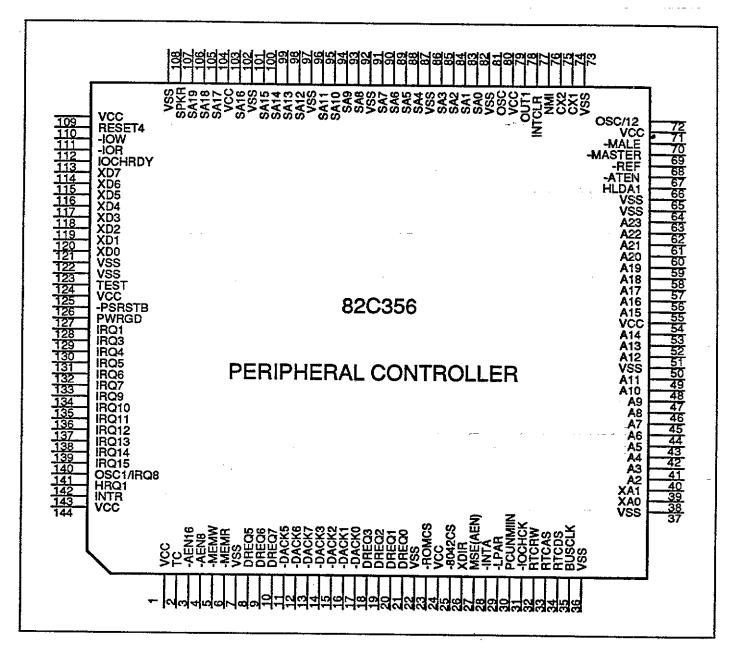

| Sect | ion 3: 356 Pin Descriptions             | 193         |

| 3.1  | Pin Assignments                         |             |

| 3.2  | Numerical Listing of Pin Assignments    | 199         |

| 3.3  | Alphabetical Listing of Pin Assignments | 200         |

| 3.4  | Pin Diagram                             | 201         |

| Sect | ion 4: 356 Physical Characteristics     | 203         |

| 4.1  | Absolute Maximum Ratings                |             |

| 4.2  | Operating Conditions                    |             |

| Sect | ion 5: 356 DC/AC Characteristics        |             |

| 5.1  | DC Characteristics                      | <b>2</b> 05 |

| 5.2  | AC Characteristics                      | 206         |

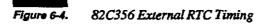

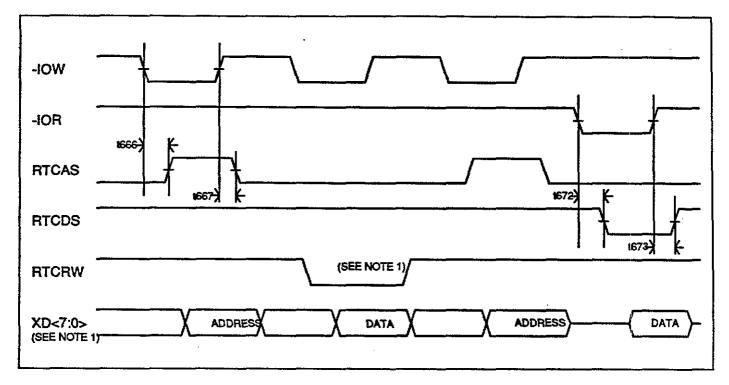

| Sect | ion 6: 356 Timing Diagrams              | 209         |

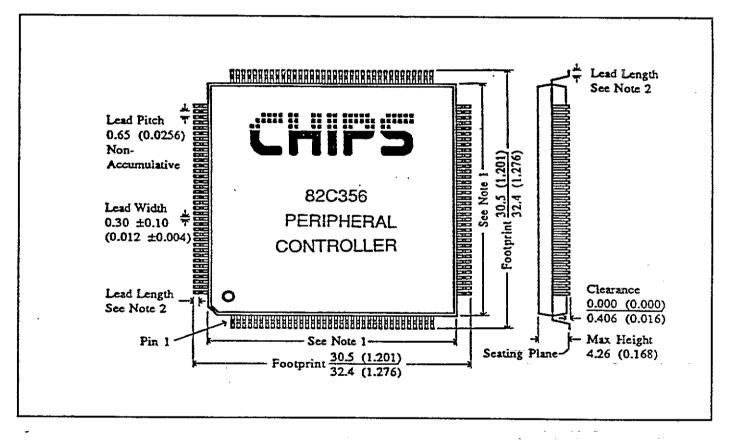

| Sect | ion 7: 356 Physical Dimensions          | 215         |

| 7.1  | 82C356 Peripheral Controller            | 215         |

# List of Figures

| Volume I: PEAK/DM Overview |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Section 1:                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

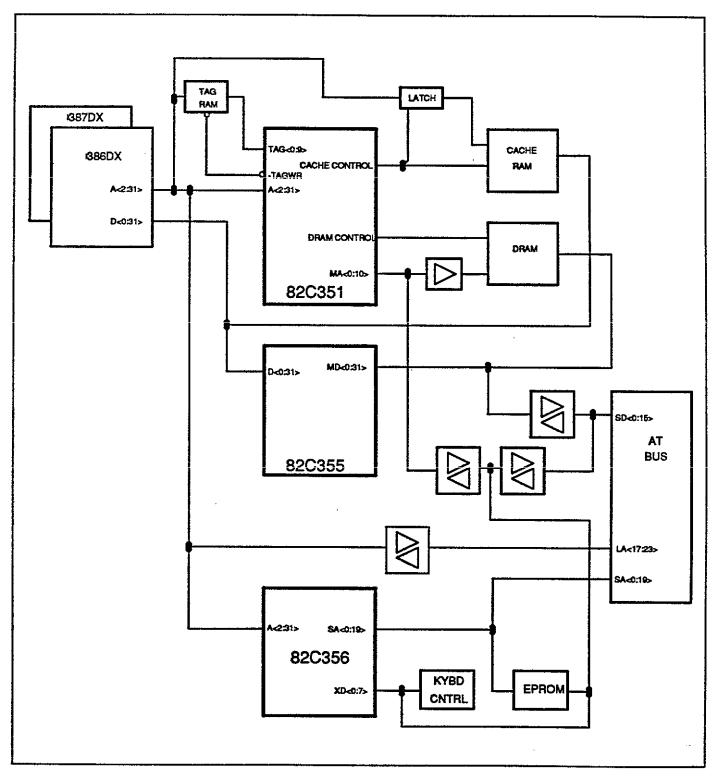

| Figure 1-1                 | PEAK/DM System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Volume II:                 | 82C351 CPU/Cache/DRAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Section 1:                 | 351 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

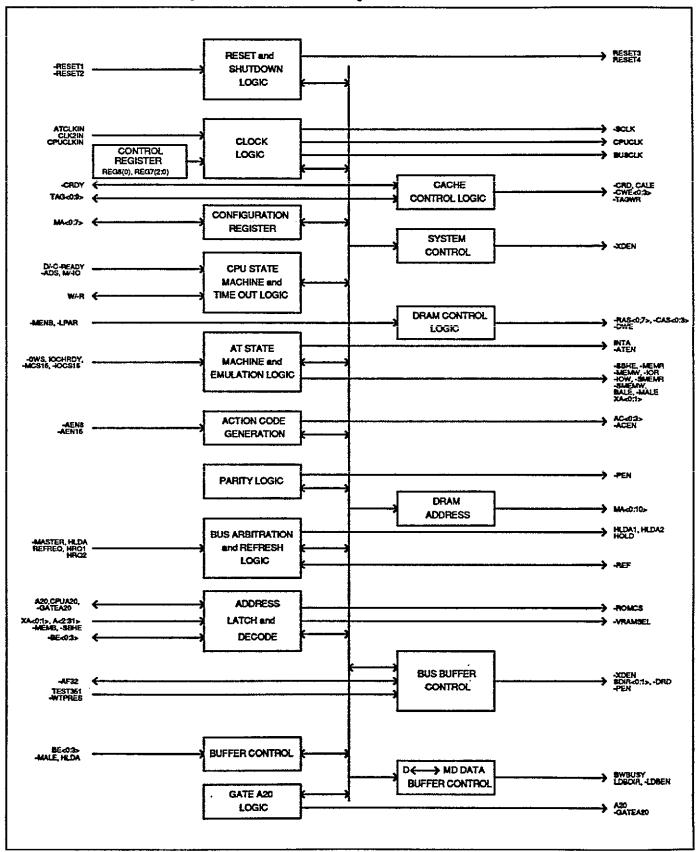

| Figure 1-1                 | 82C351 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

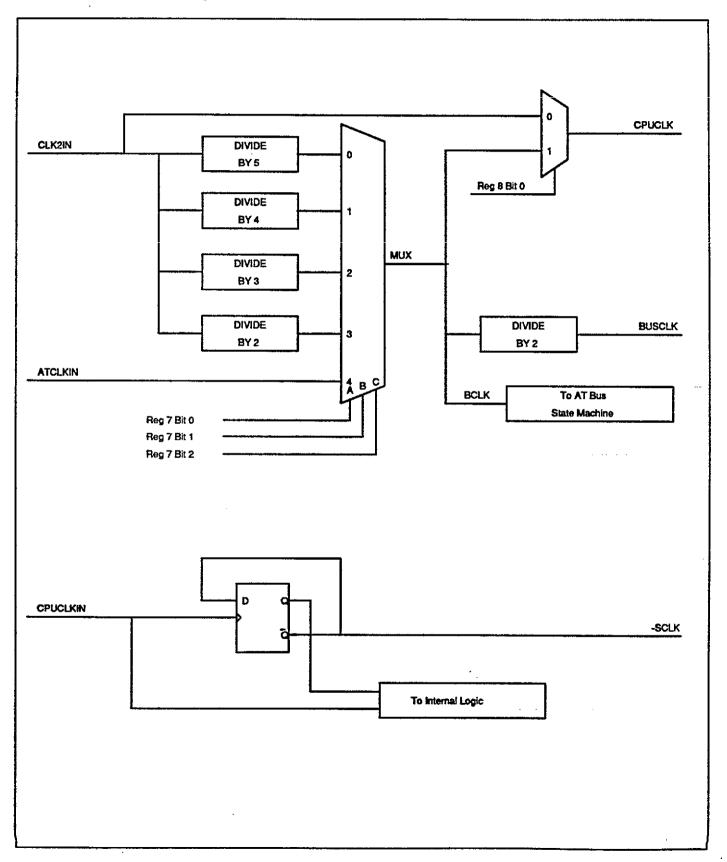

| Figure 1-2                 | 82C351 Clock Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

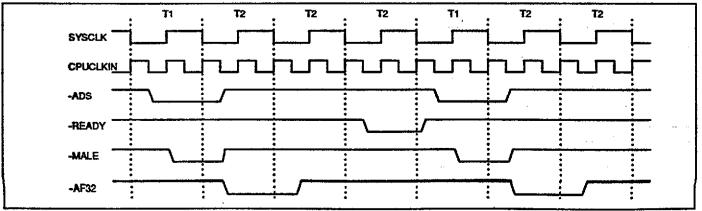

| Figure 1-3                 | -MALE and -AF32 Generation for Local                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| _                          | Bus Cycles (2 WS Cycle)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

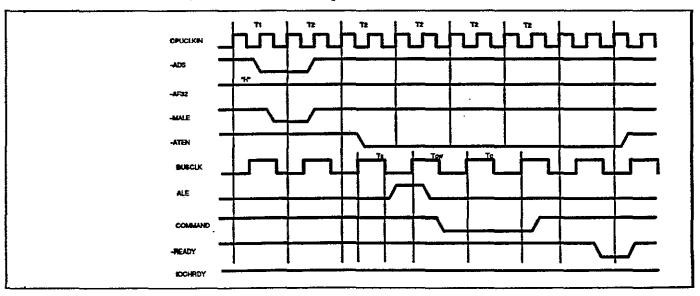

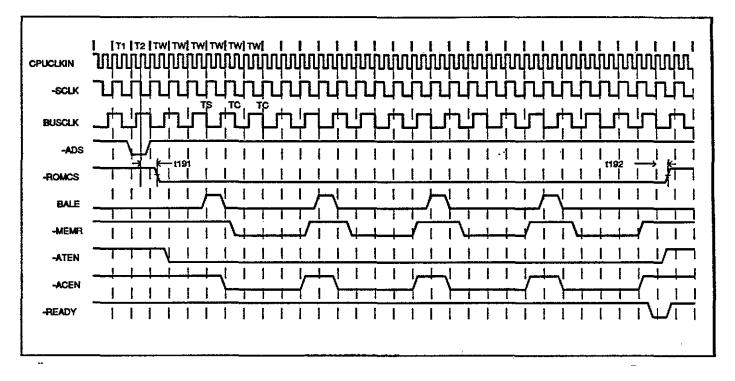

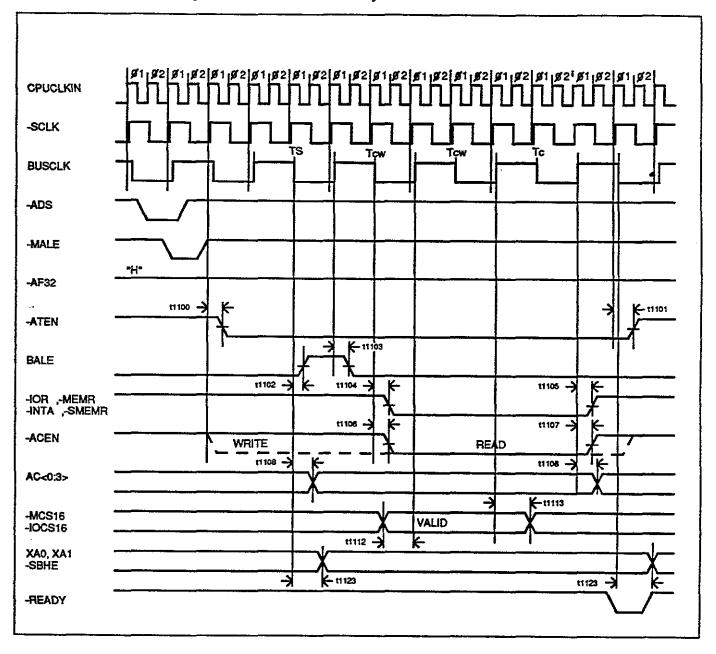

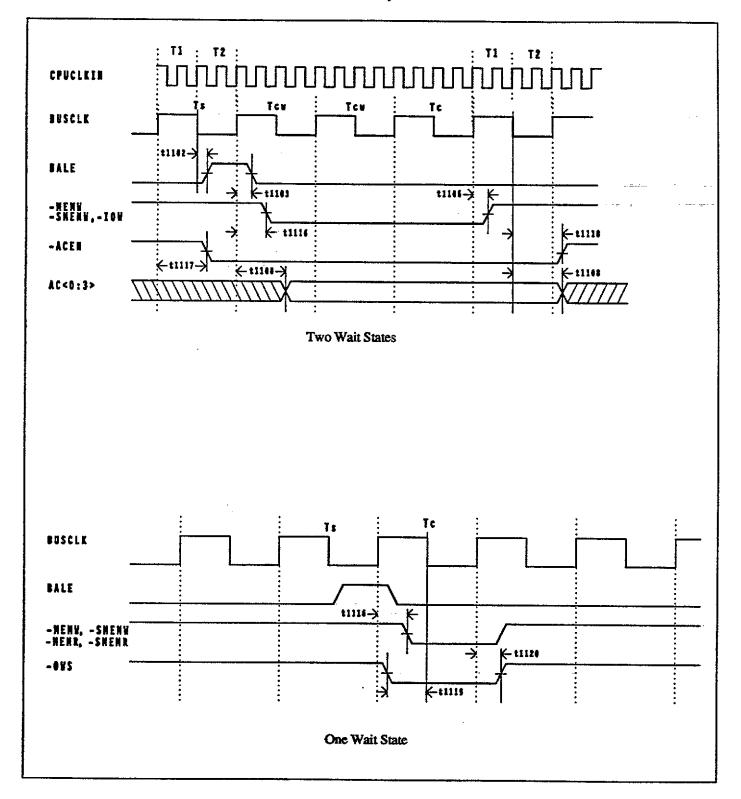

| Figure 1-4                 | AT Bus Timing - One Wait State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

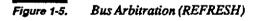

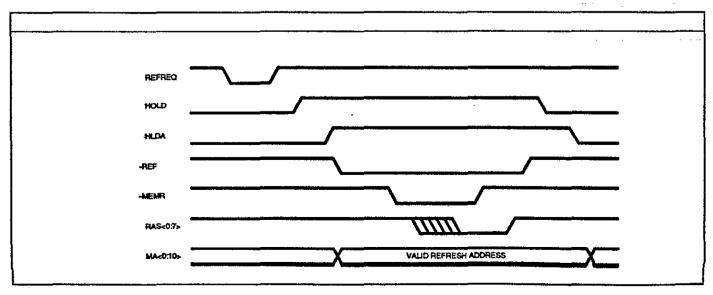

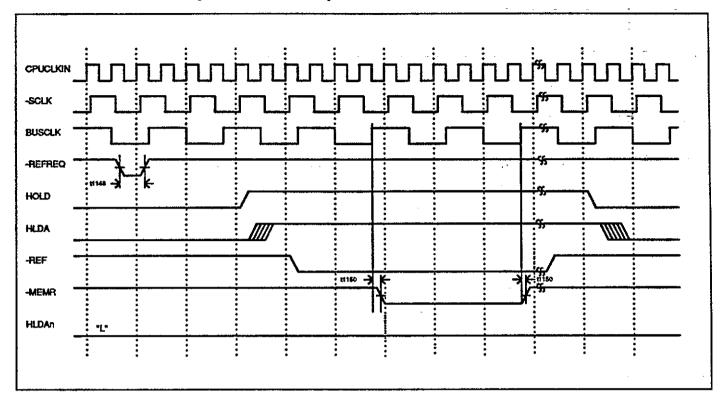

| Figure 1-5                 | Bus Arbitration (REFRESH)1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

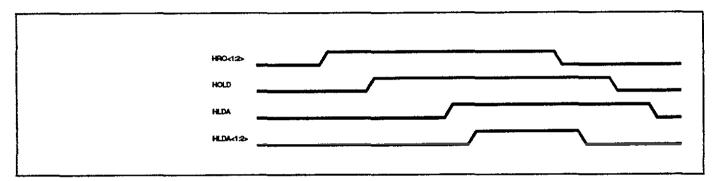

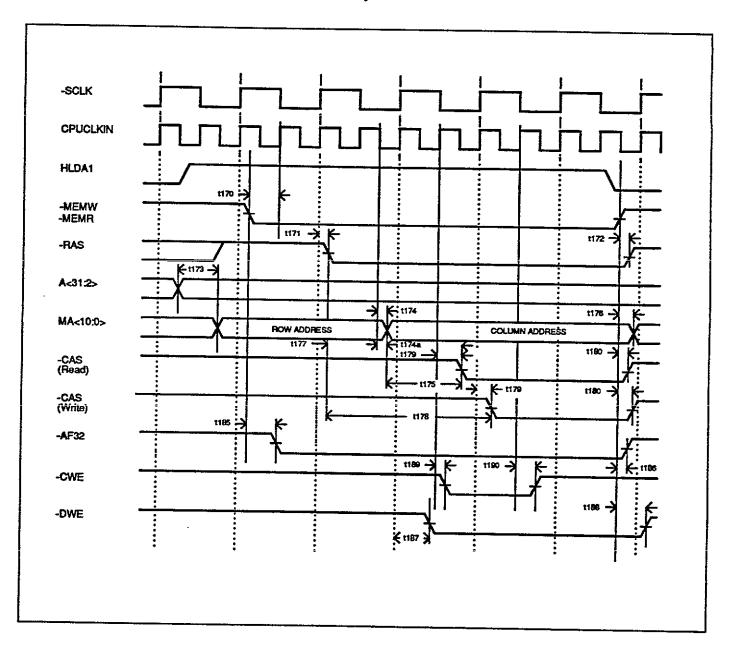

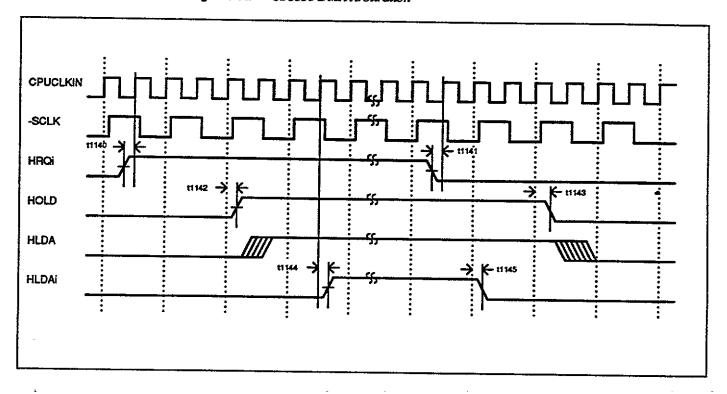

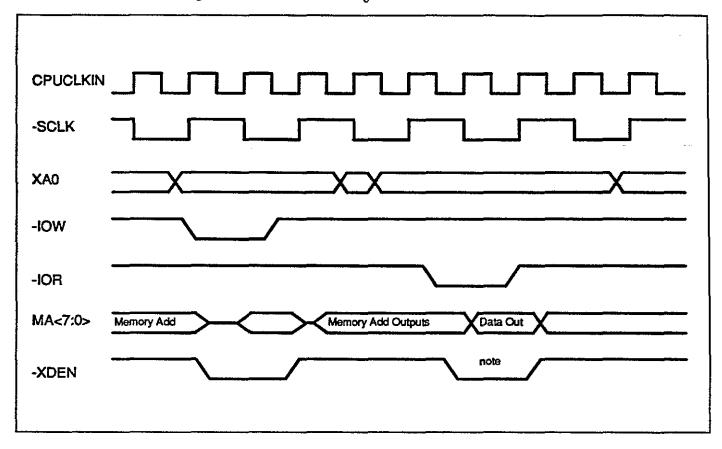

| Figure 1-6                 | DMA Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

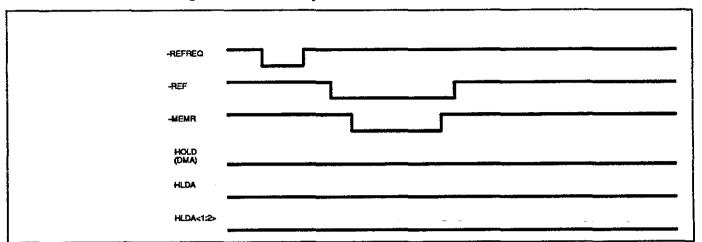

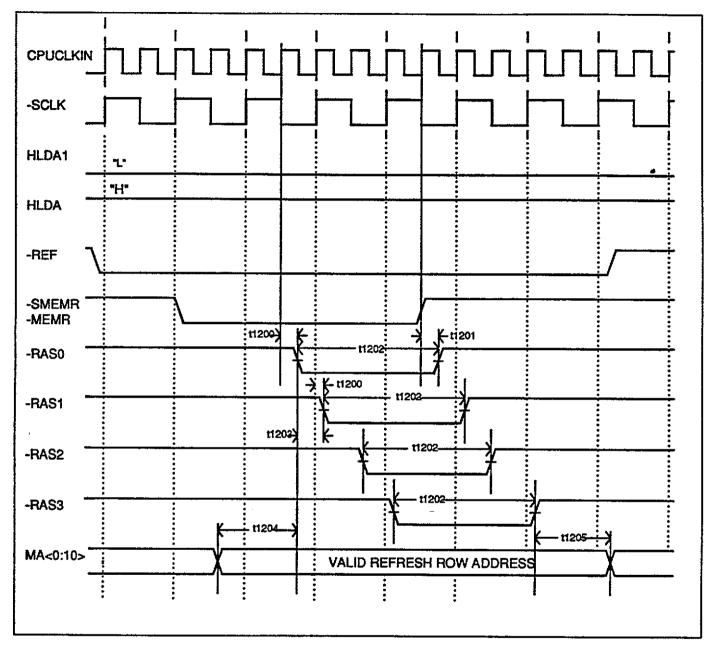

| Figure 1-7                 | Hidden Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

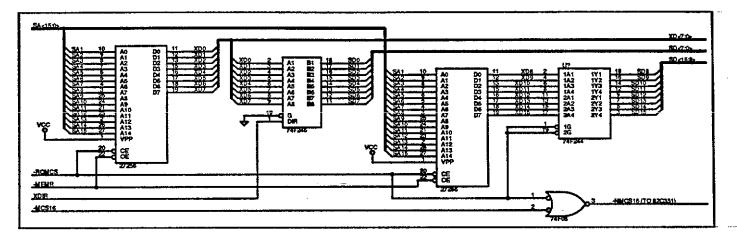

| Figure 1-8                 | Single EPROM Connection Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

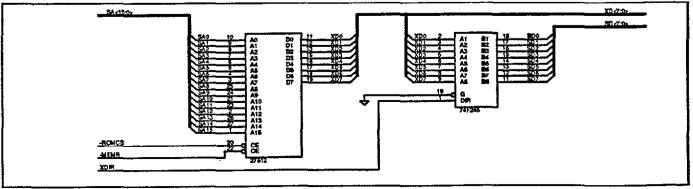

| Figure 1-9                 | Dual EPROM Connection Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

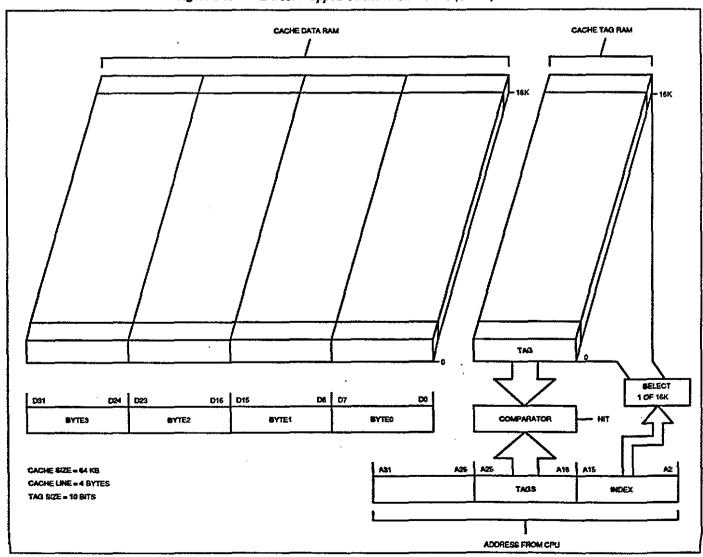

| Figure 1-10                | Direct Mapped Cache Architecture (64KB)29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

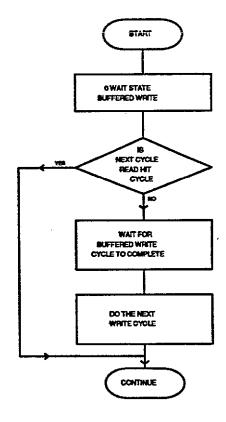

| Figure 1-11                | Buffered Write Algorithm 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

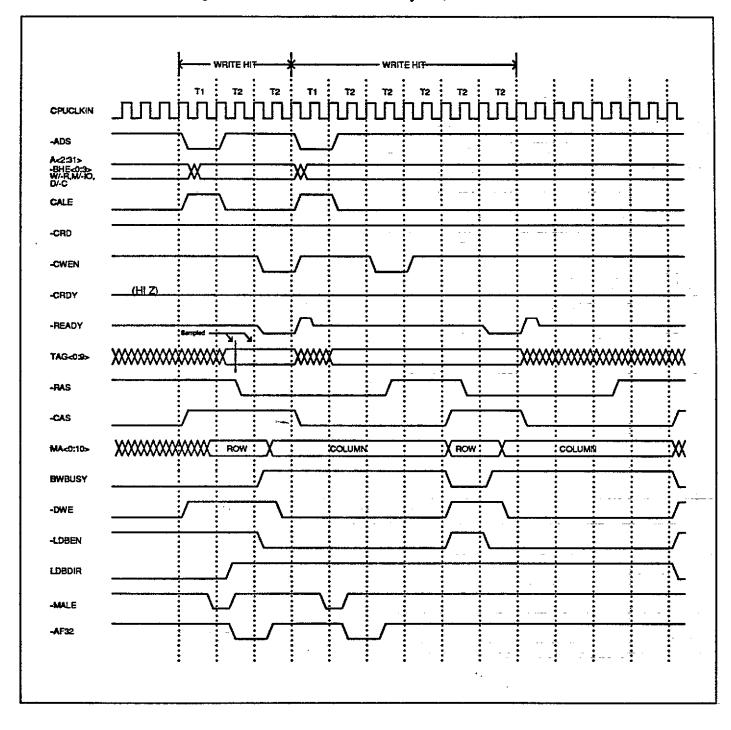

| Figure 1-12                | Back to Back Writes Early RAS, Four Wait States 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Section 3:                 | 351 Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Figure 3-1                 | 82C351 CPU/Cache/DRAM Controller Pin Diagram . 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                            | in table 1 and 1 a |  |

| Section 6:                 | 351 Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

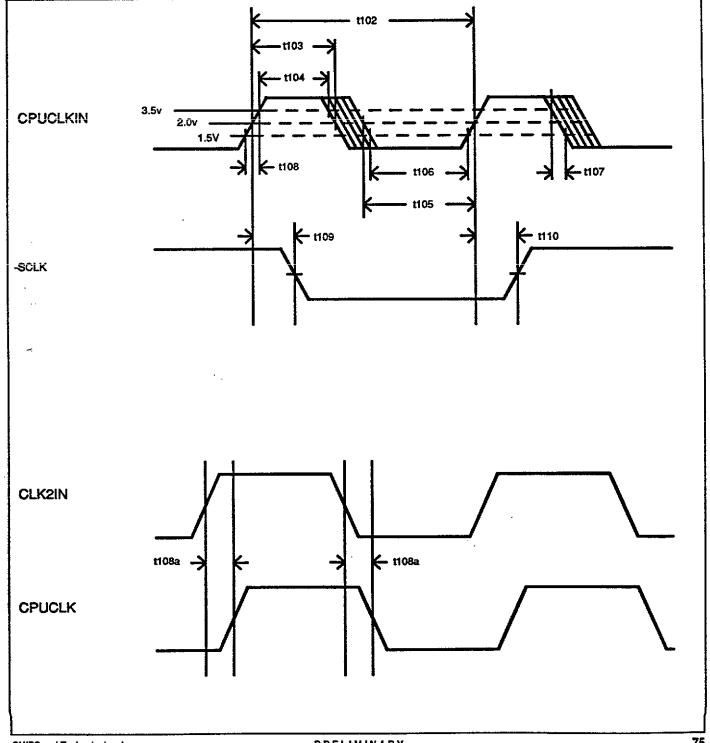

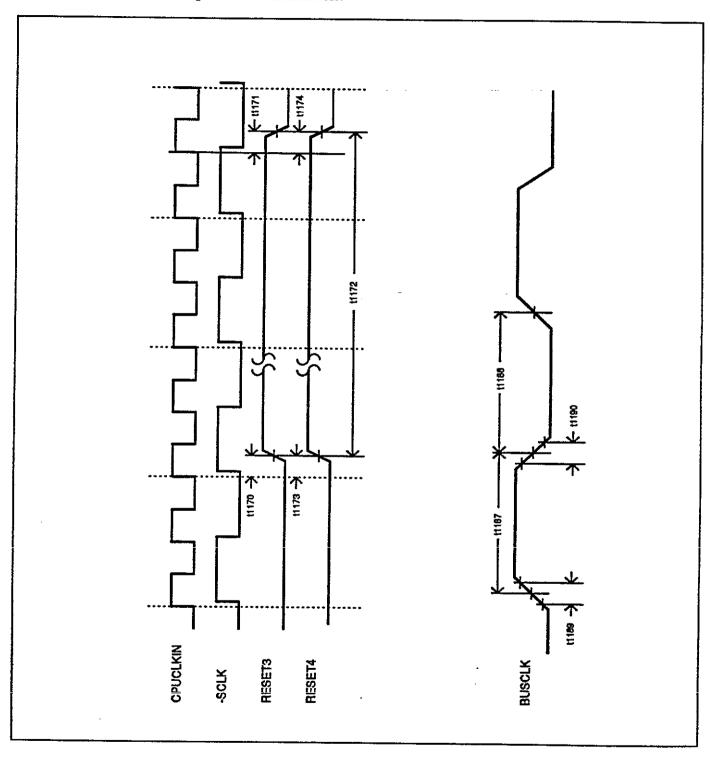

| Figure 6-1                 | 82C351 AC Timing Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

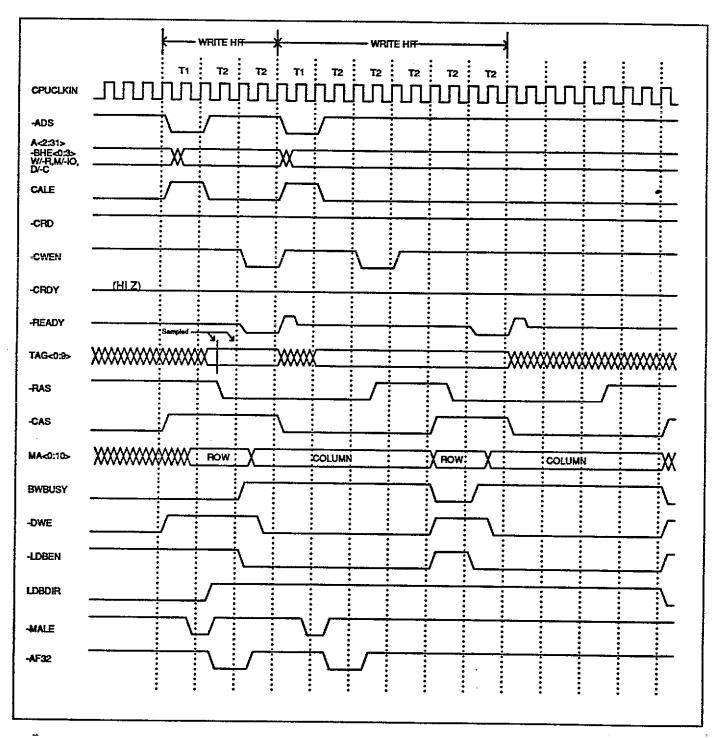

| Figure 6-2                 | Back to Back Write Early RAS, Four Wait States 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

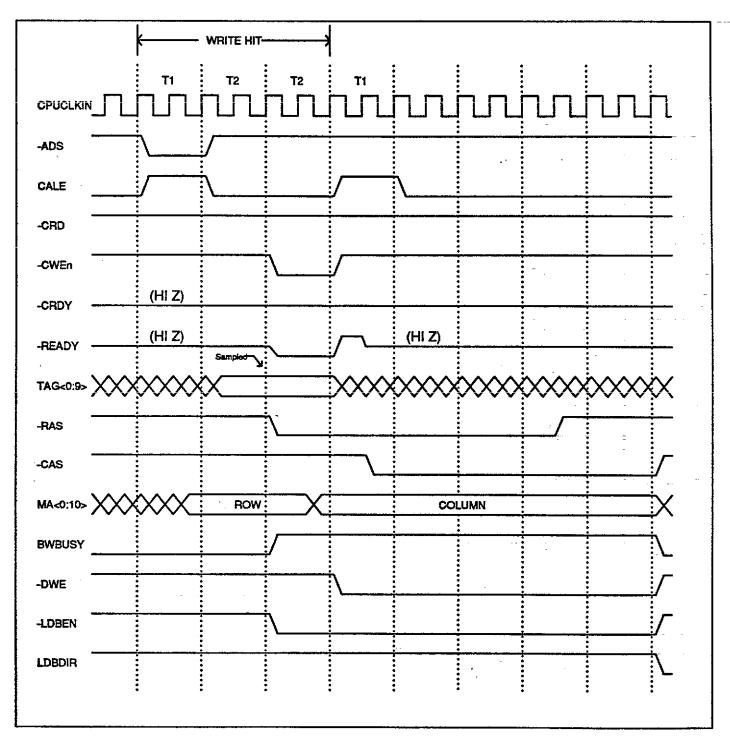

| Figure 6-3                 | 82C351 One Wait State Write Mode, Late RAS Mode, Five Wait State DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

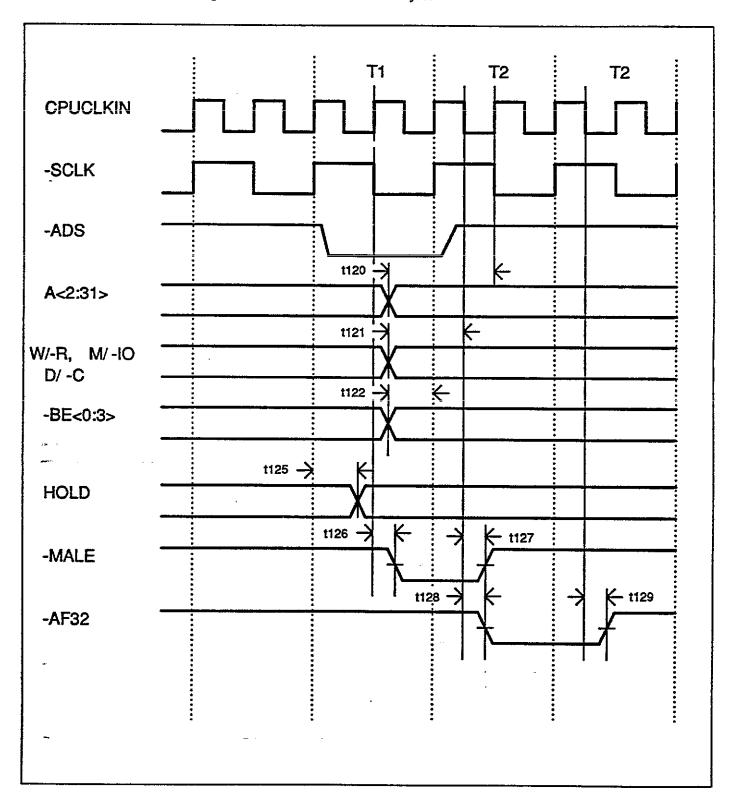

| Figure 6-4                 | 82C351 and 386DX Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

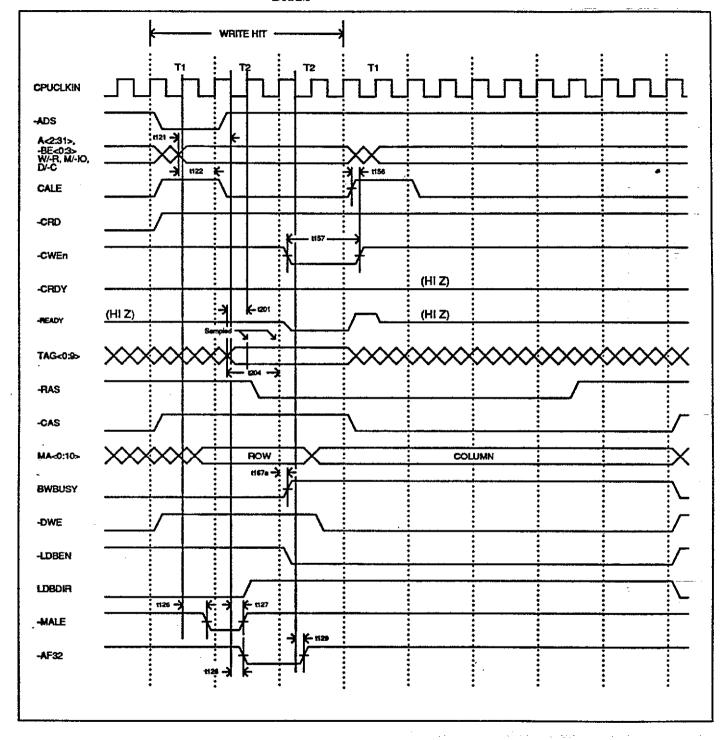

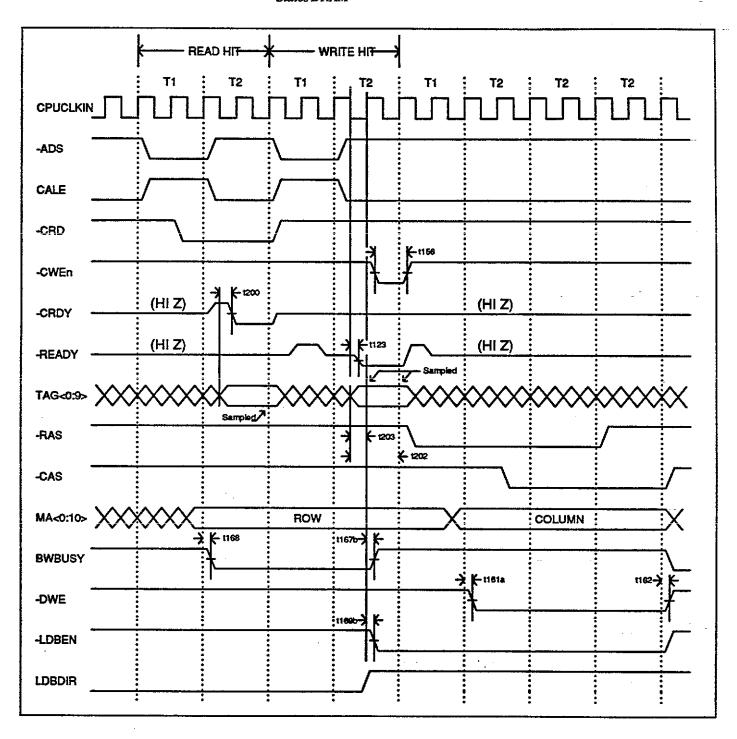

| Figure 6-5                 | 82C351 Write Hit, One Wait State Cache, Early RAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                            | Made Eine Weit Crotes DD AM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |